隨著微電子技術(shù)和計(jì)算機(jī)技術(shù)的飛速發(fā)展, 各種電子測量儀器在原理、功能、精度及自動(dòng)化水平等方面都發(fā)生了巨大的變化,特別是DSP技術(shù)誕生以后,電子測量技術(shù)更是邁進(jìn)了一個(gè)全新的時(shí)代。近年來,DSP逐漸成為各種電子器件的基礎(chǔ)器件,逐漸成為21世紀(jì)最具發(fā)展?jié)摿Φ某栃袠I(yè),甚至被譽(yù)為信息化數(shù)字化時(shí)代革命旗手。在電子測量技術(shù)中,頻率是最基本的參數(shù)之一,它與許多電參量和非電量的測量都有著十分密切的關(guān)系。例如,許多傳感器就是將一些非電量轉(zhuǎn)換成頻率來進(jìn)行測量的,因此頻率的測量就顯得更為重要。數(shù)字頻率計(jì)是用數(shù)字來顯示被測信號(hào)頻率的儀器,被測信號(hào)可以是正弦波、方波或其它周期性變化的信號(hào)。

數(shù)字頻率計(jì)廣泛采用了高速集成電路和大規(guī)模集成電路,使得儀器的體積更小、耗電更少、精度和可靠性更高。而傳統(tǒng)的頻率計(jì)測量誤差較大,范圍也較窄,因此逐漸被新型的數(shù)字頻率計(jì)所代替。基于DSP的等精度頻率計(jì)以其測量準(zhǔn)確、精度高、方便、價(jià)格便宜等優(yōu)勢將得到廣泛的應(yīng)用。

我們?cè)O(shè)計(jì)的簡易數(shù)字頻率計(jì)在未采用任何門控器件控制的情況下,在很寬的范圍內(nèi)實(shí)現(xiàn)了等精度頻率測量,0.5Hz~10MHz的范圍內(nèi)測量方波的最大相對(duì)誤差小于2e-6,測量正弦波的最大相對(duì)誤差小于3.5e-5;結(jié)果通過RS232通訊顯示在計(jì)算機(jī)上,可以很方便地監(jiān)測數(shù)據(jù)。

方案設(shè)計(jì)

總體介紹

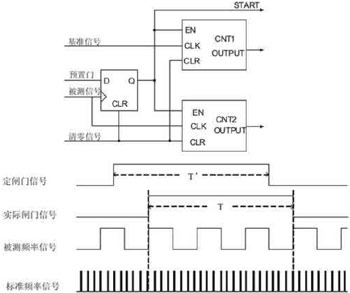

傳統(tǒng)的等精度測頻法使用門控器件產(chǎn)生門控信號(hào),從而實(shí)現(xiàn)實(shí)際門閘信號(hào)與被測信號(hào)同步,消除對(duì)被測信號(hào)計(jì)數(shù)產(chǎn)生的一個(gè)脈沖的誤差,其原理圖如圖1所示。

圖1 傳統(tǒng)的等精度測量原理

由硬件控制計(jì)數(shù)的門閘時(shí)間,當(dāng)預(yù)置們信號(hào)(即定閘門信號(hào))為高電平時(shí),基準(zhǔn)信號(hào)計(jì)數(shù)器CNT1和被測信號(hào)計(jì)數(shù)器CNT2并不啟動(dòng),而是等被測信號(hào)的上升沿來到時(shí)才同時(shí)開始計(jì)數(shù);當(dāng)預(yù)置們信號(hào)為低電平時(shí),兩個(gè)計(jì)數(shù)器并不馬上關(guān)閉,同樣要等到被測信號(hào)上升沿來到后再關(guān)閉;于是,實(shí)際閘門時(shí)間就是被測信號(hào)周期的整數(shù)倍,從而實(shí)現(xiàn)了閘門與被測信號(hào)的同步。但是,實(shí)際的門閘時(shí)間并不固定,與被測信號(hào)的頻率有關(guān)。此外,無論是采用計(jì)數(shù)器還是單片機(jī),在實(shí)現(xiàn)等精度測量時(shí)總是離不開門控器件。

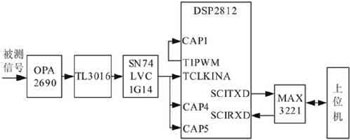

本設(shè)計(jì)基于DSP豐富的軟件資源,經(jīng)過判斷和處理,完成了對(duì)被測信號(hào)頻率的等精度測量。硬件上無需任何門控器件,簡化了電路。系統(tǒng)框圖如圖2所示,信號(hào)處理部分以TMS320F2812 DSP芯片作為控制和測量的核心;信號(hào)調(diào)理部分主要是完成對(duì)信號(hào)的放大、整形和限幅;標(biāo)準(zhǔn)頻率信號(hào)由30MHz有源晶振產(chǎn)生,作為高頻標(biāo)準(zhǔn)填充脈沖;通過DSP的SCI模塊與上位機(jī)實(shí)現(xiàn)通信,結(jié)果顯示在上位機(jī)上。

圖2 系統(tǒng)框圖

頻率/周期測量

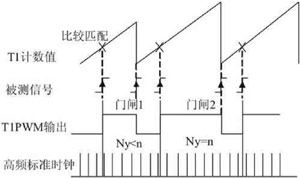

在對(duì)被測信號(hào)頻率和周期的測量中,等精度測量是基于DSP比較匹配時(shí)T1PWM引腳輸出電平的跳變作為門閘信號(hào)的開啟和關(guān)閉,由于比較匹配發(fā)生在被測信號(hào)的上升沿,從而實(shí)現(xiàn)了門閘時(shí)間與被測信號(hào)的同步。原理圖如圖3所示。

圖3 本等精度頻率測量原理

通用定時(shí)器T1時(shí)鐘輸入選擇外部定時(shí)器時(shí)鐘,此處用調(diào)理后的被測信號(hào)作為定時(shí)器T1的時(shí)鐘輸入,定時(shí)器T2時(shí)鐘輸入選擇內(nèi)部CPU時(shí)鐘,用來產(chǎn)生高頻標(biāo)準(zhǔn)填充脈沖。F2812片上EVA中通用定時(shí)器T1在發(fā)生比較匹配事件時(shí),其比較輸出引腳T1CMP輸出信號(hào)會(huì)自動(dòng)改變電平狀態(tài),產(chǎn)生PWM波。捕獲單元CAP1設(shè)置為上升沿捕獲,T1PWM輸出的PWM波上升沿被CAP1捕獲到,讀取此時(shí)定時(shí)器T2的計(jì)數(shù)值,同理在下一次比較匹配時(shí)再次讀取定時(shí)器T2的計(jì)數(shù)值。通過兩次T2CNT值的相減,即可獲得該門閘時(shí)間內(nèi)標(biāo)準(zhǔn)填充脈沖的個(gè)數(shù),然后求出被測信號(hào)頻率。

基于DSP比較匹配時(shí)T1PWM引腳輸出電平的跳變作為門閘信號(hào)的開啟和關(guān)閉,由于比較匹配發(fā)生在被測信號(hào)的上升沿,從而實(shí)現(xiàn)了門閘時(shí)間與被測信號(hào)的同步。兩個(gè)相鄰的比較匹配產(chǎn)生的PWM波的上升沿分別作為門閘信號(hào)的開啟和關(guān)閉信號(hào),其中被測信號(hào)的個(gè)數(shù)為整數(shù),并且是由我們自己任意設(shè)定的。定時(shí)器T2時(shí)鐘輸入選擇內(nèi)部CPU時(shí)鐘,用來產(chǎn)生標(biāo)準(zhǔn)填充脈沖。設(shè)定捕獲單元CAP1為上升沿捕獲,當(dāng)其捕獲到上升沿時(shí)讀取堆棧CAPFIFO內(nèi)的值,在下一次捕獲到時(shí)再讀堆棧內(nèi)的值,計(jì)算出標(biāo)準(zhǔn)填充脈沖的個(gè)數(shù)Ny,保證Ny的個(gè)數(shù)不小于一定的值,即可保證門閘時(shí)間大于一定的值。假設(shè)現(xiàn)在希望一個(gè)門閘時(shí)間內(nèi)高頻填充脈沖的總數(shù)不小于n,當(dāng)Ny>n時(shí),就增大定時(shí)器T1的定時(shí)周期,即增大定時(shí)器T1周期寄存器TIPR的值。存在公式T1PR+1=n/Ny,由于n/Ny不一定為整數(shù),假a

周期測量與頻率測量的基本原理完全相同,測出信號(hào)頻率,根據(jù)公T=1/f即可得出被測信號(hào)的周期。

誤差分析

定時(shí)器T1計(jì)數(shù)的啟停時(shí)間都是由該信號(hào)的上升沿觸發(fā)的,在一次測量時(shí)間內(nèi)對(duì)被測信號(hào)的計(jì)數(shù)無誤差;在此時(shí)間內(nèi)標(biāo)準(zhǔn)頻率脈沖的計(jì)數(shù)個(gè)數(shù)Ny,最多相差一個(gè)脈沖,故理論誤差為:

|d|≤1/Ny

顯然,測量精度僅僅與Ny有關(guān),只要Ny值足夠大,就能保證精度。

硬件設(shè)計(jì)

如圖4所示,將被測信號(hào)經(jīng)過高速運(yùn)放OPA2690進(jìn)行放大,在經(jīng)過高速比較器TL3016進(jìn)行整形,由于比較器在對(duì)低頻正弦波信號(hào)進(jìn)行整形時(shí),輸出波形的邊沿有比較嚴(yán)重的抖動(dòng),影響測量。解決辦法是對(duì)比較器加入正反饋,加速信號(hào)邊沿,同時(shí)形成滯環(huán),可有效消除抖動(dòng)。整形后的信號(hào)經(jīng)過高速施密特觸發(fā)SN74LVC1G14進(jìn)行限幅和進(jìn)一步整形。測量部分主要使用DSP2812芯片上定時(shí)器T1的時(shí)鐘輸入引腳TCLKINA、定時(shí)器T1的比較輸出引腳T1PWM和捕獲單元CAP1的輸入引腳CAP1,即可完成頻率測量。通訊部分選擇MAX3221作為RS-232電平轉(zhuǎn)換器件,通過9芯標(biāo)準(zhǔn)RS-232口與上位機(jī)進(jìn)行串行通信。主要使用了DSP的串行通信發(fā)送引腳SCIRXD和串行通信接收引腳SCITXD。

軟件設(shè)計(jì)

軟件設(shè)計(jì)部分主要包括以下四部分:

·初始化:對(duì)變量參數(shù)、系統(tǒng)時(shí)鐘、PIE、EV、Flash、GPIO等進(jìn)行配置。

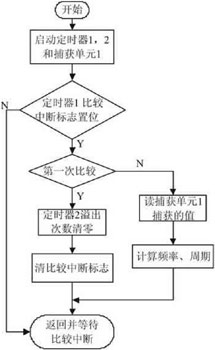

圖5為測頻率、周期軟件流程圖,圖6為定時(shí)器2的溢出中斷流程圖。

在該部分初始化時(shí),要進(jìn)行以下配置:通用定時(shí)器T1時(shí)鐘輸入為外部定時(shí)器時(shí)鐘,通用定時(shí)器T2時(shí)鐘輸入為內(nèi)部時(shí)鐘輸入,用來對(duì)標(biāo)準(zhǔn)脈沖進(jìn)行計(jì)數(shù),該標(biāo)準(zhǔn)脈沖由外部30MHz的有源晶振提供;捕獲單元1設(shè)置為上升沿捕獲,用來捕獲T1PWM引腳輸出PWM波的上升沿,在每次比較匹配時(shí)讀取定時(shí)器T2的計(jì)數(shù)值T2CNT,該值保存在CAP1FIFO內(nèi)。初始化時(shí)要將捕獲單元1的狀態(tài)寄存器中的FIFO堆棧狀態(tài)設(shè)置成空堆棧;將定時(shí)器T1的定時(shí)周期設(shè)置為4個(gè)被測信號(hào)的周期長度,通過測得的定時(shí)器T1的一個(gè)定時(shí)周期內(nèi)的標(biāo)準(zhǔn)脈沖的個(gè)數(shù),計(jì)算出被測信號(hào)頻率,然后對(duì)被測信號(hào)進(jìn)行分段,分別為低頻段(小于46.875Hz),中頻段(大于46.875Hz,小于2343.75KHz),以及高頻段(大于2343.75 KHz),其中分段的依據(jù)是定時(shí)器的計(jì)數(shù)飽和值為65536和計(jì)數(shù)個(gè)數(shù)應(yīng)大于等于1。若信號(hào)頻率為中高頻段則重新配置定時(shí)器T1,定時(shí)器T2的寄存器,來改變定時(shí)周期以及每個(gè)門閘時(shí)間內(nèi)的高頻填充脈沖的個(gè)數(shù)。在定時(shí)器T1的下一個(gè)定時(shí)周期內(nèi)計(jì)算出頻率和周期。另外,定時(shí)器T2的溢出次數(shù)要在第一次發(fā)生比較匹配時(shí)清零,而是否是第一次發(fā)生比較匹配則通過設(shè)置一個(gè)標(biāo)志來判斷。當(dāng)溢出次數(shù)清零后才開始記溢出次數(shù),直到第二次發(fā)生比較匹配。

下一步改進(jìn)意見

該方法的測量誤差主要來自硬件部分,整形電路的優(yōu)劣直接關(guān)系到測量精度的高低。所以我們下一步的工作就是改進(jìn)整形電路的整形效果和抗干擾性能,盡最大可能減小信號(hào)整形帶來的誤差。

由于DSP定時(shí)器在計(jì)數(shù)時(shí)存在計(jì)數(shù)飽和的情況,因此在實(shí)現(xiàn)該等精度測量時(shí)存在上限,即當(dāng)被測信號(hào)頻率高于高頻填充脈沖的頻率時(shí),該方法就不能實(shí)現(xiàn)等精度了。可以在該方案的基礎(chǔ)上進(jìn)行以下處理:選擇定時(shí)器T1定時(shí)周期內(nèi)被測信號(hào)的個(gè)數(shù)固定,可設(shè)置T1PR為65529,同時(shí)將定時(shí)器T2的時(shí)鐘修改為75MHz,這樣就能保證每個(gè)門閘時(shí)間內(nèi)高頻填充脈沖的個(gè)數(shù),從而在對(duì)高頻信號(hào)實(shí)現(xiàn)頻率和周期測量時(shí)保證了精度。

但選擇定時(shí)器T1時(shí)鐘輸入為外部時(shí)鐘時(shí)對(duì)被測信號(hào)的輸入范圍存在限制,如果要進(jìn)一步提高測量的信號(hào)的范圍,使得范圍達(dá)到上百兆或上G赫茲,可以考慮相位測量的方法,將被測信號(hào)設(shè)為360度,根據(jù)被測信號(hào)與標(biāo)準(zhǔn)信號(hào)之間的X度相位差,計(jì)算被測信號(hào)頻率。

圖4 硬件電路連接圖

·中斷模塊:SCI中斷和定時(shí)器T2、T3上溢中斷。

·數(shù)據(jù)處理模塊:分段+取算術(shù)平均值。

·輸出操作模塊:數(shù)據(jù)經(jīng)RS-232傳給上位機(jī)。

圖5 測頻率、周期流程圖

圖6 定時(shí)器T2溢出中斷流程圖