1 引言

生物電信號(hào)是由生物體發(fā)出的不穩(wěn)定的微弱電信號(hào),主要包括心電、肌電、腦電信號(hào),其特點(diǎn)表現(xiàn)為信號(hào)弱、干擾強(qiáng)、精度高。因此,在生物體的多參數(shù)測(cè)量中,高精度尤為重要,這對(duì)信號(hào)采集速率、實(shí)時(shí)性和準(zhǔn)確性等提出更高要求。

根據(jù)生物電信號(hào)特點(diǎn),介紹一種基于Ez-USB FX2接口的生物電信號(hào)數(shù)據(jù)采集系統(tǒng),它將傳統(tǒng)醫(yī)學(xué)儀器的優(yōu)點(diǎn)與計(jì)算機(jī)強(qiáng)大的數(shù)據(jù)存儲(chǔ)能力以及良好的人機(jī)界面相結(jié)合,符合醫(yī)學(xué)儀器數(shù)字化、模塊化、小型化的發(fā)展趨勢(shì),具有很好的應(yīng)用前景。

2 EZ-USB FX2接口簡(jiǎn)介

高速設(shè)備通常具有支持高速傳輸?shù)腢SB控制器以實(shí)現(xiàn)高速傳輸,選用內(nèi)置增強(qiáng)型微處理器8051、可動(dòng)態(tài)加載固件的USB2.0控制器EZ-USB FX2(CY7C68013),該器件相對(duì)于其他USB控制器,功能強(qiáng)大,開發(fā)難度較小且性價(jià)比較高。

2.1 基本特性

EZ-USB FX2功能強(qiáng)大,既負(fù)責(zé)USB事務(wù)處理,也兼具微處理器的控制功能,可用作USB外設(shè)主控器件。該器件集USB2.0收發(fā)器、串行接口引擎、增強(qiáng)型 8051、I2C總線以及通用可編程接口于一體,體積小巧,性價(jià)比高,廣泛應(yīng)用于存儲(chǔ)器、打印機(jī)、掃描儀等各種USB外設(shè)。

2.2 端點(diǎn)緩存

USB規(guī)范定義端點(diǎn)作為發(fā)送數(shù)據(jù)的起始點(diǎn)或接收數(shù)據(jù)的目的地址。EZ-USB FX2包含3個(gè)64 B的端點(diǎn)緩沖區(qū)和4 KB的可配置端點(diǎn)緩沖區(qū)。其中3個(gè)64 B的緩沖區(qū)分別用于EP0,EPlIN和EP1OUT,而4 KB的可配置緩沖區(qū)用于EP2,EP4,EP6和EP8。端點(diǎn)0默認(rèn)為控制端點(diǎn),支持OUT和IN雙向傳輸;端點(diǎn)1支持批量、中斷和同步傳輸;而端點(diǎn)2、 4、6和8則是高帶寬的數(shù)據(jù)傳輸端點(diǎn),可配置成不同方式以適應(yīng)不同帶寬要求。

2.3 GPIF接口

EZ-USB FX2系列器件提供3種可用接口模式:端口模式、從屬FIFO模式和GPIF主控制模式。端口模式下,所有I/O引腳都可作為8051的通用I/O接口;從屬FIFO模式下,外部邏輯或外部處理器直接與EZ-USB FX2的端點(diǎn)FIFO相連,外部設(shè)備作為控制器,像普通FIFO一樣對(duì)EZ-USB FX2中的端點(diǎn)數(shù)據(jù)緩沖區(qū)進(jìn)行讀寫;而GPIF模式是一種內(nèi)部主機(jī)控制模式,使用內(nèi)部集成的高效控制邏輯取代外部微控制器來(lái)控制Ez-USB FX2端點(diǎn)FIFO。在EZ-USB FX2內(nèi)部,GPIF內(nèi)核就是一個(gè)可編程的狀態(tài)機(jī)。

EZ-USB FX2使用4個(gè)用戶定義的波形描述符控制狀態(tài)機(jī).從而實(shí)現(xiàn)FIFO以及單字節(jié)數(shù)據(jù)的讀寫操作。每個(gè)GPIF波形描述符都由7段組成:S0~S6。執(zhí)行完 S0~S6的動(dòng)作后,進(jìn)入idle狀態(tài)(S7)即空閑狀態(tài),以準(zhǔn)備啟動(dòng)下一次GPIF動(dòng)作。每個(gè)state可定義為無(wú)判斷不轉(zhuǎn)移態(tài)(NDP)或判斷轉(zhuǎn)移態(tài) (DP)。當(dāng)某個(gè)state定義為NDP時(shí),這個(gè)state動(dòng)作的執(zhí)行只是簡(jiǎn)單延時(shí),用于確定產(chǎn)生指定電平的延續(xù)時(shí)間;當(dāng)定義為DP時(shí),它將根據(jù) RDY0~RDY5上的輸入信號(hào)狀態(tài),以及內(nèi)部FIFO的可編程標(biāo)志和內(nèi)部自定義的Ready標(biāo)志,將這些信號(hào)進(jìn)行邏輯“與”、“或”、“異或”運(yùn)算,并根據(jù)得到的邏輯結(jié)果在S0~S6中選擇一個(gè)即將執(zhí)行的state。執(zhí)行每個(gè)state時(shí),都可指定CTL0~CTL5輸出用戶指定的狀態(tài)。通過(guò)RDYx和 CTLx以及內(nèi)部一些標(biāo)志位的組合,即能完成各種復(fù)雜時(shí)序電路的控制。由于GPIF接口的配置靈活,使得FX2可方便地和其他邏輯微處理器(例如單片機(jī)、 DSP、CPLD和FPGA等)進(jìn)行數(shù)據(jù)的主動(dòng)讀寫,這樣便大大擴(kuò)展GPIF模式的使用范圍。GPIF模式下,8051可不參與數(shù)據(jù)傳輸,以突破高速、全速下的傳輸模式進(jìn)一步接近EZ-USB FX2的傳輸帶寬480 Mb/s。同時(shí)根據(jù)生物電信號(hào)的頻率特征,將每個(gè)通道最大采樣頻率設(shè)為100 kHz,在GPIF接口模式下完全能夠滿足系統(tǒng)要求。

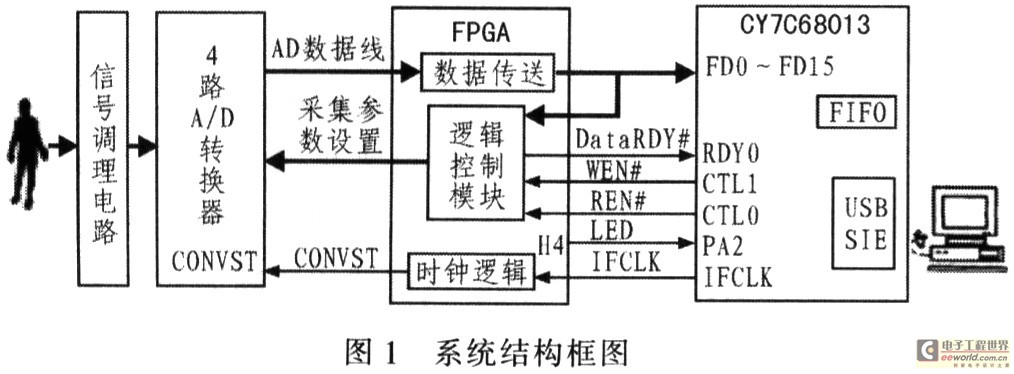

3 系統(tǒng)結(jié)構(gòu)

系統(tǒng)結(jié)構(gòu)框架如圖1所示。通過(guò)導(dǎo)聯(lián)由人體采集到的心電、腦電、肌電等信號(hào)調(diào)理電路后,由FPGA內(nèi)部邏輯控制A/D轉(zhuǎn)換對(duì)其采樣。將經(jīng)采樣并通過(guò)A/D轉(zhuǎn)換后的數(shù)據(jù)暫時(shí)緩存到EZ-USB FX2的內(nèi)部FIFO中,供PC機(jī)讀取。整個(gè)系統(tǒng)涉及A/D轉(zhuǎn)換及其通道選擇、信號(hào)放大、FPGA控制和EZ-USBFX2接口設(shè)計(jì),這里主要介紹EZ- USB FX2接口設(shè)計(jì),以及相應(yīng)固件程序的開發(fā)與GPIF波形設(shè)計(jì)。

4 器件資源分配

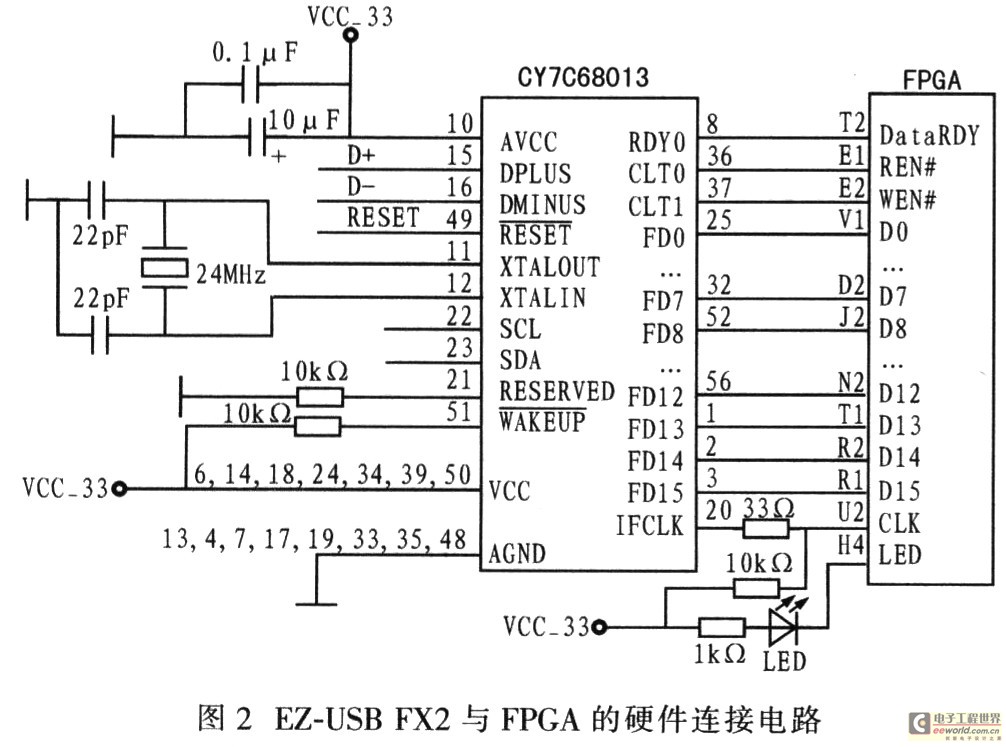

4.1 EZ-USB FX2與FPGA的硬件連接

EZ-USB FX2采用GPIF接口和FPGA相連,其硬件連接電路如圖2所示。EZ-USB FX2與FPGA連接的引腳分配如下:FD0~FD15為GPIF雙向數(shù)據(jù)線,負(fù)責(zé)讀寫數(shù)據(jù):CTL0、CTL1分別為讀(REN#)、寫(WEN#)使能信號(hào);RDY0為FPGA發(fā)出的數(shù)據(jù)準(zhǔn)備好信號(hào);PA2與FPGA的H4引腳連接,用于數(shù)據(jù)采集開始時(shí)點(diǎn)亮LED。

4.2 端點(diǎn)分配

系統(tǒng)中數(shù)據(jù)通道分為數(shù)據(jù)上傳通道以及配置和控制命令通道,根據(jù)設(shè)計(jì)需要,選擇其中兩個(gè)端點(diǎn)分別作為發(fā)送和接收端點(diǎn)。配置如下:EP2用于從USB向FPGA傳輸采集控制命令,4×512字節(jié)緩沖,傳輸類型為批量OUT傳輸方式;EP6用于從 FPGA向USB傳輸數(shù)據(jù)采集結(jié)果,4×512字節(jié)緩沖,傳輸類型為批量IN傳輸方式。EZ-USB FX2相當(dāng)于一個(gè)中轉(zhuǎn)站,一方面將FPGA發(fā)來(lái)的采集數(shù)據(jù)傳輸給主機(jī),另一方面將主機(jī)發(fā)送的數(shù)據(jù)采集參數(shù)傳輸至FPGA,便于控制A/D轉(zhuǎn)換。

5 固件程序設(shè)計(jì)

固件是設(shè)備運(yùn)行的核心,其主要功能是控制EZ-USB FX2處理驅(qū)動(dòng)程序請(qǐng)求(如請(qǐng)求設(shè)備描述符、請(qǐng)求或設(shè)置設(shè)備狀態(tài)及設(shè)備接口等USB2.0標(biāo)準(zhǔn)請(qǐng)求)、向FPGA發(fā)送采集參數(shù)、通過(guò)EZ-USB FX2緩存數(shù)據(jù)并實(shí)時(shí)上傳至PC等。

本系統(tǒng)中,即使使用外部邏輯和內(nèi)置通用可編程接口,在沒有CPU的干涉下能夠通過(guò)4個(gè)端點(diǎn)FIFO處理高速帶寬數(shù)據(jù),固件還需器件初始化、GPIF波形初始化、控制和監(jiān)測(cè)GPIF的動(dòng)作。

5.1 器件初始化

同件初始化函數(shù)為TD_Init(),主要負(fù)責(zé)對(duì)EZ-USB FX2的初始化,在同件開始運(yùn)行時(shí)調(diào)用該甬?dāng)?shù)。其初始化工作主要分為以下步驟:

(1)設(shè)置EZ-USB FX2的IFCLK輸出頻率,將時(shí)鐘頻率設(shè)置為內(nèi)部時(shí)鐘48 MHz;

(2)設(shè)置EZ-USB FX2的EP2為BULK、OUT傳輸方式,EP6為BULK、IN傳輸方式,均為4倍緩沖;

(3)復(fù)位EP2 FIFO并設(shè)置為Auto OUT模式,復(fù)位EP6FIFO并設(shè)置為Auto IN模式;

(4)調(diào)用GpifInit()函數(shù),初始化GPIF所需的寄存器;對(duì)EP2OUT、GPIF使用EF標(biāo)志,對(duì)EP6IN,GPIF使用FF標(biāo)志;

(5)初始化PA2為輸出引腳并置為低電平,高電平時(shí)點(diǎn)亮LED。

5.2 GPIF波形設(shè)計(jì)

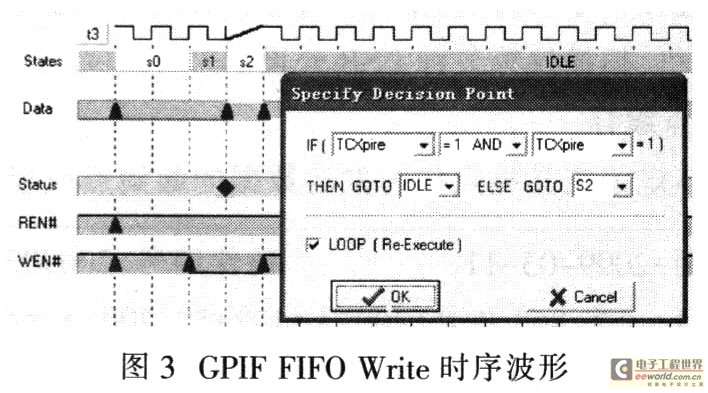

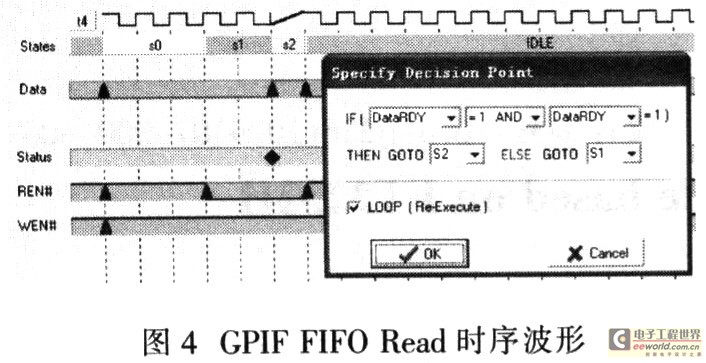

EZ-USB FX2固件程序可指定某個(gè)波形為4個(gè)端點(diǎn)中的任意一個(gè)工作,GPIF將在接口產(chǎn)生使能信號(hào)和握手信號(hào),將數(shù)據(jù)送入或送出端點(diǎn)FIFO。在本系統(tǒng)中,對(duì) FPGA寫命令時(shí)則通過(guò)FIFO Write實(shí)現(xiàn);讀取所采集到的數(shù)據(jù)時(shí),則通過(guò)FI-FO Read實(shí)現(xiàn)。波形設(shè)計(jì)如下:

(1)圖3為FIFO Write時(shí)序波形,用于向FPGA發(fā)送采集控制參數(shù)。S0為非活動(dòng)狀態(tài),當(dāng)WEN#置低時(shí)跳入S1狀態(tài),S2設(shè)為Next FIFO Data,依次將數(shù)據(jù)寫入FPGA的寄存器中。

(2)圖4為FIFO Read時(shí)序波形,它描述了采集數(shù)據(jù)的讀傳輸,S0為非活動(dòng)狀態(tài),S1為讀操作的引導(dǎo)狀態(tài)并將REN#置低。當(dāng)接收到FPGA發(fā)送的DataRDY=1 后,跳入S2。將S2設(shè)為FlowState,邏輯控制數(shù)據(jù)從FPGA中讀出并操作REN#的狀態(tài),即當(dāng)Tcxpire=1時(shí),將REN#置高,跳入 IDIE狀態(tài)。在FlowState狀態(tài)下,WEN#置高,寫使能關(guān)閉。

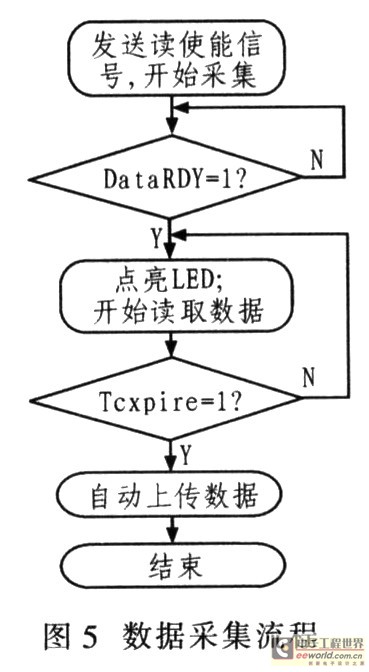

5.3 數(shù)據(jù)采集流程

程序開始,主函數(shù)調(diào)用TD_Init()和Gpiflnit()函數(shù),初始化寄存器,并通過(guò)2個(gè)自動(dòng)指針寄存器AUTOPTR1和AU-TOPTR2,把生成的GPIF波形程序調(diào)入器件的RAM,然后狀態(tài)機(jī)開始運(yùn)行,產(chǎn)生所設(shè)計(jì)的控制波形。采集參數(shù)下傳后,F(xiàn)PGA解析參數(shù),延時(shí),EZ-USB FX2向FPGA發(fā)送讀使能信號(hào),開始采集數(shù)據(jù),數(shù)據(jù)采集程序流程如圖5所示。如果FP-GA返回DataRDY=1,在TD_Poll()函數(shù)中執(zhí)行讀取數(shù)據(jù)傳輸程序。完成該過(guò)程后,程序根據(jù)主機(jī)請(qǐng)求,開始自動(dòng)上傳數(shù)據(jù)。

6 結(jié)束語(yǔ)

基于FPGA控制電路、EZ-USB FX2高速傳輸?shù)臄?shù)據(jù)采集系統(tǒng),可同時(shí)采集16位生物電信號(hào);EZ-USB FX2采用GPIF接口模式,8051可不參與數(shù)據(jù)傳輸,以突破高速、全速下的傳輸模式,解決了外圍設(shè)備和EZ-USB FX2接口之間存在的傳輸瓶頸問(wèn)題:同時(shí)A/D轉(zhuǎn)換脫離了EZ-USB FX2,而由FPGA完全控制,避免了直接上傳時(shí)的數(shù)據(jù)丟失。該系統(tǒng)設(shè)計(jì)具有結(jié)構(gòu)簡(jiǎn)單、數(shù)據(jù)不丟失且傳輸速率高等優(yōu)點(diǎn),因此在生物電信號(hào)數(shù)據(jù)采集中具有良好的實(shí)用價(jià)值和應(yīng)用前景。