中心議題:

解決方案:

- 檢測電路設計

- 偏置電路設計

- 延時電路,、電平轉換電路及待機設計

1 引言

鋰電池產(chǎn)品在充放電過程中的過充電,、過放電、放電過電流及其它異常狀態(tài)(例如負載短路),,將會導致內部發(fā)熱,,可能引起電池或其它器件的損害,嚴重影響到電池使用的安全性,。因此,,鋰電池產(chǎn)品保護電路的設計應用必不可少,。本文基于標準CMOS工藝,設計了一種全功能電池保護電路,。通過過放電檢測輸出端,、過充電檢測輸出端的CMOS輸出電平控制外接的兩個N溝道場效應開關晶體管的關斷,從而達到對電池實施保護的目的,。具有高檢測電壓精度,、低功耗、可靠性高等優(yōu)點,,可廣泛用于移動電話,、筆記本電腦、PDA,、MP3等產(chǎn)品中,。

2 電池保護電路原理分析

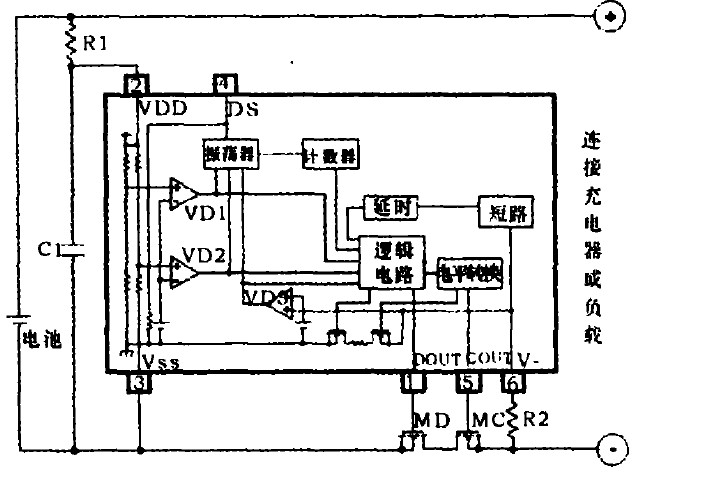

本論文所設計的電池保護電路應用示意圖如圖1所示。實線框內為電池保護電路的系統(tǒng)結構圖,,框外為外圍器件連接示意圖,。

圖1中,DOUT為過放電檢測的CMOS輸出,,COUT為過充電檢測的CMOS輸出,,VDD為電池電壓輸入,VSS為芯片接地引腳,,DS為響應延遲時間縮短控制輸入端,,V-為放電過流檢測端。

在充電時,,若電池電壓高于過充電檢測電壓并保持相應的延遲時間,,COUT端由高電位變?yōu)榈碗娢唬潆娍刂芃OS管MC關斷,,芯片進入過充電保護狀態(tài),,停止充電。

在放電時,,若電池電壓低于過放電檢測電壓并保持相應的延遲時間,,DOUT端由高電位變?yōu)榈碗娢唬烹娍刂芃OS管MD關斷,,芯片進入過放電保護模式,,停止放電。

圖1 鋰離子/鋰聚合物電池保護電路芯片應用電路圖以及內部系統(tǒng)結構框圖

放電時,,芯片同時監(jiān)控V-端電壓,。當因電流過大引起V-端電壓高于放電過電流檢測電壓,而低于短路檢測電壓時,,芯片進入放電過電流保護狀態(tài),;當V-端電壓高于短路檢測電壓時,,芯片進入短路保護狀態(tài)。此時,,DOUT端輸出由高電位變?yōu)榈碗娢?,關斷MD防止電路中通過強電流。

圖1中,,R1和C1起到對外接充電器或與其并聯(lián)的二次電池的電壓波動進行平滑濾波抑制的作用,。而電阻R1、R2為當對電池反向充電或充電器充電電壓超過芯片絕對極限額定充電電壓值時的限流電阻,。

該系統(tǒng)中主要包括過充電檢測電路(VD1),、過放電檢測電路(VD2)、放電過電流檢測電路(VD3)和短路檢測電路,、電平轉換電路,、基準電路、振蕩電路以及偏置電路等,。

3 電路設計

由于保護電路依靠電池來供應其電源電壓,,為了不影響電池的待機時間,應盡可能設計低電源電壓,、低功耗的電池保護電路,。

3.1 檢測電路設計

由于檢測電路VD1、VD2,、VD3原理類似,在此以過放電檢測電路(VD2)設計為例進行分析,。為了滿足整個芯片功耗小的要求,,可設計該電路處于亞閾值工作狀態(tài),有效降低其工作電流及電壓,。

圖2 過放電檢測電路

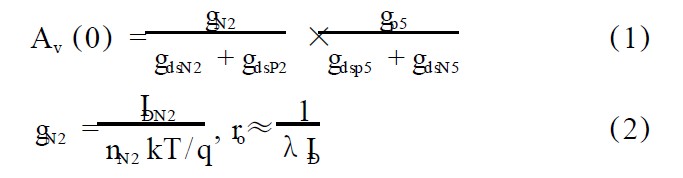

過放電檢測電路(VD2)可利用一個二級開環(huán)比較器來實現(xiàn),,如圖2所示。在設計中應采用差分輸入并盡可能地提高增益,,以滿足精度要求,。該電路中,第一級是由MN1,MN2,MP1,MP2,MN3,MN4組成的差分放大器,。第二級是由MP5,MN5組成的單級放大器,。前級放大器放大輸入的差模信號,后一級將前級的輸出進一步放大,,以達到數(shù)字信號的輸出電平,。該比較器電路的直流增益為:

同時,還必須考慮諸如傳輸時延,、輸出電壓擺率,、輸入共模范圍等性能,。鑒于大的偏置電流和小的電容可使擺率得到改善,縮短延遲時間,,因此可通過加大偏置電流而達到高速,。但是,一般而言,,高速比較器也會有較高的功耗,。因此在設計時必須在功耗與速度之間進行折衷。相對于處于飽和區(qū)的比較器而言,,工作在亞閾值區(qū)的比較器的延遲時間顯著增長,,這主要是由于工作在亞閾值區(qū)的偏置電流較小,電容充放電需要更長的時間,,從而使得延遲時間變長,。該比較器具有與差動放大器類似的ICMR(輸入共模范圍),其最低輸入電壓應小于過放電檢測基準電壓,。

![]()

3.2 偏置電路設計

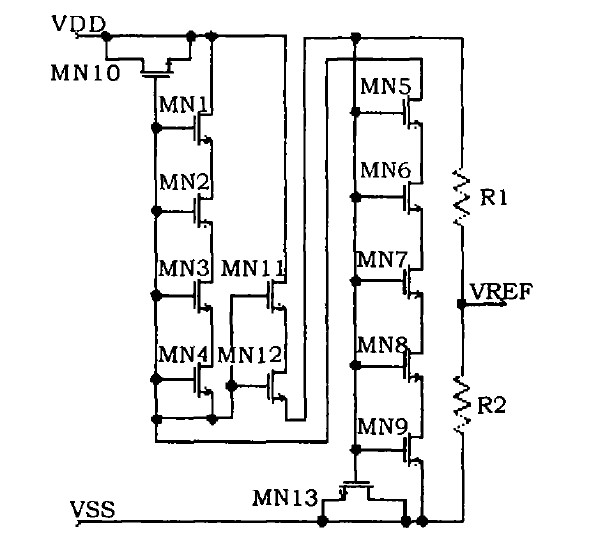

偏置電路用于為檢測電路提供穩(wěn)定,、高精度的基準電壓,從而檢測過充電,、過放電,、放電過電流等狀態(tài)。本論文中設計了一種低功耗基準電路,,示于圖3,。

圖3 低功耗基準電路

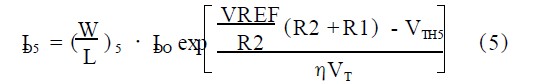

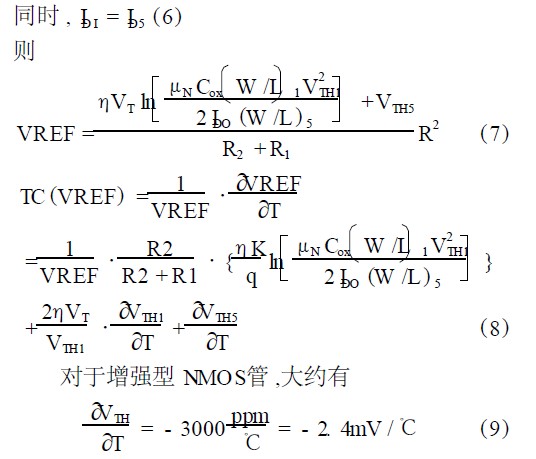

基于耗盡型NMOS管閾值電壓為負值,在VGS=0時也處于工作狀態(tài),,該特性可有效降低其工作電壓及功耗,。因而,該基準電路中利用串聯(lián)的耗盡型NMOS管MN1-MN4,、串聯(lián)的增強型NMOS管MN5-MN9,、MN11-MN12和電阻R1、R2構成基于VGS的基準電壓電路,,該基準電路的輸出為檢測比較器反相端的基準電壓信號VREF,。

由于本電路中耗盡管閾值電壓為負值,且柵源電壓恒為0,故耗盡型管始終工作在飽和區(qū),。且其電流值恒定為:

同時為滿足該電路低功耗的要求,,應盡可能使電路中增強性管工作在亞閾值區(qū)。如圖3所示,,基于襯偏效應和源極電位的升高,,MN5管工作于亞閾值區(qū)。

即對于增強型NMOS管,VTH隨溫度升高而下降,,而對于耗盡型NMOS管,,VTH為負值,其絕對值隨溫度升高而上升,。由此推得,,當選取合適的參數(shù)時,本電路的溫度漂移可以控制在較小范圍內,。

3.3 其余部分設計

3.3.1 延時電路

為了防止干擾信號使保護電路產(chǎn)生誤操作,,系統(tǒng)針對不同的異常狀態(tài),設置了相應的延遲時間,。

該延遲時間是由振蕩電路以及計數(shù)器共同實現(xiàn),。

振蕩電路采用三級環(huán)形振蕩器結構,其每一級由一個反相器和一個電容構成,,該振蕩電路正常工作時,,向計數(shù)器輸出振蕩方波,不工作時輸出高電平,。

計數(shù)器由D觸發(fā)器級聯(lián)而成,。

3.3.2 電平轉換電路

同時,為了保證充電控制管MC在過充電狀態(tài)下有效關斷,,利用電平轉換電路使輸出COUT端為邏輯電路輸出信號的四級反相,,從而使COUT端低電平由VSS降至V-。

3.3.3 待機狀態(tài)

芯片中的部分電路設有使能端,,為邏輯電路輸出,。當保護電路進入過放電保護狀態(tài)后,該使能端由高電位變?yōu)榈碗娢?,關閉相應電路,,芯片進入待機狀態(tài),從而大大降低消耗電流,,減小功耗,。

圖4 過充電保護及復原波形圖

4 仿真結果及分析

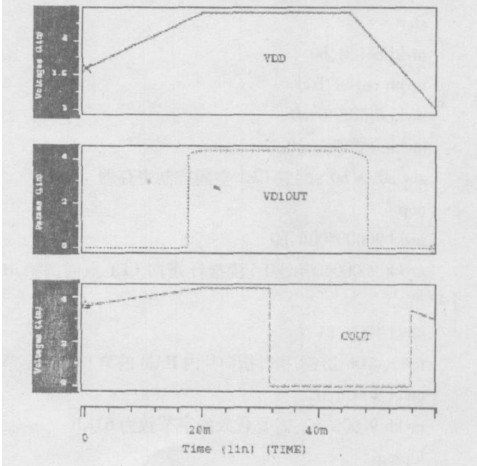

本芯片采用0.6μm的標準CMOS工藝,。使用49級HSPICE模型進行仿真,。圖4為過充電保護及復原波形圖,圖5為過放電保護及復原波形圖,。

正常工作時,,該芯片的消耗電流為2.11μA,而處于待機狀態(tài)時的消耗電流僅為0.03μA。過充電過放電的電壓檢測精度約為25mV,。

圖5 過放電保護及復原波形圖

5 結論

本文基于全功能電池保護電路原理,,針對過放電、過充電、放電過電流,、負載短路等異常狀態(tài)設置了相應的保護機制,。為滿足低功耗要求,設計了基于亞閾值區(qū)的基準電路及比較器,,并設置了待機狀態(tài),。經(jīng)仿真驗證,本芯片滿足功能,、性能設計要求,,已經(jīng)流片成功。