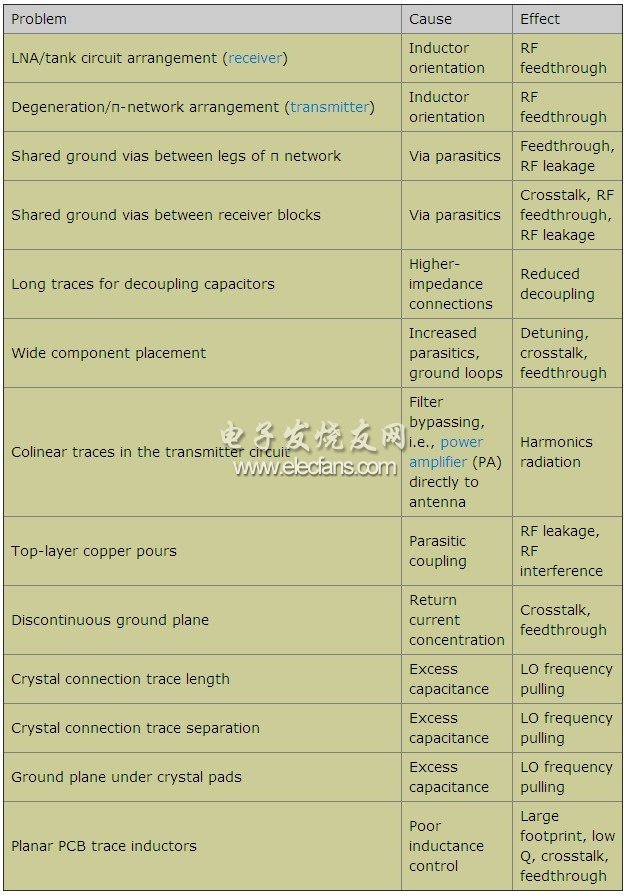

本文羅列了各種不同的設(shè)計(jì)疏忽,,探討了每種失誤導(dǎo)致電路故障的原因,,并給出了如何避免這些設(shè)計(jì)缺陷的建議。本文以FR-4電介質(zhì),、厚度0.0625in的雙層PCB為例,,電路板底層接地。工作頻率介于315MHz到915MHz之間的不同頻段,,Tx和Rx功率介于-120dBm至+13dBm之間,。表1列出了一些可能出現(xiàn)的PCB布局問題,、原因及其影響。

其中大多數(shù)問題源于少數(shù)幾個(gè)常見原因,,我們將對(duì)此逐一討論,。

電感方向

當(dāng)兩個(gè)電感(甚至是兩條PCB走線)彼此靠近時(shí),將會(huì)產(chǎn)生互感,。第一個(gè)電路中的電流所產(chǎn)生的磁場(chǎng)會(huì)對(duì)第二個(gè)電路中的電流產(chǎn)生激勵(lì)(圖1),。這一過程與變壓器初級(jí)、次級(jí)線圈之間的相互影響類似,。當(dāng)兩個(gè)電流通過磁場(chǎng)相互作用時(shí),,所產(chǎn)生的電壓由互感LM決定:

![]()

式中,YB是向電路B注入的誤差電壓,,IA是在電路A作用的電流1,。LM對(duì)電路間距、電感環(huán)路面積(即磁通量)以及環(huán)路方向非常敏感,。因此,,緊湊的電路布局和降低耦合之間的最佳平衡是正確排列所有電感的方向。

圖1.由磁力線可以看出互感與電感排列方向有關(guān)

對(duì)電路B的方向進(jìn)行調(diào)整,,使其電流環(huán)路平行于電路A的磁力線,。為達(dá)到這一目的,盡量使電感互相垂直,,請(qǐng)參考低功率FSK超外差接收機(jī)評(píng)估(EV)板(MAX7042EVKIT)的電路布局(圖2),。該電路板上的三個(gè)電感(L3、L1和L2)距離非常近,,將其方向排列為0°,、45°和90°,有助于降低彼此之間的互感,。

圖2.圖中所示為兩種不同的PCB布局,,其中一種布局的元件排列方向不合理(L1和L3),另一種的方向排列則更為合適,。

綜上所述,,應(yīng)遵循以下原則:

電感間距應(yīng)盡可能遠(yuǎn)。

電感排列方向成直角,,使電感之間的串?dāng)_降至最小,。

引線耦合

如同電感排列方向會(huì)影響磁場(chǎng)耦合一樣,如果引線彼此過于靠近,,也會(huì)影響耦合,。這種布局問題也會(huì)產(chǎn)生所謂的互感。RF電路最關(guān)心問題之一即為系統(tǒng)敏感部件的走線,例如輸入匹配網(wǎng)絡(luò),、接收器的諧振槽路,、發(fā)送器的天線匹配網(wǎng)絡(luò)等。

返回電流通路須盡可能靠近主電流通道,,將輻射磁場(chǎng)降至最小,。這種布局有助于減小電流環(huán)路面積。返回電流的理想低阻通路通常是引線下方的接地區(qū)域—將環(huán)路面積有效限制在電介質(zhì)厚度乘以引線長(zhǎng)度的區(qū)域,。但是,,如果接地區(qū)域被分割開,則會(huì)增大環(huán)路面積(圖3),。對(duì)于穿過分割區(qū)域的引線,,返回電流將被強(qiáng)制通過高阻通路,大大提高了電流環(huán)路面積,。這種布局還使電路引線更容易受互感的影響,。

圖3.完整的大面積接地有助于改善系統(tǒng)性能

對(duì)于一個(gè)實(shí)際電感,引線方向?qū)Υ艌?chǎng)耦合的影響也很大,。如果敏感電路的引線必須彼此靠近,,最好將引線方向垂直排列,以降低耦合(圖4),。如果無法做到垂直排列,,則可考慮使用保護(hù)線。關(guān)于保護(hù)線的設(shè)計(jì),,請(qǐng)參考以下接地與填充處理部分,。

圖4.類似于圖1,表示可能存在的磁力線耦合,。

綜上所述,,布板時(shí)應(yīng)遵循以下原則:

引線下方應(yīng)保證完整接地。

敏感引線應(yīng)垂直排列,。

如果引線必須平行排列,,須確保足夠的間距或采用保護(hù)線。

接地過孔

RF電路布局的主要問題通常是電路的特征阻抗不理想,,包括電路元件及其互聯(lián),。引線覆銅層較薄,則等效于電感線,,并與鄰近的其它引線形成分布電容,。引線穿過過孔時(shí),也會(huì)表現(xiàn)出電感和電容特性,。

過孔電容主要源于過孔焊盤側(cè)的覆銅與地層覆銅之間構(gòu)成的電容,它們之間由一個(gè)相當(dāng)小的圓環(huán)隔開。另外一個(gè)影響源于金屬過孔本身的圓柱,。寄生電容的影響一般較小,,通常只會(huì)造成高速數(shù)字信號(hào)的邊沿變差(本文不對(duì)此加以討論)。

過孔的最大影響是相應(yīng)的互聯(lián)方式所引起的寄生電感,。因?yàn)镽FPCB設(shè)計(jì)中,,大多數(shù)金屬過孔尺寸與集總元件的尺寸相同,可利用簡(jiǎn)單的公式估算電路過孔的影響(圖5):

![]()

式中,,LVIA為過孔的集總電感;h為過孔高度,,單位為英寸;d為過孔直徑,單位為英寸2,。

圖5.PCB橫截面用于估算寄生影響的過孔結(jié)構(gòu)

寄生電感往往對(duì)旁路電容的連接影響很大,。理想的旁路電容在電源層與地層之間提供高頻短路,但是,,非理想過孔則會(huì)影響地層和電源層之間的低感通路,。典型的PCB過孔(d=10mil、h=62.5mil)大約等效于一個(gè)1.34nH電感,。給定ISM-RF產(chǎn)品的特定工作頻率,,過孔會(huì)對(duì)敏感電路(例如,諧振槽路,、濾波器以及匹配網(wǎng)絡(luò)等)造成不良影響,。

如果敏感電路共用過孔,例如π型網(wǎng)絡(luò)的兩個(gè)臂,,則會(huì)產(chǎn)生其它問題,。例如,放置一個(gè)等效于集總電感的理想過孔,,等效原理圖則與原電路設(shè)計(jì)有很大區(qū)別(圖6),。與共用電流通路的串?dāng)_一樣3,導(dǎo)致互感增大,,加大串?dāng)_和饋通,。

圖6.理想架構(gòu)與非理想架構(gòu)比較,電路中存在潛在的“信號(hào)通路”,。

綜上所述,,電路布局需要遵循以下原則:

確保對(duì)敏感區(qū)域的過孔電感建模。

濾波器或匹配網(wǎng)絡(luò)采用獨(dú)立過孔,。

注意,,較薄的PCB覆銅會(huì)降低過孔寄生電感的影響。

引線長(zhǎng)度

Maxim ISM-RF產(chǎn)品的數(shù)據(jù)資料往往建議使用盡可能短的高頻輸入,、輸出引線,,從而將損耗和輻射降至最小。另一方面,這種損耗通常是由于非理想寄生參數(shù)引起的,,所以寄生電感和電容都會(huì)影響電路布局,,使用盡可能短的引線有助于降低寄生參數(shù)。通常情況下,,10mil寬,、距離地層0.0625in的PCB引線,如果采用的是FR4電路板,,則產(chǎn)生大約19nH/in的電感和大約1pF/in的分布電容,。對(duì)于具有20nH電感、3pF電容的LAN/混頻器電路,,電路,、元器件布局非常緊湊時(shí),會(huì)對(duì)有效元件值造成很大影響,。

“InstituteforPrintedCircuits”中的IPC-D-317A4提供了一個(gè)行業(yè)標(biāo)準(zhǔn)方程,,用于估算微帶線PCB的各種阻抗參數(shù)。該文件在2003年被IPC-2251取代5,,后者為各種PCB引線提供更準(zhǔn)確的計(jì)算方法,。可以通過各種渠道獲得在線計(jì)算器,,其中大多數(shù)都基于IPC-2251提供的方程式,。密蘇里理工大學(xué)的電磁兼容性實(shí)驗(yàn)室提供了一個(gè)非常實(shí)用的PCB引線阻抗計(jì)算方法6。

公認(rèn)的計(jì)算微帶線阻抗的標(biāo)準(zhǔn)是:

![]()

式中,,εr為電介質(zhì)的介電常數(shù),,h為引線距離地層的高度,w為引線寬度,,t為引線厚度(圖7),。w/h介于0.1至2.0、εr介于1至15之間時(shí),,該公式的計(jì)算結(jié)果相當(dāng)準(zhǔn)確7,。

圖7.該圖為PCB橫截面(與圖5類似),表示用于計(jì)算微帶線阻抗的結(jié)構(gòu),。

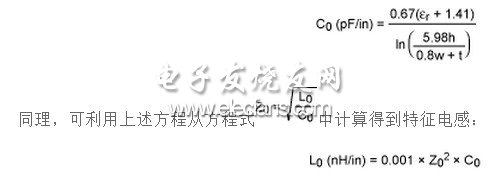

為評(píng)估引線長(zhǎng)度的影響,,確定引線寄生參數(shù)對(duì)理想電路的去諧效應(yīng)更實(shí)用。本例中,,我們討論雜散電容和電感,。用于微帶線的特征電容標(biāo)準(zhǔn)方程為:

舉例說明,假設(shè)PCB厚度為0.0625in(h=62.5mil),,1盎司覆銅引線(t=1.35mil),,寬度為0.01in(w=10mil),,采用FR-4電路板。注意,,F(xiàn)R-4的εr典型值為4.35法拉/米(F/m),,但范圍可從4.0F/m至4.7F/m,。本例計(jì)算得到的特征值為Z0=134Ω,,C0=1.04pF/in,L0=18.7nH/in,。

對(duì)于ISM-RF設(shè)計(jì)中,,電路板上布局長(zhǎng)度為12.7mm(0.5in)的引線,可產(chǎn)生大約0.5pF和9.3nH的寄生參數(shù)(圖8),。這一等級(jí)的寄生參數(shù)對(duì)于接收器諧振槽路的影響(LC乘積的變化),,可能產(chǎn)生315MHz±2%或433.92MHz±3.5%的變化。由于引線寄生效應(yīng)所產(chǎn)生的附加電容和電感,,使得315MHz振蕩頻率的峰值達(dá)到312.17MHz,,433.92MHz振蕩頻率的峰值達(dá)到426.61MHz。

圖8.一個(gè)緊湊的PCB布局,,寄生效應(yīng)會(huì)對(duì)電路產(chǎn)生影響,。

另外一個(gè)例子是Maxim的超外差接收機(jī)(MAX7042)的諧振槽路,推薦使用的元件在315MHz時(shí)為1.2pF和30nH;433.92MHz時(shí)為0pF和16nH,。利用方程計(jì)算諧振電路振蕩頻率:

![]()

評(píng)估板諧振電路應(yīng)包括封裝和布局的寄生效應(yīng),,計(jì)算315MHz諧振頻率時(shí),寄生參數(shù)分別為7.3pF和7.5pF,。注意,,LC乘積表現(xiàn)為集總電容。

綜上所述,,布板須遵循以下原則:

保持引線長(zhǎng)度盡可能短,。

關(guān)鍵電路盡量靠近器件放置。

根據(jù)實(shí)際布局寄生效應(yīng)對(duì)關(guān)鍵元件進(jìn)行補(bǔ)償,。

接地與填充處理

接地或電源層定義了一個(gè)公共參考電壓,,通過低阻通路為系統(tǒng)的所有部件供電。按照這種方式均衡所有電場(chǎng),,產(chǎn)生良好的屏蔽機(jī)制,。

直流電流總是傾向于沿著低阻通路流通。同理,,高頻電流也是優(yōu)先流過最低電阻的通路,。所以,對(duì)于地層上方的標(biāo)準(zhǔn)PCB微帶線,,返回電流試圖流入引線正下方的接地區(qū)域,。按照上述引線耦合部分所述,,割斷的接地區(qū)域會(huì)引入各種噪聲,進(jìn)而通過磁場(chǎng)耦合或匯聚電流而增大串?dāng)_(圖9),。

圖9.盡可能保持地層完整,,否則返回電流會(huì)引起串?dāng)_。

填充地也稱為保護(hù)線,,通常將其用于電路中很難鋪設(shè)連續(xù)接地區(qū)域或需要屏蔽敏感電路的設(shè)計(jì)(圖10),。通過在引線兩端,或者是沿線放置接地過孔(即過孔陣列),,增大屏蔽效應(yīng)8,。請(qǐng)不要將保護(hù)線與設(shè)計(jì)用來提供返回電流通路的引線相混合,這樣的布局會(huì)引入串?dāng)_,。

圖10.RF系統(tǒng)設(shè)計(jì)中須避免覆銅線浮空,,特別是需要鋪設(shè)銅皮的情況下。

覆銅區(qū)域不接地(浮空)或僅在一端接地時(shí),,會(huì)制約其有效性,。有些情況下,它會(huì)形成寄生電容,,改變周圍布線的阻抗或在電路之間產(chǎn)生“潛在”通路,,從而造成不利影響。簡(jiǎn)而言之,,如果在電路板上鋪設(shè)了一塊覆銅(非電路信號(hào)走線),,來確保一致的電鍍厚度。覆銅區(qū)域應(yīng)避免浮空,,因?yàn)樗鼈儠?huì)影響電路設(shè)計(jì),。

最后,確??紤]天線附近任何接地區(qū)域的影響,。任何單極天線都將接地區(qū)域、走線和過孔作為系統(tǒng)均衡的一部分,,非理想均衡布線會(huì)影響天線的輻射效率和方向(輻射模板),。因此,不應(yīng)將接地區(qū)域直接放置在單極PCB引線天線的下方,。

綜上所述,,應(yīng)該遵循以下原則:

盡量提供連續(xù)、低阻的接地區(qū)域,。

填充線的兩端接地,,并盡量采用過孔陣列。

RF電路附近不要將覆銅線浮空,,RF電路周圍不要鋪設(shè)銅皮,。

如果電路板包括多個(gè)地層,,信號(hào)線從一側(cè)過度另一側(cè)時(shí),最好鋪設(shè)一個(gè)接地過孔,。

晶體電容過大

寄生電容會(huì)使晶振的工作頻率偏離目標(biāo)值9,。因此,須遵循一些常規(guī)準(zhǔn)則,,降低晶體引腳,、焊盤、走線或與RF器件連接的雜散電容,。

應(yīng)遵循以下原則:

晶體與RF器件之間的連線盡可能短,。

相互之間的走線盡可能保持隔離。

如果并聯(lián)寄生電容太大,,則去除晶體下方的接地區(qū)域。

平面走線電感

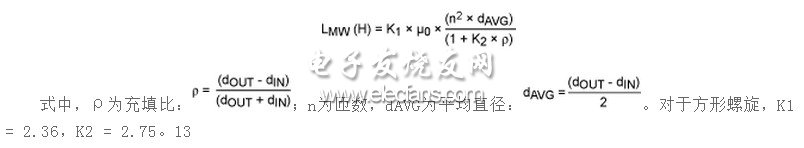

不建議使用平面走線或PCB螺旋電感,,典型PCB制造工藝具有一定的不精確性,,例如寬度、空間容差,,從而對(duì)元件值精度影響非常大,。因此,大多數(shù)受控和高Q值電感均為繞線式,。其次,,可以選擇多層陶瓷電感,多層片式電容廠商也提供這種產(chǎn)品,。盡管如此,,有些設(shè)計(jì)者還是在不得已的情況下選擇了螺線電感。計(jì)算平面螺旋電感的標(biāo)準(zhǔn)公式通常采用惠勒公式10:

![]()

式中,,a為線圈的平均半徑,,單位為英寸;n為匝數(shù);c為線圈磁芯的寬度(rOUTER-rINNER),單位為英寸,。當(dāng)線圈的c>0.2a時(shí)11,,該計(jì)算方法的精度在5%之內(nèi)。

可以使用方形,、六角形或其它形狀的單層螺旋電感,。可以找到非常好的近似方法,,對(duì)集成電路晶圓上的平面電感進(jìn)行建模,。為了達(dá)到這一目的,對(duì)標(biāo)準(zhǔn)惠勒公式進(jìn)行修改,,得到非常適合小尺寸及方形規(guī)格的平面電感估算方法12,。

避免使用這種電感的原因有很多,,它們通常受空間限制而導(dǎo)致電感值減小。避免使用平面電感的主要原因是受限制的幾何尺寸,,以及對(duì)臨界尺寸的控制較差,,從而無法預(yù)測(cè)電感值。此外,,PCB生產(chǎn)過程中很難控制實(shí)際電感值,,電感還會(huì)將噪聲耦合到電路的其它部分的趨向(參見上文中的引線耦合部分)。

總而言之,,應(yīng)該:

避免使用平面走線電感,。

盡量使用繞線片式電感。

總結(jié)

如上所述,,幾種常見的PCB布局陷阱會(huì)造成ISM-RF設(shè)計(jì)問題,。然而,注意電路的非理想特性,,您完全可避免這些缺陷,。補(bǔ)償這些不希望的影響需要適當(dāng)處理表面上無關(guān)緊要的事項(xiàng),例如元件方向,、走線長(zhǎng)度,、過孔布置,以及接地區(qū)域的用法,。遵守以上的指導(dǎo)原則,,您可明顯節(jié)省浪費(fèi)在修正錯(cuò)誤方面的時(shí)間和金錢。