引言

在計算機(jī)的數(shù)據(jù)通信中,外設(shè)一般不能與計算機(jī)直接相連,它們之間的信息交換主要存在以下問題:

(1)速度不匹配。外設(shè)的工作速度和計算機(jī)的工作速度不一樣,而且外設(shè)之間的工作速度差異也比較大。

(2)數(shù)據(jù)格式不匹配。不同的外設(shè)在進(jìn)行信息存儲和處理時的數(shù)據(jù)格式可能不同,例如最基本的數(shù)據(jù)格式可分為并行數(shù)據(jù)和串行數(shù)據(jù)。

(3)信息類型不匹配。不同的外設(shè)可能采用不同類型的型號,有些是模擬信號,有些是數(shù)字信號,因此采用的處理方式也不同。

為了解決外設(shè)和計算機(jī)之間的信息交換問題,即需要設(shè)計一個信息交換的中間環(huán)節(jié)接口。UART控制器是最常用的接口。

通用異步收發(fā)器(UniversalAsynchrONousReceiv2er/Transmitter,UART)是輔助計算機(jī)與串行設(shè)備之間的通信,作為RS232通信接口的一個重要的部分,目前大部分的處理器都集成了UART。

1 UART的數(shù)據(jù)格式

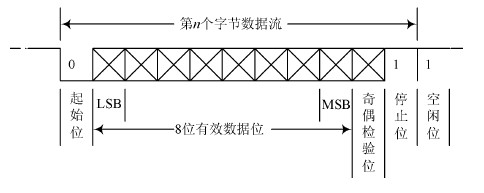

UART的數(shù)據(jù)傳輸格式如圖1所示。

圖1 UART的數(shù)據(jù)傳輸格式

由于數(shù)字圖像亞像素在計算機(jī)中是用8位二進(jìn)制表示,因此UART傳輸?shù)挠行?shù)據(jù)位為8位。傳輸線在空閑時為高電平,因此有效數(shù)據(jù)流的開始位設(shè)為0。

接著傳輸8位有效數(shù)據(jù)位,先從最低位開始傳送。奇偶檢驗位可以設(shè)置為奇檢驗、偶校驗或者不設(shè)置校驗位,由于本系統(tǒng)使用的傳輸速率不高,為了加快開發(fā)進(jìn)程,減少電路面積,因此沒有設(shè)計奇偶檢驗?zāi)K,數(shù)據(jù)流中不設(shè)奇偶檢驗位。最后停止位為高電平。

2 UART的基本結(jié)構(gòu)

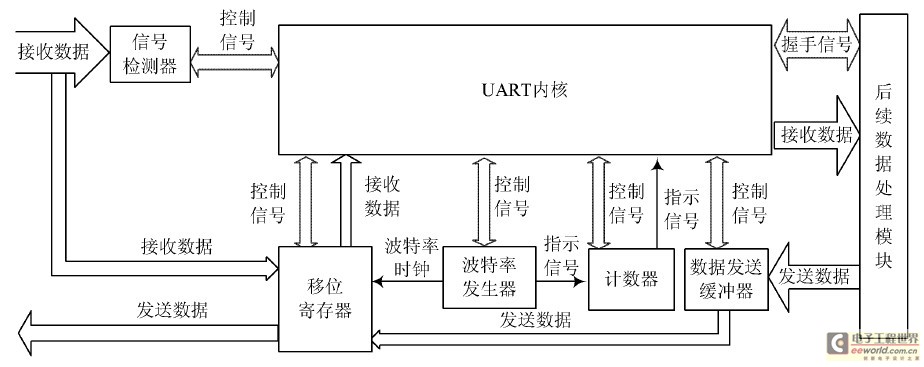

設(shè)計的UART主要由UART內(nèi)核、信號檢測器、移位寄存器" title="移位寄存器">移位寄存器、波特率發(fā)生器和計數(shù)器組成,如圖2所示。

圖2 UART基本結(jié)構(gòu)

UART各個功能模塊的功能如下文所述。

2.1 信號檢測器模塊

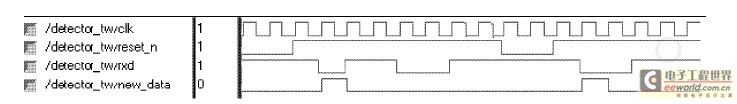

信號檢測器用于對RS232的輸入信號進(jìn)行實時監(jiān)測,一旦發(fā)現(xiàn)新的數(shù)據(jù)則立即通知UART內(nèi)核。信號檢測器的仿真波形如圖3所示。

圖3 信號檢測器仿真波形圖

其中,RxD第一次為低時,new_data信號闡述輸出,之后RxD又變低,但由于信號檢測器處于鎖定狀態(tài),所以new_data信號并沒有輸出;最后,reset_n信號將信號檢測器復(fù)位,RxD再次變低時,new_data又有輸出。可見信號檢測器的實現(xiàn)完全正確,其功能完全符合設(shè)計要求。

2.2 移位寄存器模塊

移位寄存器模塊的作用是存儲輸入或者輸出數(shù)據(jù)。

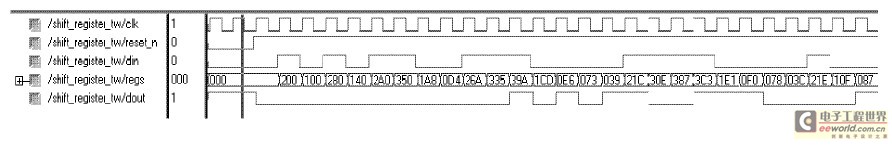

當(dāng)UART接收RS232輸入時,移位寄存器在波特率模式下采集RS232輸入信號,且保存結(jié)果;當(dāng)進(jìn)行RS232輸出時,UART內(nèi)核首先將數(shù)據(jù)加載到移位寄存器內(nèi),再使移位寄存器在波特率模式下將數(shù)據(jù)輸出到RS232輸出端口上。移位寄存器的仿真波形圖如圖4所示。

關(guān)鍵字:嵌入式" title="嵌入式">嵌入式 UART接口模塊" title="UART接口模塊">UART接口模塊

圖4 移位寄存器仿真波形圖

如圖4所示,移位寄存器在復(fù)位后的每個時鐘的上升沿工作。由于數(shù)據(jù)發(fā)送時是先發(fā)送有效數(shù)據(jù)的最低位,因此移位寄存器是將接收的數(shù)據(jù)由高位向低位移動,dout輸出移位寄存器的最低位。圖中的regs數(shù)據(jù)用16進(jìn)制表示。

2.3 波特率發(fā)生器模塊

波特率發(fā)生器的功能是產(chǎn)生和RS232通信所采用的波特率同步的時鐘,這樣才能方便地按照RS232串行通信的時序要求進(jìn)行數(shù)據(jù)接收或者發(fā)送。比如,波特率為9600b/s,即每秒傳輸9600b數(shù)據(jù),則同步的波特率時鐘頻率為9600Hz,周期為1/9600=0.10417。

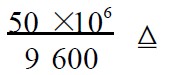

設(shè)計波特率時鐘的基本思路就是設(shè)計一個計數(shù)器,該計數(shù)器工作在速度很高的系統(tǒng)時鐘下,當(dāng)計數(shù)器計數(shù)到某數(shù)值時將輸出置高,再計數(shù)到一定的數(shù)值后再將輸出置低,如此反復(fù)便能夠得到所需的波特率時鐘。該系統(tǒng)所用的FPGA系統(tǒng)時鐘為50MHz,RS232通信的波特率為9600b/s,則波特率時鐘的每個周期相當(dāng)于

5208個系統(tǒng)時鐘周期。假如要得到占空比為50%的波特率時鐘,只要使得計數(shù)器在計數(shù)到1604時將輸出置高,之后在計數(shù)到5208時將輸出置低并且重新計數(shù),就能實現(xiàn)和9600波特率同步的時鐘。

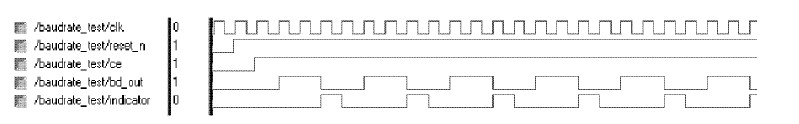

為了便于仿真,使計數(shù)器計到2時將輸出置高,之后計到4時將輸出置地并且重新計數(shù)。波特率發(fā)生器的仿真波形圖如圖5所示。

圖5 波特率發(fā)生器仿真波形圖

觀察波形可以看到波特率發(fā)生器每經(jīng)過4個時鐘周期輸出1個完整的波特率時鐘周期,占空比為1/2,并且在每次輸出波特率時鐘周期之后輸出1個系統(tǒng)時鐘脈寬的提示信號indicator,UART通過此信號來了解波特率發(fā)生器已輸出的波特率時鐘周期個數(shù)。由波形圖可見波特率發(fā)生器的工作完全滿足設(shè)計的要求。

2.4 計數(shù)器模塊

計數(shù)器模塊的功能是可控的,在輸入時鐘的驅(qū)動下進(jìn)行計數(shù),當(dāng)達(dá)到計數(shù)上閾時給UART內(nèi)核一個提示信號。在不同的工作狀態(tài)下,計數(shù)器模塊的輸入時鐘是不同的。UART在數(shù)據(jù)發(fā)送之前需要進(jìn)行數(shù)據(jù)加載(即將串行序列保存在移位寄存器內(nèi)),在此工程中計數(shù)器模塊的輸入時鐘為系統(tǒng)時鐘,因為此時移位寄存器也工作在系統(tǒng)時鐘下。除了數(shù)據(jù)加載,另外2個需要計數(shù)器模塊的過程是數(shù)據(jù)接收和數(shù)據(jù)發(fā)送。

由于這兩個過程中移位寄存器工作在波特率時鐘下,所以計數(shù)器模塊的時鐘就是與波特率時鐘同步的波特率發(fā)生器提示信號indicator,這樣每輸出1個完整的波特率時鐘周期計數(shù)器就能增加1。

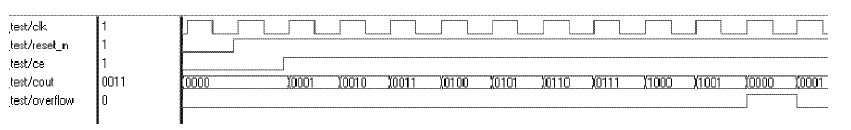

計數(shù)器的仿真波形圖如圖6所示。

圖6 計數(shù)器仿真波形圖

計數(shù)器在復(fù)位后并且ce有效時開始計數(shù),并且在第10個時鐘周期輸出提示信號overflow。

2.5 發(fā)送數(shù)據(jù)緩沖器模塊

發(fā)送數(shù)據(jù)緩沖器模塊的功能是將要發(fā)送的并行數(shù)據(jù)轉(zhuǎn)換成串行數(shù)據(jù),并且在輸出的串行數(shù)據(jù)流中加人起始位和停止位。緩沖器首先將要發(fā)送的8位數(shù)據(jù)寄存,并在最低位后添加起始位‘0’,在最高位前添加停止位‘1’,組成10位要發(fā)送的數(shù)據(jù),然后根據(jù)UART內(nèi)核模塊的計數(shù)值將相應(yīng)的數(shù)據(jù)送入移位寄存器輸入端。

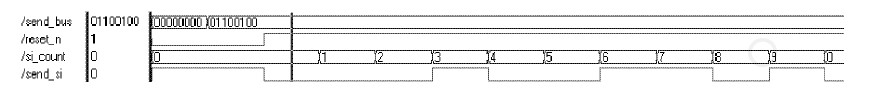

UART內(nèi)核模塊輸出的計數(shù)值是從0依次計到9,即先將要發(fā)送數(shù)據(jù)的最低位送入移位寄存器。發(fā)送數(shù)據(jù)緩沖器的仿真波形圖如圖7所示。

圖7 發(fā)送數(shù)據(jù)緩沖器仿真波形圖

由波形圖可知,發(fā)送數(shù)據(jù)緩沖器在復(fù)位后,在輸入的計數(shù)值si_count為0時,send_si輸出起始位‘0’。在輸入的計數(shù)值si_count為1~8時,send_si分別輸出send_bus上相應(yīng)的數(shù)據(jù)位。在輸入的計數(shù)值si_count為9時,send_si輸出停止位‘1’。

2.6 UART內(nèi)核模塊

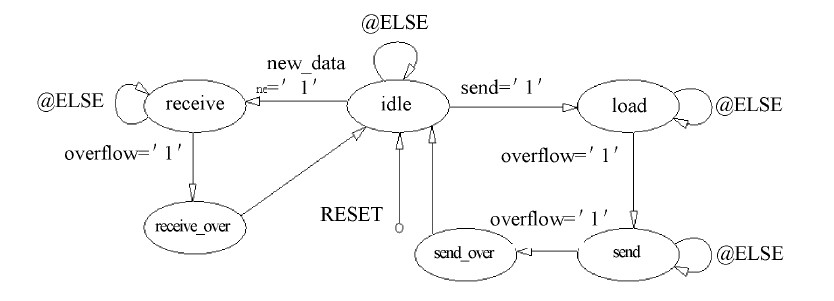

UART內(nèi)核模塊是整個設(shè)計的核心。在數(shù)據(jù)接收時,UART內(nèi)核模塊負(fù)責(zé)控制波特率發(fā)生器和移位寄存器,使得移位寄存器在波特率時鐘的驅(qū)動下同步地接收并且保存RS232接收端口上的數(shù)據(jù)。在數(shù)據(jù)發(fā)送時,UART內(nèi)核模塊首先根據(jù)待發(fā)送數(shù)據(jù)產(chǎn)生完整的發(fā)送數(shù)據(jù)序列(包括起始位、數(shù)據(jù)位和停止位),之后控制移位寄存器將序列加載到移位寄存器的內(nèi)部寄存器里,最后再控制波特率發(fā)生器驅(qū)動移位寄存器將數(shù)據(jù)串行輸出。UART內(nèi)核模塊的主要功能是控制數(shù)據(jù)接收、數(shù)據(jù)加載和數(shù)據(jù)發(fā)送的過程,這可以用狀態(tài)機(jī)來實現(xiàn),其狀態(tài)圖如圖8所示。

圖8 UART內(nèi)核狀態(tài)轉(zhuǎn)移圖

(1)數(shù)據(jù)加載過程。數(shù)據(jù)的接收過程可以定義3個狀態(tài):空閑“idle”狀態(tài)、接收“receive”和接收完成“receive_over”。UART內(nèi)核模塊在復(fù)位后進(jìn)入空閑狀態(tài)。如果信號檢測器檢測到數(shù)據(jù)傳輸,即new_data=‘1’,UART內(nèi)核檢測到此信號就會進(jìn)入接收狀態(tài)。

在UART進(jìn)入由空閑狀態(tài)轉(zhuǎn)為接收狀態(tài)過程中,需要進(jìn)行一系列的接收預(yù)備操作,包括將子模塊復(fù)位、選擇移位寄存器串行輸入數(shù)據(jù)以及選擇移位寄存器的輸入時鐘等。進(jìn)入接收狀態(tài)后,波特率發(fā)生器開始工作,其輸出波特率時鐘驅(qū)動移位寄存器同步的存儲RS232接收端口上的數(shù)據(jù),并且其提示信號“indicator”驅(qū)動計數(shù)器進(jìn)行計數(shù)。當(dāng)所有數(shù)據(jù)接收完成,計數(shù)器也達(dá)到了其計數(shù)的上閾,此時overflow=‘1’,通知UART內(nèi)核進(jìn)入接收狀態(tài)。UART內(nèi)核進(jìn)入接收完成狀態(tài)的同時,會檢奇偶校驗的結(jié)果,同時使得子模塊使能信號無效,以停止各個子模塊。

UART內(nèi)核的接收完成狀態(tài)僅保持1個時鐘周期,設(shè)置這個狀態(tài)的作用是借用一個時鐘周期復(fù)位信號檢測器,準(zhǔn)備接收下次數(shù)據(jù)傳輸。

檢測器,準(zhǔn)備接收下次數(shù)據(jù)傳輸。

(2)數(shù)據(jù)加載和發(fā)送過程。數(shù)據(jù)加載和發(fā)送的過程都是為發(fā)送數(shù)據(jù)而設(shè)定的,所以將它們放在一起進(jìn)行介紹,可以用4個狀態(tài)來實現(xiàn)上述的過程,即空閑、加載、發(fā)送和發(fā)送完成。其中的空閑狀態(tài)是UART內(nèi)核復(fù)位后的空閑狀態(tài),與上面介紹的數(shù)據(jù)接收過程的空閑狀態(tài)一致。數(shù)據(jù)加載過程在數(shù)據(jù)發(fā)送過程之前進(jìn)行。

UART內(nèi)核復(fù)位后進(jìn)入空閑狀態(tài),當(dāng)探測到發(fā)送控制信號有效時,即send=‘1’,便會進(jìn)入加載狀態(tài)開始數(shù)據(jù)加載。在進(jìn)入加載狀態(tài)的同時,UART內(nèi)核會將移位寄存器、計數(shù)器復(fù)位,并且通過選擇信號使得移位寄存器的輸入為發(fā)送數(shù)據(jù)緩沖器模塊產(chǎn)生的串行數(shù)據(jù)序列,使得移位寄存器和計數(shù)器的工作時鐘為系統(tǒng)時鐘。

進(jìn)入加載狀態(tài)后,在UART內(nèi)核控制下,發(fā)送數(shù)據(jù)緩沖器模塊會將完整的待發(fā)送序列加載到移位寄存器的數(shù)據(jù)輸入端,發(fā)送的序列是和系統(tǒng)時鐘同步的,移位寄存器在系統(tǒng)時鐘的驅(qū)動下不斷讀入輸入端數(shù)據(jù)并保存在內(nèi)部寄存器內(nèi)。在移位寄存器加載數(shù)據(jù)的同時,計數(shù)器也在時鐘的驅(qū)動下進(jìn)行計數(shù),由于都是工作在系統(tǒng)時鐘下,所以當(dāng)所有數(shù)據(jù)被加載時,計數(shù)器也達(dá)到了計數(shù)的上閾(即串行數(shù)據(jù)的總量),此時overflow=‘1’,通知UART內(nèi)核進(jìn)入發(fā)送狀態(tài)。UART內(nèi)核進(jìn)入發(fā)送狀態(tài)的同時會改變幾個選擇信號,比如將移位寄存器的時鐘設(shè)為波特率時鐘,將計數(shù)器時鐘設(shè)為波特率的提示信號,最重要的是將輸出信號送到RS232的發(fā)送端口TxD上。發(fā)送的過程和接收類似,移位寄存器在波特率時鐘的驅(qū)動下內(nèi)部寄存器的數(shù)據(jù)串行的發(fā)送出去,同時計數(shù)器在波特率發(fā)生器的提示信號驅(qū)動下進(jìn)行計數(shù)。

UART內(nèi)核在計數(shù)器到達(dá)計數(shù)上閾后便進(jìn)入發(fā)送完成模式,并且輸出發(fā)送完成信號。

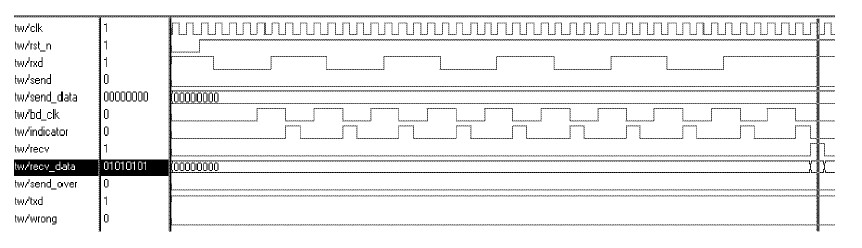

3 UART頂層模塊的仿真測試

將上述各個模塊的VHDL代碼生成原理圖符號,并在原理圖編輯工具中將各個模塊連接起組成1個完整的UART模塊。為了驗證UART模塊的正確性,對UART的發(fā)送過程和接收過程分別進(jìn)行了波形仿真。

為便于觀察波形,波特率產(chǎn)生器設(shè)置為4個系統(tǒng)時鐘產(chǎn)生一個完整的波特率時鐘。圖9是UART模塊接收過程的仿真波形圖。

圖9 UART數(shù)據(jù)接收過程的仿真波形圖

由仿真波形圖可以看出,接收端RxD上的數(shù)據(jù)序列為0101010101,起始位‘0’后為數(shù)據(jù)位“10101010”,最后一位為停止位‘1’。在10個波特率時鐘之后,UART發(fā)出1個接收完成信號recv=‘1’,并在數(shù)據(jù)輸出端“new_data”將接收的數(shù)據(jù)輸出給后續(xù)數(shù)據(jù)處理模塊。由于發(fā)送數(shù)據(jù)時首先發(fā)送數(shù)據(jù)的最低位,因此接收的數(shù)據(jù)應(yīng)為“01010101”,將光條放置數(shù)據(jù)輸出端“new_data”的數(shù)據(jù)輸出波形上,可以從數(shù)據(jù)欄看到此時數(shù)據(jù)輸出端new_data=“01010101”,UART數(shù)據(jù)接收功能完全正確。

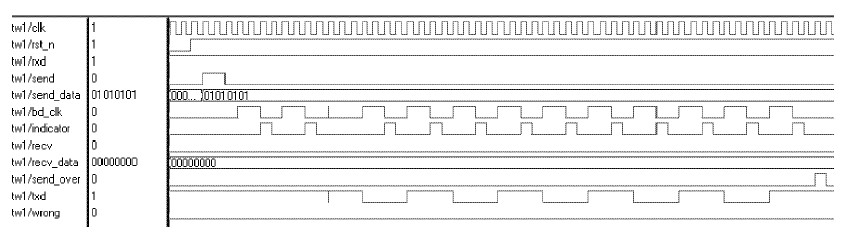

圖10為UART發(fā)送過程仿真波形。由圖可以看出,send=‘1’后待發(fā)送數(shù)據(jù)為“01010101”,將待發(fā)送數(shù)據(jù)加上起始位和停止位,并從最低位開始發(fā)送,則發(fā)送端txd上的數(shù)據(jù)序列為“0101010101”,發(fā)送停止位后,發(fā)送結(jié)束信號send_over=‘1’。圖10證明UART數(shù)據(jù)發(fā)送功能完全正確。

圖10 UART數(shù)據(jù)發(fā)送過程的仿真波形圖

4 結(jié)語

介紹了UART在可編程邏輯器件FPGA上的實現(xiàn),并通過實際電路驗證了設(shè)計的功能,使用FPGA不僅可以方便地用串口協(xié)議與PC機(jī)進(jìn)行串行通信,而且擴(kuò)展了板級系統(tǒng)的接口功能。應(yīng)用在可編程器件FP2GA內(nèi)部,可以很大程度地減少電路板的使用面積,并提高系統(tǒng)的穩(wěn)定性和可編程性。