隨著 Xilinx ISE 設(shè)計套件 11.1 的推出,賽靈思在優(yōu)化設(shè)計方法、更好地滿足不同技能客戶的多樣化需求,以及幫助客戶利用賽靈思 FPGA 目標(biāo)設(shè)計平臺進(jìn)行創(chuàng)新設(shè)計方面邁出了一大步。賽靈思 ISE 設(shè)計套件 11.1同時推出四種全新的工具流程,專為邏輯設(shè)計人員、嵌入式開發(fā)人員、DSP算法開發(fā)人員以及系統(tǒng)集成人員量身定制,以滿足他們的不同要求。

2009 年賽靈思版權(quán)所有。Xilinx、Xilinx 徽標(biāo)、Virtex、Spartan、ISE、以及本文涉及的其它指定品牌均為賽靈思公司在美國及其它國家的商標(biāo)。MATLAB 以及 Simulink 均為 The MathWorks 公司的注冊商標(biāo)。PCI、PCle 以及 PCI E 為 PCI-SIG 的商標(biāo),須得到許可后才可使用。PowerPC 名稱及徽標(biāo)為 IBM 公司的注冊商標(biāo),須得到許可才可使用。所有其它商標(biāo)均歸其各自所有者所有。

此前,賽靈思的客戶主要是邏輯設(shè)計人員,他們是精通硬件設(shè)計和硬件描述語言 (HDL) 的電氣工程師。不過,在過去 8 年間,隨著各代 Virtex 和 Spartan FPGA 產(chǎn)品的推出,邏輯單元以及 MPU 和 DSP 等嵌入式軟硬件處理器呈指數(shù)級增長。在此情況下,賽靈思的客戶中迅速增加了大量嵌入式軟硬件工程師、DSP 算法開發(fā)人員和系統(tǒng)集成人員,他們都使用賽靈思的器件來構(gòu)建高級片上系統(tǒng)。也就是說,不僅多領(lǐng)域的設(shè)計團(tuán)隊在使用賽靈思的器件,而且很多情況下,就連對 HDL設(shè)計不了解或了解甚少的人如今也都在用賽靈思 FPGA開展系統(tǒng)設(shè)計工作。

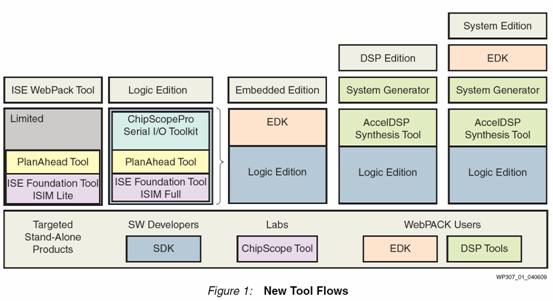

在推出 ISE 設(shè)計套件 11.1之前,賽靈思為所有客戶提供了一套完整的工具和 IP。每個用戶可以根據(jù) FPGA 編程的需要選擇使用不同的工具。不過,如果客戶對邏輯/連接設(shè)計不熟悉的話,可能會對眾多工具和IP的選擇感到無所適從。舉例來說,如果客戶不熟悉硬件調(diào)試,可能就不了解 ChipScope Pro 分析器的優(yōu)點,不知道這款工具能自動完成調(diào)試任務(wù),可以幫助用戶簡化設(shè)計工作。為了幫助不同設(shè)計領(lǐng)域的用戶在熟悉的可定制環(huán)境中更高效地開展設(shè)計工作,賽靈思現(xiàn)在推出了四種全新的ISE 設(shè)計套件配置版本:邏輯版本、嵌入式版本、DSP 版本和系統(tǒng)版本(見圖 1)。

圖 1:全新工具流程

賽靈思對不同領(lǐng)域的客戶進(jìn)行了認(rèn)真地調(diào)查,了解其設(shè)計方法,看看他們會使用賽靈思和第三方合作伙伴提供的哪些工具成功進(jìn)行賽靈思 FPGA設(shè)計工作。

賽靈思的軟件設(shè)計部根據(jù)上述調(diào)查研究推出了四種全新的 ISE 設(shè)計套件 配置版本。這四種配置版本既能幫助經(jīng)驗豐富的客戶優(yōu)化工具選購,也能幫助FPGA設(shè)計新手輕松確定哪些工具最適合他們的設(shè)計需求。每個配置版本都配套提供全面的設(shè)計創(chuàng)建、驗證和實施工具以及針對特定領(lǐng)域的 IP。

上述四種新版本都可以定制,因此用戶能根據(jù)設(shè)計流程的需要選擇添加賽靈思或第三方合作伙伴提供的其他工具。賽靈思不會規(guī)定用戶的設(shè)計流程,而是創(chuàng)建了可擴展、可定制的基礎(chǔ)流程。此外,設(shè)計經(jīng)理可根據(jù)設(shè)計團(tuán)隊的需求和每名設(shè)計團(tuán)隊成員的實際技能選擇最適當(dāng)?shù)脑S可證數(shù)量和類型。舉例來說,新推出的四種配置版本允許客戶為設(shè)計團(tuán)隊添加諸如賽靈思軟件開發(fā)套件 (SDK) 等額外的許可證選項,這樣設(shè)計團(tuán)隊就能讓數(shù)名軟件開發(fā)人員為單個 FPGA 編寫代碼,而不必像過去那樣購買整套嵌入式開發(fā)套件 (EDK)。

全新 ISE 設(shè)計套件配置版本的推出是賽靈思目標(biāo)設(shè)計平臺戰(zhàn)略的關(guān)鍵部分,可幫助賽靈思集中精力推出市場上最佳的 FPGA硅芯片,并配套提供業(yè)界一流的軟硬件設(shè)計工具、IP、開發(fā)板以及技術(shù)支持,幫助客戶取得成功,并讓客戶集中精力開展增值設(shè)計工作,盡快向市場推出創(chuàng)新設(shè)計。參見:WP306,賽靈思目標(biāo)設(shè)計平臺:推動“可編程技術(shù)勢在必行”之趨勢。

全新 ISE 設(shè)計套件配置版本

賽靈思 ISE 設(shè)計套件 11.1提供了四種全新的不同配置版本:邏輯版本、嵌入式版本、DSP 版本和系統(tǒng)版本。每種版本都提供完整的設(shè)計流程,包括相關(guān)工具、針對特定領(lǐng)域和應(yīng)用的IP,以及參考設(shè)計。

除了提供上述四種全新的ISE 設(shè)計套件配置版本外,賽靈思還繼續(xù)推出 ISE WebPACK軟件(賽靈思工具流程的限定器件版)、SDK、ChipScope Pro 分析器、EDK和DSP(AccelDSP 綜合工具和System Generator for DSP),作為獨立的產(chǎn)品供用戶添加到自己的流程中。

邏輯版本

全新邏輯版本是面向RTL設(shè)計的完整流程,其特性有助于縮短運行時間,提高存儲器利用率、可用性、精確度,以及優(yōu)化功耗等,相對于前一版本而言,不僅能將動態(tài)功耗降低高達(dá) 10%,存儲器利用率提高28%,而且還可將布局和布線編譯時間縮短1/2。

邏輯版本既可作為所有賽靈思設(shè)計人員所選版本流程的基礎(chǔ),也可作為一個獨立的套件,其包括所有賽靈思老客戶熟悉的工具。

邏輯版本包括 ISE Foundation 軟件、PlanAhead 設(shè)計分析工具、帶Serial I/O工具包的 ChipScope Pro 分析器、ISE Simulator 以及 CORE Generator 工具 IP。

邏輯版本:創(chuàng)建設(shè)計方案

在邏輯版本流程中,用戶可在 ISE Foundation 中打開 ISE Project Navigator以啟動項目。利用該工具,用戶可啟動 CORE Generator 界面并選擇最適合設(shè)計需要的 IP 核。隨后用戶可用 Project Navigator 中的 HDL 編輯器來編寫設(shè)計方案的 HDL 表示。CORE Generator 軟件包括數(shù)百個針對專門領(lǐng)域和應(yīng)用的內(nèi)核,允許用戶快速將預(yù)定義的功能添加到設(shè)計方案中,從而集中主要精力創(chuàng)建設(shè)計方案的增值部分。在 ISE 設(shè)計套件 11.1 工具中,賽靈思針對視頻市場需求增加了新的IP,也為所有賽靈思內(nèi)核提供了版本數(shù)據(jù),使用戶全面監(jiān)控內(nèi)核情況。

設(shè)計人員隨后可用 ISE 設(shè)計套件 軟件中的賽靈思存儲器接口生成器 (MIG) 工具生成適用于賽靈思 FPGA 的存儲器控制器和接口。MIG 工具還可生成未加密的 Verilog 或 VHDL 設(shè)計文件、UCF 約束文件、仿真文件和實施腳本文件,以簡化設(shè)計流程。在上一版本的 ISE 設(shè)計套件 軟件中,MIG 用戶在修改存儲器模塊的引腳分配時必須了解布局、布線和時序限制情況。在 ISE 設(shè)計套件 11.1 中,賽靈思對相關(guān)工具進(jìn)行了改進(jìn),布局和布線引擎在存儲器接口的引腳分配發(fā)生變動時能自動實施設(shè)計方案(用戶不必手動改變布局和布線限制)。此外,在將功能集成到設(shè)計方案中時,用戶還能獲得 PCIe 接口內(nèi)核的可預(yù)見時序功能。ISE 設(shè)計套件 11.1 工具目前支持 DDR3 SDRAM、DDR2 SDRAM、DDR SDRAM、QDRII SRAM、DDRII SRAM以及RLDRAM II。

用戶選定模塊并創(chuàng)建 HDL 表達(dá)后,即可綜合設(shè)計方案,執(zhí)行平面規(guī)劃,并前瞻性地進(jìn)行引腳分配。

針對邏輯綜合,ISE 設(shè)計套件 軟件提供了內(nèi)置的 XST 綜合引擎。在 ISE 設(shè)計套件 11.1 中,XST 綜合的運行速度比上一版本平均提高 1.6 倍。

所有 ISE 軟件版本的捆綁(包括 ISE WebPACK 工具)都免費配套提供 PlanAhead 軟件的完整版。PlanAhead 工具是一款功能齊全的設(shè)計分析駕駛艙,提供了高級 FPGA 實施管理的關(guān)鍵特性,如I/O引腳分配、平面規(guī)劃、設(shè)計分析和實施等功能。現(xiàn)在,我們可從 Project Navigator 中調(diào)用 PlanAhead 工具,執(zhí)行引腳規(guī)劃和平面規(guī)劃等工作。此外該工具也可作為獨立的可執(zhí)行文件使用,提供高級實施和調(diào)試功能。

在 ISE 設(shè)計套件 11.1 中,用戶能通過 PlanAhead 工具獲得 ChipScope Pro 調(diào)試工具內(nèi)核插入功能,其中包括全新向?qū)Чδ埽軒椭脩粼谒性O(shè)計方案中方便地插入測試監(jiān)控邏輯,從而更方便地監(jiān)控信號,隨后還能通過 ChipScope Pro 工具查找錯誤。

設(shè)計人員可用 PlanAhead 軟件的引腳布局功能來進(jìn)行引腳分配,再將引腳布局信息發(fā)送給PCB 設(shè)計人員,從而盡早啟動 PCB 開發(fā)工作。

邏輯版本用戶還能在設(shè)計流程的各個環(huán)節(jié)利用 PlanAhead 軟件中的 TimeAhead 功能來獲得實施布局和布線估算,了解給定的平面規(guī)劃安排對時序預(yù)算會產(chǎn)生什么影響。用戶獲得大致的平面規(guī)劃后,就能利用實施運行功能。該功能驅(qū)動 ISE 軟件的布局和布線引擎創(chuàng)建一種或多種不同設(shè)計實施方案,以及嘗試多種不同的布局方案,并最終確定在單元利用率、節(jié)能和設(shè)計性能等方面表現(xiàn)最出色的布局方案。在布局過程中,用戶可發(fā)現(xiàn)出現(xiàn)時序違規(guī)的區(qū)域,然后對功能和模塊調(diào)整修改,優(yōu)化設(shè)計方案,解決時序問題,并快速再次運行實施方案來比較結(jié)果。

邏輯版:采用 ISE 設(shè)計套件 驗證設(shè)計方案

邏輯版還包含廣泛系列的分析與測試工具,可幫助用戶驗證其設(shè)計方案的功能性、時序與功耗。

邏輯版針對邏輯仿真提供了 ISim 仿真器。此外也可使用 Mentor Graphics ModelSim Xilinx Edition (MXE-III)、Cadence NCSim 以及 Synopsys VCS 仿真器。在 ISE 11.1 軟件中,ISim的運行速度比此前版本 10.1 (service pack 3) 快 2 倍。ISE 軟件的邏輯版還集成了更快速的SecureIP 仿真模型,能對專用模塊進(jìn)行建模。此外,ISim 現(xiàn)在還提供了類似于示波器的波形察看器和導(dǎo)航功能,能編寫 Switching Activity Interchange Format (SAIF) 以支持賽靈思 XPower工具的功率估算,同時還能導(dǎo)入和導(dǎo)出用戶波形設(shè)置。

邏輯版針對功耗分析提供了 XPower Estimator 和 Analyzer 工具。用戶首先通過輸入頻率、器件利用率以及 I/O 類型等數(shù)據(jù)完成 XPower Estimator 的數(shù)據(jù)表單,明確其設(shè)計方案的功耗目標(biāo)。設(shè)計方案的放置和布線完成后,用戶可使仿真器生成 VCD 文件,并用 XPower Analyzer 確保設(shè)計方案能夠滿足其功耗目標(biāo)。

在邏輯版中,ChipScope Pro 工具使用戶能直接在其設(shè)計方案中插入邏輯分析器、總線分析器以及虛擬 I/O 低規(guī)范軟件內(nèi)核 (Low-profile software core)。用戶插入分析器 IP 后,即可查看嵌入式或軟處理器等所有內(nèi)部信號或節(jié)點,如同使用了外接示波器。

ISE 11.1軟件還提供了 ChipScope Pro Serial I/O 工具套件作為 ISE 設(shè)計套件 各版本的標(biāo)準(zhǔn)特性。該工具使用戶能夠設(shè)置并調(diào)試 Virtex-4 FX、Virtex-5 LXT、Virtex-5 SXT、Virtex-5 FXT 以及 Virtex-5 TXT FPGA 串行 I/O 通道,測量多通道的比特誤差率,在串行 I/O 通道與系統(tǒng)其他部分交互的同時實時調(diào)節(jié)高速串行收發(fā)器參數(shù)等。此外,該工具還包含支持所有標(biāo)準(zhǔn)串行 I/O 數(shù)據(jù)分組的內(nèi)置模式生成器和模式接收機。

邏輯版:采用 ISE 設(shè)計套件 實施設(shè)計

邏輯版還包含更高性能的放置與布線引擎。

賽靈思已添加了最新的內(nèi)置活動估算引擎來實施工具流程,能在設(shè)計的實施階段自動識別功耗大的模塊。識別出功耗大的模塊之后,該工具可執(zhí)行再綜合任務(wù),以便在相關(guān)模塊中重新編輯可減少這些模塊中開關(guān)元件的邏輯。

此外,賽靈思還在 ISE 軟件中為放置和布線引擎添加了新的功耗降低特性。ISE 11.1 軟件放置器現(xiàn)在可提供最新的時鐘門控特性,在用戶的指導(dǎo)下可采用全局時鐘緩沖器來替代高扇出寄存器時鐘啟用機制,而該特性反過來不僅有助于減小布線電容,而且還能夠最大限度地縮短連線長度,從而使器件的整體動態(tài)功耗銳降 10%。

除了低功耗特性之外,ISE 11.1 軟件的放置與布線引擎與 10.1 版本相比運行速度快了 2倍,而 SmartGuide 中的增量實施引擎的運行時間也加快了 2 倍。此外,賽靈思還為 Linux版的放置和布線引擎添加了多線程放置支持,可充分發(fā)揮多內(nèi)核處理器工作站的優(yōu)勢,從而幫助用戶進(jìn)一步加速放置與布線的運行時間。

此外,賽靈思還對 ISE 11.1 軟件中的 SmartXplorer 進(jìn)行了升級,其目前可支持計算中心的各個系統(tǒng),使設(shè)計人員能夠在整個計算主機網(wǎng)絡(luò)上的執(zhí)行多個實施運行。SmartXplorer 支持將實施運行提交給裝入程序共享設(shè)備 (LSF) 與 Sun 網(wǎng)格引擎 (SGE) 分布式計算中心來處理,而 PlanAhead 軟件還支持將實施運行提交給多個 Linux 主機來執(zhí)行,從而可實現(xiàn)并行處理。

嵌入式版本

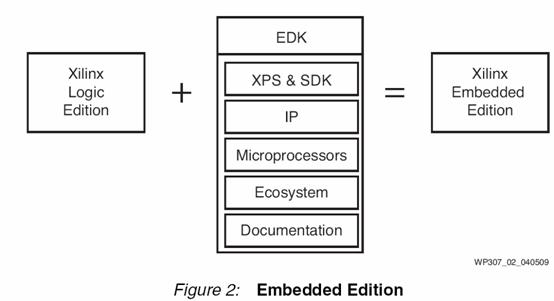

在全新嵌入式版本中,賽靈思將其備受歡迎的嵌入式開發(fā)套件 (EDK) 與邏輯版本進(jìn)行了捆綁(見圖2)。嵌入式版本旨在滿足那些希望在設(shè)計過程中充分利用嵌入式處理器高靈活優(yōu)勢的客戶的需求。賽靈思提供了兩款可實現(xiàn)最高設(shè)計靈活性的處理器內(nèi)核:MicroBlazeTM 軟處理器 32 位內(nèi)核與 PowerPC440 嵌入式處理器內(nèi)核。此外,嵌入式版本還提供必要的驅(qū)動程序、軟件應(yīng)用程序,以及嵌入式系統(tǒng)設(shè)計人員非常熟悉的調(diào)試功能。為積極響應(yīng)客戶需求,賽靈思還在 ISE 設(shè)計套件 11.1 軟件中新增了 EDK 的軟件開發(fā)套件 (SDK),,SDK 是一種面向軟件設(shè)計人員的低成本、獨立許可配置。

嵌入式版本軟件的突出優(yōu)勢包括如下:

· SDK 可為專注于嵌入式軟件應(yīng)用開發(fā)與調(diào)試的用戶提供獨立配置,從而可簡化用戶界面,與較早版本的 EDK 相比,顯著降低了磁盤空間占用;

· 采用 Base System Builder (BSB) 的雙處理器設(shè)計創(chuàng)建自動操作;

· 在使用 賽靈思目標(biāo)設(shè)計平臺進(jìn)行設(shè)計時,新版 MicroBlaze 處理器 (7.20) 可實現(xiàn)更高的優(yōu)化性。

圖 2:嵌入式版本

在嵌入式版本中使用 EDK 進(jìn)行處理器編程

EDK 是由 賽靈思Platform Studio (XPS) 與 SDK 工具、嵌入式 IP、微處理器內(nèi)核、文檔以及諸如 Wind River 與 Monta Vista 等第三方提供的接口組成。

在嵌入式版本設(shè)計流程中,用戶首先要創(chuàng)建設(shè)計 RTL,并將其導(dǎo)入 Project Navigator。如果他們想在設(shè)計方案(Virte-4 與 Virte-5 器件中的 MicroBlazeTM 軟處理器或 PowerPC 處理器)中添加微處理器內(nèi)核,應(yīng)激活 XPS 工具。

XPS 包括高級向?qū)Чぞ?BSB,使用戶能夠通過一系列鼠標(biāo)點擊選擇在設(shè)計方案中采用的微處理器(最多兩個)。用戶還可便捷地選擇所需的外設(shè)集與設(shè)計拓?fù)洹?span lang="EN-US">BSB 隨后可自動生成包括軟硬件平臺的可平穩(wěn)運行的完整嵌入式系統(tǒng),這些平臺可通過 XPS 輕松實施。該工具隨后將自動實施。較早版本的 BSB 一次只允許用戶實施單個處理器及其外設(shè)。而現(xiàn)在,ISE 設(shè)計套件 11.1 軟件中的新版 BSB 使用戶既可實施單處理器設(shè)計方案,也可實施雙處理器方案,而且配合了相關(guān)的外設(shè)。

BSB 還可提供進(jìn)一步功能,使用戶在幾個窗口中通過一系列鼠標(biāo)點擊指定要使用的開發(fā)板。隨后用戶可在設(shè)計方案中選擇實施單個處理器或雙處理器。他們可指定是否需要處理器使用 FPU,并明確目標(biāo)處理器、總線性能以及每個處理器的存儲器分配/要求(有時需要額外的 FPGA 資源)。用戶隨后可根據(jù)自己的意愿選擇添加至每個處理器的 MPU 外設(shè),并指定是否需要給定的外設(shè)專用于單處理器或由雙處理器共享。用戶指定完所有特性后,就可在 XPS 中根據(jù)需要查看、放大與實施設(shè)計方案。XPS 可精細(xì)控制連接,也就是說可獲得設(shè)計方案的各種視圖,其中包括方框圖以及系統(tǒng)組裝視圖。XPS 使用戶能夠進(jìn)行詳細(xì)的分析,并手動調(diào)節(jié)設(shè)計方案中的各個塊。用戶對設(shè)計方案滿意后,就可使 XPS 自動實施設(shè)計(XPS 將自動在后臺運行 ISE 工具)。此外,XPS 還可自動為設(shè)計方案的所有硬件組件提供必需的驅(qū)動程序。

Platform Studio 的一個全新的特性有助于用戶在 SDK 的 XML 文件中導(dǎo)出設(shè)計方案。XML 文件包含設(shè)計方案中硬件、存儲器映射以及外設(shè)的描述信息,同時還包括所有硬件外設(shè)的數(shù)據(jù)表單。

用戶導(dǎo)入 XML 文件至 SDK 后,就可在業(yè)界標(biāo)準(zhǔn)的 Eclipse 軟件開發(fā)環(huán)境下打開設(shè)計方案(不是以硬件設(shè)計為中心的 GUI),大多數(shù)軟件開發(fā)人員對這種環(huán)境都很熟悉,也是他們目前開發(fā)應(yīng)用軟件所常用的環(huán)境。

使用 SDK,用戶還可通過下拉菜單定義所要使用的操作系統(tǒng)。隨后該工具便可編輯操作系統(tǒng),以及適用于設(shè)計硬件外設(shè)的驅(qū)動程序。用戶可在工具中啟動軟件項目,創(chuàng)建軟件應(yīng)用,執(zhí)行軟件調(diào)試,建立描述,并向處理器下載應(yīng)用代碼。此外,SDK 還提供了一系列測試應(yīng)用,其中包括Dhrystone、數(shù)種存儲器與外設(shè)測試,以及 Xilkernel 演示調(diào)度程序。

增強的 Platform Studio 版本可實現(xiàn)版本的修訂歷史跟蹤功能,為設(shè)計人員提供了漸進(jìn)性更改設(shè)計方案的功能,并確保設(shè)計人員能根據(jù)需要返回到以前的版本。

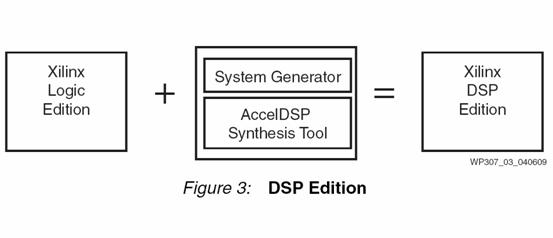

DSP 版

新的 DSP 版包括賽靈思邏輯版以及賽靈思 DSP捆綁包(System Generator 開發(fā)環(huán)境和AccelDSP 綜合工具)。參見圖 3。

圖 3:DSP 版

DSP 版主要以算法開發(fā)人員為目標(biāo)受眾,可幫助他們在賽靈思 FPGA 中實施復(fù)雜的算法。由于工作流程高度自動化,因此用戶無需熟悉 HDL。

在流程中,算法開發(fā)人員首先在 The MathWorks 推出的 MATLAB 軟件環(huán)境中創(chuàng)建算法和算法的行為模型,然后再在 MathWorks’ Simulink 產(chǎn)品中測試行為模型,在 MATLAB 和 Simulink 軟件之間迭代調(diào)試算法,直到算法行為達(dá)到預(yù)期為止。隨后,用戶則能用賽靈思 DSP 版來優(yōu)化和實施賽靈思 FPGA 算法。

算法開發(fā)人員可在 DSP 版中用 System Generator 來取代構(gòu)成所有、大部分或部分算法的行為模塊。這些模塊包含了賽靈思 CORE Generator 庫中的優(yōu)化 IP,也就是說用戶也能通過定制黑盒子用自己的HDL來取代所有或部分模塊。如果用戶在MATLAB軟件中創(chuàng)建了定制算法但沒有算法的 VHDL 表達(dá),那么算法開發(fā)人員可用 AccelDSP 綜合工具自動將定制算法綜合到 VHDL 中,并創(chuàng)建新的 System Generator 模塊。該模塊可用 System Generator設(shè)計中的其他模塊來替代。System Generator 中的所有算法模塊被填充后,用戶按下按鈕,System Generator 就能自動運行 ISE 軟件的放置和布線工具,讓工具自己去實施 FPGA 算法表達(dá)。這樣,算法開發(fā)人員只需幾分鐘就能在賽靈思 FPGA中實施算法,并了解算法在真實硬件上的工作情況。

DSP 版可鏈接至 Simulink 軟件,這使算法開發(fā)人員能夠在 Simulink 和 MATLAB 環(huán)境中重復(fù)使用已開發(fā)的測試基準(zhǔn)來測試其算法,從而確保硬件算法和軟件算法的版本行為一致。此外,算法開發(fā)人員還能結(jié)合使用 DSP 版及 Simulink 和 MATLAB 軟件來執(zhí)行協(xié)同仿真任務(wù),同時還能對算法進(jìn)行故障排除和修改,以實現(xiàn)最佳的性能與功能。例如,如果算法開發(fā)人員在開發(fā)過程中發(fā)現(xiàn)眾多行為模塊之一需要調(diào)整,則可在 FPGA 中運行已知狀態(tài)良好的模塊,以便通過對故障模塊的反復(fù)調(diào)節(jié)測試迭代來加速驗證工作。硬件協(xié)同仿真的運行速度比純軟件仿真加快了 1,000 倍;而且算法越復(fù)雜,硬件仿真相對于軟件仿真的加速就越明顯。

在 ISE 設(shè)計套件 11.1 軟件中,System Generator 工具可運行在 Linux 與 Microsoft Windows 上。

系統(tǒng)版

系統(tǒng)版提供了賽靈思產(chǎn)品旗下的所有工具,適用于賽靈思器件的各類開發(fā)人員和開發(fā)團(tuán)隊。嵌入式版包含邏輯版加 EDK,DSP 版包含邏輯版和賽靈思 DSP Bundle,而系統(tǒng)版則包括邏輯版加 EDK 再加上賽靈思 DSP Bundle。

系統(tǒng)版流程中的所有工具均包括以上所述的全部 ISE 設(shè)計套件 11.1 軟件更新,并提高了邏輯、嵌入式以及 DSP 工具流程之間的互操作性。

WebPACK工具

除了推出 ISE 設(shè)計套件 11.1 軟件的不同新配置版本外,賽靈思還更新了可供免費下載的ISE WebPACK 工具。在 ISE WebPACK 的 10.1 版本中提供了 PlanAhead 的限制版,而 ISE 11.1 WebPACK 工具則包括 PlanAhead(參見邏輯版章節(jié)的相關(guān)介紹)完整版的所有實用工具,但僅支持有限數(shù)量的器件。

獨立工具

賽靈思目前正為客戶提供能夠充分滿足其各種需求的 ISE 軟件的各種新型配置版本。一些客戶可能希望在現(xiàn)有流程版本的基礎(chǔ)上再額外購買某些工具的許可證,因而除了推出邏輯版、嵌入式版、DSP 版以及系統(tǒng)版的配置版本之外,客戶還能將 SDK、ChipScope Pro 分析器、EDK 工具及賽靈思 DSP Tools Bundle(包括 System Generator 加 AccelDSP 綜合工具)作為獨立工具單獨購買其許可證。

SDK 版本只包括嵌入式軟件工具,主要面向開展嵌入式應(yīng)用開發(fā)、建模和調(diào)試的設(shè)計團(tuán)隊成員。希望針對其設(shè)計進(jìn)行一些嵌入式軟件開發(fā)的 DSP 版客戶也會發(fā)現(xiàn) SDK 非常實用,并能夠充分發(fā)揮 ISE 設(shè)計套件 11.1 軟件將 System Generator 和 SDK 相集成的顯著優(yōu)勢。作為獨立工具的SDK不包括任何FPGA邏輯實施或仿真工具,因此對硬盤占用很少。

例如,如果用戶希望向其設(shè)計流程添加嵌入式應(yīng)用開發(fā)功能,那么他們可將 EDK 作為獨立工具購買。同樣,如果他們希望向設(shè)計流程添加 DSP 算法開發(fā),也可單獨購買賽靈思 DSP Tools Bundle 的許可證。

ISE 設(shè)計套件 的許可證

賽靈思推出的 ISE 11.1 設(shè)計套件 擁有全新的工具許可管理方案。在本版本產(chǎn)品發(fā)布之前,賽靈思工具的許可管理主要采取基于用戶的方式,即每名用戶都需要一個許可證才能使用工具,任何工具都不提供流動許可證。

從 ISE 設(shè)計套件 11.1 軟件開始,賽靈思將以兩種配置方式提供工具:節(jié)點鎖定式,即在單臺計算機上鎖定許可證;以及流動式,即許可證駐留于客戶的網(wǎng)絡(luò)服務(wù)器上。節(jié)點鎖定式使客戶能夠?qū)⑷魏钨愳`思工具的許可證下載到特定的工作站。多個用戶能夠共享使用運行在該工作站上的賽靈思軟件。流動許可證使用戶能將單個許可證下載到其服務(wù)器上,以使設(shè)計人員無論位于全球任何位置都能同時使用該許可證。賽靈思也以節(jié)點鎖定和流動配置方式提供獨立工具的許可證。請參見表 1。

表 1:新工具流程配置的特性

|

特性 |

ISE WebPACK |

邏輯版 |

嵌入式版 |

DSP 版 |

系統(tǒng)版 |

|

ISE Foundation with ISE Simulator (ISim) |

√ |

√ |

√ |

√ |

√ |

|

PlanAhead Design 與 Analysis Tool |

√ |

√ |

√ |

√ |

√ |

|

ChipScope Pro 與 ChipScope Pro Serial I/O Toolkit |

|

√ |

√ |

√ |

√ |

|

嵌入式開發(fā)套件 (EDK) |

|

|

√ |

|

√ |

|

軟件開發(fā)套件 (SDK) |

|

|

√ |

|

√ |

|

賽靈思 DSP Bundle 包括 System Generator for DSP 以及 AccelDSP Synthesis Tool |

|

|

|

√ |

√ |

結(jié)論

為了更好地適應(yīng)客戶不同技能水平的需要,幫助客戶用賽靈思 FPGA 目標(biāo)設(shè)計平臺開展技術(shù)創(chuàng)新,賽靈思在精煉設(shè)計方法方面邁出了一大步。ISE 設(shè)計套件 11.1 軟件可提供四種最新的工具流程配置,能夠充分滿足邏輯設(shè)計人員、嵌入式系統(tǒng)開發(fā)人員、DSP 算法開發(fā)人員以及系統(tǒng)集成商的各種需求。

修改記錄

下表顯示了本文件的修改記錄:

免責(zé)聲明

本文向您透露的信息(以下簡稱“信息”)為最終版,不再更改,也不提供任何明示或暗示的擔(dān)保。請恕賽靈思就您對本信息的使用不承擔(dān)任何責(zé)任。您應(yīng)負(fù)責(zé)獲得使用本信息所需的權(quán)利。賽靈思保留在不另行通知的情況下隨時自行對本信息進(jìn)行更改的權(quán)利。對于本信息中所含任何可能錯誤,賽靈思概不負(fù)責(zé)修改,也不負(fù)責(zé)向您通知任何更改或更新情況。賽靈思明確發(fā)布免責(zé)聲明,概不承擔(dān)與本信息相關(guān)的任何技術(shù)支持或協(xié)助責(zé)任。對于本信息的任何商用性和特定目的的適用性,賽靈思不做任何其他明示、暗示或法定擔(dān)保,也不確保本信息不侵犯第三方權(quán)利。