主要介紹作為從設(shè)備如何根據(jù)PCI總線協(xié)議設(shè)計(jì)PCI總線接口電路,從而實(shí)現(xiàn)基于PCI總線的GP-IB接口電路設(shè)計(jì),重點(diǎn)闡述PCI總線接口狀態(tài)機(jī)的設(shè)計(jì)。

前言

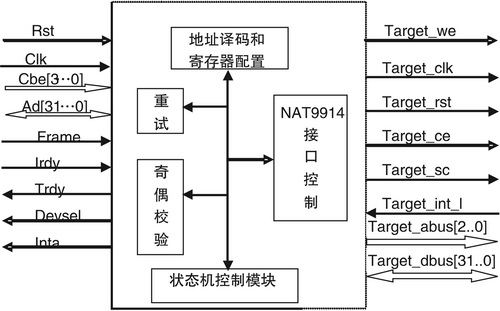

基于PCI總線的GP-IB接口電路框圖如圖1所示,工控機(jī)采用PCI-104堆棧結(jié)構(gòu),通過(guò)PCI總線和EPLD相連,數(shù)據(jù)總線為32bit,傳輸速率為33MHz。EPLD完成PCI總線接口電路的設(shè)計(jì)和NAT9914接口芯片的控制,通過(guò)驅(qū)動(dòng)芯片75160和75162完成GP-IB的接口通信。在此重點(diǎn)介紹EPLD內(nèi)部電路設(shè)計(jì)。

圖1 GP-IB接口電路結(jié)構(gòu)框圖

EPLD內(nèi)部電路設(shè)計(jì)

PCI局部總線很復(fù)雜,PCI局部總線也在不斷的發(fā)展中,現(xiàn)在已經(jīng)衍生有CPCI、PCI EXPRESS等總線標(biāo)準(zhǔn)。PCI局部總線定義的功能很強(qiáng)大,當(dāng)然如果需要將所有的PCI局部總線的要求都能實(shí)現(xiàn),購(gòu)買PCI局部總線的專用集成電路或IP核是最佳選擇,因?yàn)镻CI局部總線的硬件設(shè)計(jì)過(guò)于龐大,全部實(shí)現(xiàn)有一定的難度。如果設(shè)備只是作為從設(shè)備,根據(jù)設(shè)計(jì)要求實(shí)現(xiàn)起來(lái)也不是很復(fù)雜,很多功能如仲裁、邊界掃描及錯(cuò)誤報(bào)告等功能就可以不用實(shí)現(xiàn),甚至像奇偶校驗(yàn)、重試、突發(fā)傳輸?shù)裙δ芤部梢圆挥脤?shí)現(xiàn)。

根據(jù)GP-IB接口卡的功能,本文主要介紹在EPLD中實(shí)現(xiàn)PCI總線接口電路的設(shè)計(jì),并且能夠正確操作GP-IB總線協(xié)議的控制芯片NAT9914。EPLD的容量較小,我們采用XILINX公司的XC95288XL器件,只有288個(gè)宏單元,經(jīng)過(guò)設(shè)計(jì)優(yōu)化,最終成功裝載。其實(shí)現(xiàn)原理框圖如圖2所示。

圖2 EPLD內(nèi)部電路框圖

PCI接口信號(hào)設(shè)計(jì)

設(shè)計(jì)PCI接口信號(hào)很關(guān)鍵,PCI總線規(guī)范定義的信號(hào)很多,在設(shè)計(jì)過(guò)程中必須有所取舍。下面按照PCI總線規(guī)范的要求,根據(jù)設(shè)計(jì)電路的實(shí)際需求,設(shè)計(jì)如下接口信號(hào):

Rst : 上電復(fù)位信號(hào),低電平有效。

Clk : 時(shí)鐘信號(hào)33MHz。

Cbe[3..0] : 命令、字節(jié)使能信號(hào)。

Ad[31..0] : 地址、數(shù)據(jù)多路復(fù)用的三態(tài)輸入/輸出信號(hào)。

Frame : 幀周期信號(hào),由主設(shè)備驅(qū)動(dòng),表示當(dāng)前主設(shè)備一次交易的開(kāi)始和持續(xù)時(shí)間。

Irdy : 主設(shè)備準(zhǔn)備好信號(hào)。

Trdy : 從設(shè)備數(shù)據(jù)準(zhǔn)備好信號(hào)。

Devsel : 從設(shè)備被選中響應(yīng)信號(hào)。

Inta :從設(shè)備中斷請(qǐng)求,低有效。

在設(shè)計(jì)時(shí)舍棄的信號(hào)有:Par、Stop、Perr、Serr、Req、Gnt。

GP-IB接口芯片控制信號(hào)設(shè)計(jì)

根據(jù)電路要求,設(shè)計(jì)如下接口信號(hào),用來(lái)完成對(duì)NAT9914和驅(qū)動(dòng)芯片的控制,實(shí)現(xiàn)PCI到GP-IB接口的轉(zhuǎn)換。

Target_clk: GP-IB接口控制芯片時(shí)鐘,本方案設(shè)計(jì)為33MHz時(shí)鐘的8分頻。

Target_rst:復(fù)位脈沖信號(hào),低電平復(fù)位。

Target_ce: 讀寫使能,高電平為讀,低電平為寫。

Target_sc:標(biāo)識(shí)GP-IB接口卡作為控者,還是作為普通器件。

Target_we:寫使能控制,低電平有效。

Target_int_l:控制芯片中斷輸出,低電平有效。

Target_abus:有效地址輸出。

Target_dbus:三態(tài)數(shù)據(jù)輸入/輸出總線。

電路優(yōu)化設(shè)計(jì)

圖2給出了PCI總線接口電路的原理框圖,由于EPLD容量較小,在設(shè)計(jì)時(shí)必須盡量減少不必要的電路設(shè)計(jì),并對(duì)電路設(shè)計(jì)進(jìn)行優(yōu)化,下面給出各電路模塊的功能設(shè)計(jì):

譯碼電路

PCI總線命令編碼方式有12種,在本設(shè)計(jì)中我們只實(shí)現(xiàn)配置讀、配置寫、存儲(chǔ)器讀和存儲(chǔ)器寫四種編碼交易類型。譯碼功能電路工作在地址周期,包括命令譯碼、地址譯碼和命令/地址鎖存等三項(xiàng)功能。在Frame變低的第一個(gè)時(shí)鐘周期內(nèi),譯碼電路對(duì)來(lái)自主設(shè)備的命令Cbe[3..0]進(jìn)行譯碼,并向狀態(tài)機(jī)控制模塊發(fā)出是配置讀寫還是存儲(chǔ)器讀寫命令,同時(shí)鎖存地址。

配置寄存器

在PCI規(guī)范中,配置空間是一個(gè)容量為256字節(jié)并具有特定記錄結(jié)構(gòu)或模型的地址空間,該空間又分為頭標(biāo)區(qū)和設(shè)備有關(guān)區(qū)兩部分。在配置寄存器中不用的寄存器當(dāng)CPU讀的時(shí)候,將默認(rèn)為零。

重試

GP-IB控制芯片寄存器響應(yīng)完全能夠滿足PCI規(guī)范的要求,不需要進(jìn)行重試,這部分功能不再實(shí)現(xiàn)。

奇偶校驗(yàn)

在BIOS中可以對(duì)奇偶校驗(yàn)進(jìn)行屏蔽和開(kāi)放,為了減少設(shè)計(jì)的復(fù)雜性,奇偶校驗(yàn)功能在EPLD中沒(méi)有實(shí)現(xiàn),在BIOS中進(jìn)行了屏蔽。

NAT9914接口控制電路

NAT9914接口控制電路主要完成內(nèi)部總線到外設(shè)的時(shí)序控制。GP-IB總線接口采用的是負(fù)邏輯電平設(shè)計(jì),考慮到EPLD的容量有限,在設(shè)計(jì)時(shí)數(shù)據(jù)傳輸不支持DMA模式,只支持單周期CPU讀寫。由于CPU讀數(shù)據(jù)時(shí)延遲較大,在對(duì)PCI狀態(tài)機(jī)設(shè)計(jì)時(shí)必須進(jìn)行讀延遲等待。

狀態(tài)機(jī)的設(shè)計(jì)與實(shí)現(xiàn)

狀態(tài)機(jī)的設(shè)計(jì)是整個(gè)設(shè)計(jì)中的核心部分,它主要用來(lái)控制從設(shè)備和PCI總線的時(shí)序。在本設(shè)計(jì)方案中,配置過(guò)程的完成和存儲(chǔ)器的讀寫都是由狀態(tài)機(jī)來(lái)完成的。由于EPLD的容量有限,GP-IB接口芯片的讀寫速度比較慢,在設(shè)計(jì)狀態(tài)機(jī)時(shí),不支持CPU的猝發(fā)操作。表1給出了狀態(tài)機(jī)的狀態(tài)名、狀態(tài)變量和說(shuō)明,圖3給出了狀態(tài)機(jī)的流程圖。

圖3 狀態(tài)機(jī)設(shè)計(jì)流程圖

下面根據(jù)狀態(tài)機(jī)的流程圖給出讀、寫操作時(shí)序分析與設(shè)計(jì)要點(diǎn):

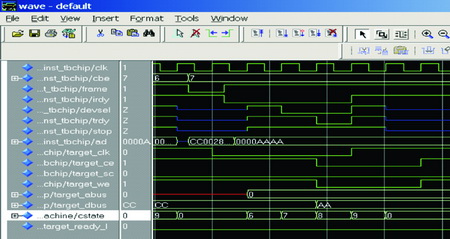

PCI規(guī)范中定義了三種讀寫操作,即Memory和I/O讀寫及配置讀寫。本方案不支持I/O讀寫,只支持Memory和配置的讀寫,下面給出Memory映射方式的單周期仿真讀寫時(shí)序。

存儲(chǔ)器寫操作

存儲(chǔ)器單周期寫操作時(shí)序如圖4所示,當(dāng)frame為低電平時(shí)啟動(dòng)讀寫操作,同時(shí)給出要寫的目標(biāo)地址ad[31..0]和命令cbe[3..0]=7,cbe等于7表示寫寄存器,從設(shè)備鎖存命令和地址到緩沖區(qū)。在第2個(gè)clk,主設(shè)備將irdy變低,同時(shí)給出數(shù)據(jù),狀態(tài)機(jī)運(yùn)行到6,鎖存數(shù)據(jù)給緩沖區(qū),trdy、devsel由高阻變?yōu)楦唠娖健T诘?個(gè)clk,devsel變低,給出主設(shè)備應(yīng)答信號(hào),表示從設(shè)備已經(jīng)響應(yīng)請(qǐng)求,狀態(tài)機(jī)運(yùn)行到7。根據(jù)寫操作,target_we、target_ce變低,并對(duì)地址進(jìn)行譯碼,放在地址總線上,同時(shí)驅(qū)動(dòng)數(shù)據(jù)總線,表示在對(duì)控制芯片進(jìn)行寫操作。在第4個(gè)clk,檢測(cè)到目標(biāo)設(shè)備的target_ready_l為低電平,表示從設(shè)備已經(jīng)做好接受數(shù)據(jù)的準(zhǔn)備,狀態(tài)機(jī)運(yùn)行到8,將trdy變低。在第5個(gè)clk,狀態(tài)機(jī)運(yùn)行到9,trdy變高,同時(shí)主設(shè)備將驅(qū)動(dòng)irdy變高,表示一個(gè)寫周期結(jié)束。狀態(tài)機(jī)運(yùn)行到初始狀態(tài),等待下一次操作。target_ce、target_we將延遲變高,結(jié)束控制芯片寫周期。

圖4 存儲(chǔ)器寫周期時(shí)序

存儲(chǔ)器讀操作

存儲(chǔ)器單周期讀操作時(shí)序如圖5所示,當(dāng)frame為低電平時(shí)啟動(dòng)讀寫操作,同時(shí)給出要寫的目標(biāo)地址ad[31..0]和命令cbe[3..0]=6,從設(shè)備鎖存該命令和地址。在第2個(gè)clk,狀態(tài)機(jī)運(yùn)行到6,進(jìn)入讀寫等待狀態(tài),主設(shè)備將frame變高,表示單周期模式,trdy、devsel、由高阻變?yōu)楦唠娖健T诘?個(gè)clk,狀態(tài)機(jī)運(yùn)行到7,并給出應(yīng)答信號(hào)devsel,檢測(cè)到target_ready_l為高電平,狀態(tài)機(jī)進(jìn)入等待狀態(tài),直到為低電平,然后運(yùn)行到讀等待狀態(tài)4。在狀態(tài)機(jī)8,trdy變低,從設(shè)備將讀數(shù)據(jù)放在ad[31..0]總線上。在狀態(tài)機(jī)9,trdy變高,devsel變高,同時(shí)主設(shè)備將irdy變高,結(jié)束單周期讀操作。devsel、trdy回到高阻狀態(tài),狀態(tài)機(jī)運(yùn)行到初始狀態(tài),準(zhǔn)備下次操作。

圖5 存儲(chǔ)器讀周期時(shí)序

結(jié)語(yǔ)

本設(shè)計(jì)占用芯片的資源少,可移植性強(qiáng),根據(jù)設(shè)備不同的需求可以進(jìn)行設(shè)計(jì)更改,在很多測(cè)試儀器中都得到了廣泛的應(yīng)用。

參考文獻(xiàn):

1.李貴山、陳金鵬,PCI局部總線及其應(yīng)用,西安電子科技大學(xué)出版社,2003

2. 候伯亨、顧新,VHDL硬件描述語(yǔ)言與電路設(shè)計(jì),西安電子科技大學(xué)出版社,1997