摘要:門光子計(jì)數(shù)器是量子光學(xué)實(shí)驗(yàn)中單光子探測常用的數(shù)據(jù)采集設(shè)備,用于收集單光子探測器探測到的單個(gè)光子信號(hào)。由于不同的場合需要用到不同的計(jì)數(shù)模式,商用的計(jì)數(shù)器往往難以滿足具體的需求,或者造成采集效率低下。系統(tǒng)采用的是一種基于MicroBlaze系統(tǒng)FSL總線的可擴(kuò)展計(jì)數(shù)器設(shè)計(jì)架構(gòu),該架構(gòu)能夠靈活的添加不同的計(jì)數(shù)功能,并通過統(tǒng)一的FSL總線和Microblaze CPU與PC通信。在該架構(gòu)的基礎(chǔ)上實(shí)現(xiàn)了針對(duì)量子單自旋調(diào)控實(shí)驗(yàn)中常用的計(jì)數(shù)模式。系統(tǒng)所采用的設(shè)計(jì)和實(shí)現(xiàn)方式可以推廣到其他光子計(jì)數(shù)需求中,并具有較低的設(shè)計(jì)和生產(chǎn)成本。

0 引言

光學(xué)領(lǐng)域尤其是量子光學(xué)領(lǐng)域的實(shí)驗(yàn)常常需要進(jìn)行單個(gè)相干光子的探測用于實(shí)現(xiàn)實(shí)驗(yàn)數(shù)據(jù)的采集。一般常用的配置是一個(gè)單光子探測器加上一個(gè)門光子計(jì)數(shù)器,其前端的單光子探測器用來收集光子信號(hào),每探測到一個(gè)光子產(chǎn)生一個(gè)TTL脈沖,后端的門光子計(jì)數(shù)器用來記錄該TTL上升沿?cái)?shù)目并且與PC等其他器件通信或者同步。APD的工作方式相對(duì)簡單,而門光子計(jì)數(shù)器則由于具體實(shí)驗(yàn)需求不同而要求不同的工作方式,很難有一種通用的計(jì)數(shù)模式能夠滿足各種情況的需求。由于成本限制,功能固定的計(jì)數(shù)器往往因?yàn)闆]有廣闊的市場而造成價(jià)格很高。另一方面,工業(yè)和科研界購買的商用計(jì)數(shù)器往往無法滿足自己的具體需求而導(dǎo)致工作效率低下,甚至無法滿足要求。

所謂門光子計(jì)數(shù)器就是針對(duì)單自旋量子調(diào)控實(shí)驗(yàn)研究中對(duì)單個(gè)光子探測的需求所研制的。單自旋量子調(diào)控是對(duì)晶體中的缺陷,如量子點(diǎn)和金剛石色心進(jìn)行控制,其信號(hào)讀出一般是通過自旋發(fā)生的單個(gè)光子進(jìn)行探測實(shí)現(xiàn)的。在此類實(shí)驗(yàn)中常用的技術(shù)有三種:門光子計(jì)數(shù)、定時(shí)計(jì)數(shù)和相關(guān)函數(shù)測量。文中所述的系統(tǒng)建立了一種可擴(kuò)展的通信和控制架構(gòu)能夠添加不同方式的計(jì)數(shù)功能。

1 系統(tǒng)結(jié)構(gòu)設(shè)計(jì)

整體系統(tǒng)結(jié)構(gòu)示意圖如圖1所示,通過PC機(jī)的以太網(wǎng)口實(shí)現(xiàn)與計(jì)數(shù)系統(tǒng)的數(shù)據(jù)通訊與命令傳輸,PC機(jī)將工作模式選擇等命令通過網(wǎng)口向系統(tǒng)發(fā)送,而系統(tǒng)將在不同模式下的計(jì)數(shù)值及計(jì)數(shù)狀態(tài)等數(shù)據(jù)通過網(wǎng)口發(fā)送到PC機(jī),交由PC機(jī)對(duì)數(shù)據(jù)進(jìn)行處理。系統(tǒng)的主芯片采用Xilinx的SPARTAN 3E系列的XC3S500E。系統(tǒng)的光子計(jì)數(shù)輸入由兩個(gè)BNC接口引入,這兩個(gè)接口可以由FPGA進(jìn)行配置,使光子計(jì)數(shù)器以不同的模式進(jìn)行工作。系統(tǒng)的固件燒寫在FLASH芯片內(nèi),SDRAM提供了大容量存儲(chǔ)空間,用于運(yùn)行時(shí)裝載Microblaze軟核代碼、計(jì)數(shù)應(yīng)用代碼以及存儲(chǔ)計(jì)數(shù)的數(shù)據(jù)。

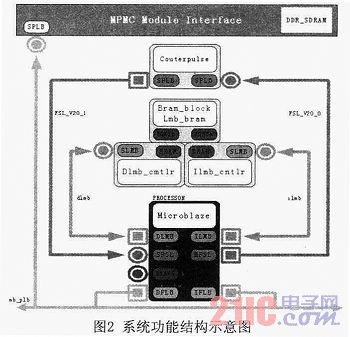

系統(tǒng)以FPGA為處理中心,實(shí)現(xiàn)各種工作模式,其功能框圖如圖2所示。功能模塊主要包括軟核Microblaze、對(duì)外部存儲(chǔ)器的接口MPMC、以及需要設(shè)計(jì)實(shí)現(xiàn)的Counterpulse IP核。在Counterpulse IP核與處理器軟核之間,采用了FSL總線進(jìn)行連接,實(shí)現(xiàn)由Microbalze對(duì)Counterpu-lse核的配置,以及由Counterpulse核到Microblaze的數(shù)據(jù)傳輸。

系統(tǒng)工作時(shí),由Microblaze軟核通過網(wǎng)口接收由PC機(jī)發(fā)送來的命令,根據(jù)命令,通過一路FSL總線對(duì)光子計(jì)數(shù)IP核進(jìn)行工作模式的選擇和配置。計(jì)數(shù)IP核對(duì)外部計(jì)數(shù)源進(jìn)行計(jì)數(shù),計(jì)數(shù)的結(jié)果和狀態(tài)數(shù)據(jù)通過另一路FSL總線發(fā)送到Microblaze軟核,由Microblaze軟核將該數(shù)據(jù)在DDRRAM內(nèi)進(jìn)行緩沖,并通過網(wǎng)口將這些數(shù)據(jù)最終發(fā)送給PC機(jī),由PC機(jī)進(jìn)行分析處理。

系統(tǒng)有三種工作模式:模式一:使能計(jì)數(shù),使能信號(hào)有效時(shí)(高電平有效),對(duì)光子計(jì)數(shù)輸入的計(jì)數(shù)脈沖信號(hào)進(jìn)行計(jì)數(shù);模式二:定周期計(jì)數(shù),根據(jù)設(shè)定的計(jì)數(shù)周期,對(duì)光子計(jì)數(shù)輸入的計(jì)數(shù)脈沖信號(hào)進(jìn)行計(jì)數(shù);模式三:啟動(dòng)和停止信號(hào)分開的計(jì)時(shí),根據(jù)輸入的計(jì)數(shù)啟動(dòng)信號(hào)和計(jì)數(shù)停止信號(hào)(均為上升沿有效),進(jìn)行以系統(tǒng)基頻為基準(zhǔn)的計(jì)時(shí),以實(shí)現(xiàn)函數(shù)測量。

2 系統(tǒng)設(shè)計(jì)實(shí)現(xiàn)

2.1 系統(tǒng)硬件框圖

計(jì)數(shù)系統(tǒng)硬件結(jié)構(gòu)如圖3所示,由FPGA、64MB的DDR存儲(chǔ)器、16MB的FLASH存儲(chǔ)器和10M/100M以太物理層(PHY)等組成。系統(tǒng)工作時(shí),由PC機(jī)通過網(wǎng)口發(fā)送命令到FPGA,F(xiàn)PGA內(nèi)部的Microblaze軟核配置計(jì)數(shù)IP核的工作模式,由FPGA通過兩路BNC接口對(duì)外部計(jì)數(shù)源進(jìn)行計(jì)數(shù),并將數(shù)據(jù)在DDRRAM內(nèi)進(jìn)行緩沖,最終將這些數(shù)據(jù)通過網(wǎng)口發(fā)送到PC機(jī)。

2.2 主要元器件介紹

2.2.1 FPGA芯片及其配置芯片選用

FPGA選用Xilinx公司的Spartan-3E系列XC3S500E,采用先進(jìn)的90nm制造工藝生產(chǎn),其器件密度為50萬門。Spartan3系列的FPGA是Xilinx公司專門針對(duì)大容量、低成本需求的電子設(shè)計(jì)而開發(fā)的,可支持多種電平的I/O標(biāo)準(zhǔn);含有豐富的邏輯資源。XC3S500E具有360kbits的塊RAM、73kbits的分布式RAM、10476個(gè)邏輯單元、20個(gè)18×18的乘法器和4個(gè)DCM時(shí)鐘管理模塊。

FPGA的配置芯片選用的是Xilinx公司的在系統(tǒng)可編程配置芯片XCF04S,該芯片可為XC3S500E提供易于使用、成本低且可重復(fù)編程的配置數(shù)據(jù)存貯方法,該芯片支持IEEE1149.1標(biāo)準(zhǔn)的JTAG邊界掃描測試和編程。在本系統(tǒng)設(shè)計(jì)中,XCF04S主要存放用于引導(dǎo)Microblaze軟核及應(yīng)用程序的引導(dǎo)代碼。

2.2.2 存儲(chǔ)芯片

系統(tǒng)使用的RAM是Micron Technology公司的DDRSDRAM(MT46V32M16),是一片容量為512Mbit(32Mx16)的16位總線寬度存儲(chǔ)芯片,用于上電后加載Microblaze軟核代碼和應(yīng)用程序代碼,以及對(duì)計(jì)數(shù)數(shù)據(jù)進(jìn)行緩沖。FLASH芯片是Intel StrataFlash parallel NORFlash,型號(hào)為28F256J3,存儲(chǔ)密度為256Mbit,在本系統(tǒng)中用于保存Microblaze軟核代碼和應(yīng)用程序代碼。

3 功能設(shè)計(jì)實(shí)現(xiàn)

3.1 基于EDK的FPGA軟核Microblaze的應(yīng)用設(shè)計(jì)實(shí)現(xiàn)

系統(tǒng)設(shè)計(jì)工具主要采用Xilinx公司的嵌入式開發(fā)套件EDK,它是用于設(shè)計(jì)嵌入式處理系統(tǒng)的集成解決方案。它包括搭建硬件平臺(tái)的XPS和進(jìn)行軟件配置的SDK。

Microblaze是Xilinx公司推出的32位軟處理器核,支持CoreConnect總線的標(biāo)準(zhǔn)外設(shè)集合。MicroBlaze處理器運(yùn)行在150MHz時(shí)鐘下,可提供125 D-MIPS的性能,這種高效的軟核在本系統(tǒng)中可用于實(shí)現(xiàn)處理器功能,實(shí)現(xiàn)對(duì)計(jì)數(shù)IP核的配置,以及支撐Xilinx的clockgenerator、Et-hernet等IP核。系統(tǒng)對(duì)計(jì)數(shù)器的實(shí)現(xiàn)采用Verilog語言將計(jì)數(shù)功能編寫為IP核,將其通過FSL總線掛在Microblaze軟核上,以實(shí)現(xiàn)計(jì)數(shù)功能。

3.2 通訊協(xié)議

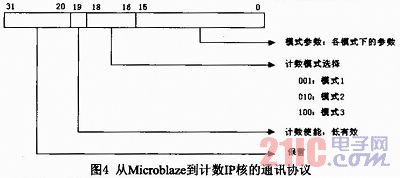

Microblaze到計(jì)數(shù)IP核之間的通訊數(shù)據(jù)定義如下:

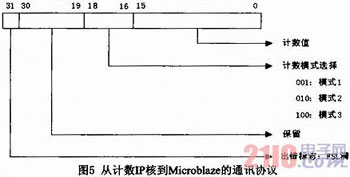

計(jì)數(shù)IP核到Microblaze之間的通訊數(shù)據(jù)定義如下:

3.3 計(jì)數(shù)IP核的設(shè)計(jì)實(shí)現(xiàn)

3.3.1 計(jì)數(shù)IP核的結(jié)構(gòu)

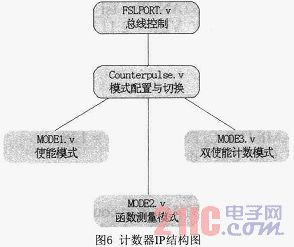

計(jì)數(shù)IP核采用verilog硬件語言編寫,其結(jié)構(gòu)如圖6所示,頂層文件counterpulse3對(duì)接口進(jìn)行配置,并根據(jù)FSL總線上的命令參數(shù)選擇工作模式,pulsecount1、pulsecount2和pulsecount3分別是3種工作模式的代碼實(shí)現(xiàn),fsloprt是與FSL進(jìn)行接口的代碼。

3.3.2 與FSL總線接口

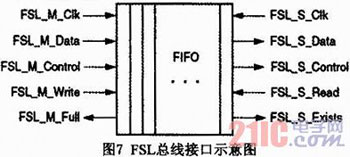

fslopn.v的代碼完成與FSL總線接口功能。FSL總線是單向點(diǎn)對(duì)點(diǎn)的通道,它用于完成任意FPGA中兩個(gè)模塊的快速通訊。FSL總線是基于FIFO的,基于非共享的無仲裁通信機(jī)制,它的深度是可以設(shè)置的,最大可以到8k,具備高速的通信性能,其結(jié)構(gòu)如圖7所示。

由于FSL總線是單向的,所以系統(tǒng)中采用了兩條FSL總線,實(shí)現(xiàn)Mieroblaze到計(jì)數(shù)IP核之間的雙向通訊,計(jì)數(shù)IP核在面對(duì)兩條FSL總線時(shí),擔(dān)當(dāng)?shù)姆謩e是MASTER(主)和SLAVE(從)兩種角色。因此,fsloprt.v的代碼應(yīng)該同時(shí)滿足與FSL總線接口的讀和寫時(shí)序。讀寫時(shí)序如圖8和圖9所示。

3.4 計(jì)數(shù)IP核和FSL總線的在EDK中的連接實(shí)現(xiàn)

為了能使用FSL總線,首先應(yīng)該在XPS圖形界面中對(duì)Microblaze進(jìn)行配置,在Buses中將Number of FSL Links設(shè)置為1。再在IP Catalog中將FSL總線加入到工程中兩次。

在計(jì)數(shù)IP核編寫后并綜合通過后,將該IP核導(dǎo)入到XPS工程中。

在XPS中,分別對(duì)Microblaze和計(jì)數(shù)IP核的MFSL和SFSL進(jìn)行連接,將Microblaze的MFSL端連接到計(jì)數(shù)IP核的SFSL端,反之將計(jì)數(shù)IP核的MFSL端連接到Microblaze的SFSL端。并在system.mhs中進(jìn)行如下配置:

由于從計(jì)數(shù)IP到Microblaze方向數(shù)據(jù)量較大,所以對(duì)FSL總線的深度進(jìn)行了配置,如上述代碼中,PARAMETERC_FSL_DEPTH=128,被配置為128級(jí)深度。

4 結(jié)論

在系統(tǒng)的設(shè)計(jì)中,光子計(jì)數(shù)IP核與Mieroblaze軟核之間通過FSL總線進(jìn)行通訊,并且對(duì)FSL總線上的FIFO緩沖進(jìn)行了深度擴(kuò)充,大大增強(qiáng)了光計(jì)數(shù)數(shù)據(jù)的傳輸可靠性。由于系統(tǒng)將門光子計(jì)數(shù)的三種模式,以IP核的方式實(shí)現(xiàn),相對(duì)于市場上商用的計(jì)數(shù)器來說,實(shí)現(xiàn)方式靈活,易于配置和擴(kuò)展,這種方式為門光子其他可能潛在的計(jì)數(shù)需求留下了擴(kuò)展的基礎(chǔ),并具有較低的設(shè)計(jì)和生產(chǎn)成本。

作者:馬正源 徐南陽 來源:現(xiàn)代電子技術(shù)