引言

晶體的主要組成部分是二氧化硅,俗稱(chēng)石英。石英具有非凡的機(jī)械和壓電特性,使得從19世紀(jì)40年代中期以來(lái)一直作為基本的時(shí)鐘器件。如今,只要需要時(shí)鐘的地方,工程師首先想到的就是晶體,但是隨著應(yīng)用的不斷深入,晶體的一些固有的缺陷也隨之暴露出來(lái)。如今新技術(shù)不斷涌現(xiàn),并帶來(lái)很大的變化。

晶體的特點(diǎn)及參數(shù)

封裝

晶體的封裝如圖1所示,有三部分組成:金屬上蓋,帶有電極的石英片和陶瓷底座。一般來(lái)說(shuō),還需要向密封殼內(nèi)充氮?dú)狻?/span>

硅頻率控制器-晶體替代市場(chǎng)的寵兒" src="http://files.chinaaet.com/images/20110823/f606da54-2aed-42a0-a2b4-e158095b0360.jpg" />

圖1 晶體封裝圖

現(xiàn)在幾乎所有的陶瓷密封裝都是由三家日本公司提供,但是由于日本地震和海嘯,產(chǎn)量嚴(yán)重受影響。今后很長(zhǎng)一段時(shí)間將難以滿(mǎn)足市場(chǎng)需求。

石英材料

石英以其固有的壓電特性成為晶體中的主要部分。但是它必須經(jīng)過(guò)切割打磨才能使用,由于其厚度非常薄,雖然采取了保護(hù)措施,但是其抗震性一直是大家所擔(dān)心的。

精度

所謂精度就是實(shí)際的時(shí)鐘頻率偏離標(biāo)準(zhǔn)時(shí)鐘頻率的程度。用公式表示為:

Error (PPM) = (Factual-Ftarget) / Ftarget * 10E6

Error:精度

Factual:實(shí)際頻率

Ftarget:標(biāo)準(zhǔn)頻率

PPM:百萬(wàn)分之一

在晶體的應(yīng)用中,有這幾個(gè)方面需要考慮:

1) 頻率公差:就是在通常的環(huán)境溫度下(25°C+/-5°C)實(shí)際頻率偏離標(biāo)準(zhǔn)頻率的值。

2) 頻率溫度特征:就是在整個(gè)溫度變化范圍內(nèi),實(shí)際頻率偏離標(biāo)準(zhǔn)頻率的值。現(xiàn)在通常有三種溫度范圍:0°C--70°C,-20°C--70°C和-40°C--85°C。

3) 老化:晶體的內(nèi)部特性隨著時(shí)間的推移發(fā)生變化引起的頻率的偏差,稱(chēng)為晶體的老化。一般來(lái)說(shuō),第一年晶體的精度受老化的影響為5PPM,以后每年大約為1-3PPM。如果一個(gè)產(chǎn)品的設(shè)計(jì)生命周期為10年,則老化帶來(lái)的頻率精度變化最高可達(dá)32PPM。

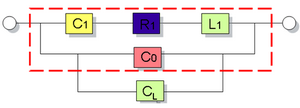

4)負(fù)載電容精度變化引起頻率的變化:這個(gè)因素往往容易被忽視。在晶體的應(yīng)用中有兩種工作模式,串行振蕩模式和并行振蕩模式。由于并行模式設(shè)計(jì)靈活并且有很高的輸出精度,現(xiàn)在已成為市場(chǎng)主流。 圖2是并行振蕩模式的等效電路圖:

圖2 并行振蕩模式等效電路圖

R1:動(dòng)態(tài)阻抗

C1:動(dòng)態(tài)電容

L1:動(dòng)態(tài)電感

C0:靜態(tài)電容

CL:負(fù)載電容

并行振蕩模式的頻率可根據(jù)以下公式:

FL=[1/2π√(L1*C1))]*√[1+C1/(C0+CL)]

其中[1/2π√(L1*C1))]是晶體串行振蕩模式的頻率

根據(jù)泰勒展開(kāi):

FL=[1/2π√(L1*C1)]*[1+C1/2(C0+CL)] (1)

從公式中可以看出,頻率與C0,C1和CL都有關(guān)。

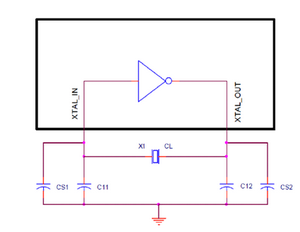

在基頻諧振中C1為10-30fF,一般取值為20fF。C0取值與晶體的尺寸有關(guān),一般取值為5pF。但是CL的計(jì)算與晶體外接電容和PCB設(shè)計(jì)和材料有關(guān)。下圖是參考電路圖

圖3 晶體外接負(fù)載電容示意圖

從上面電路中可得出:

1/(C11+CS1)+1/(C12+CS2)=1/(CL) (2)

其中C11,C12是外接電容,也就是線路設(shè)計(jì)中放在晶體兩邊接地的兩個(gè)電容。CS1和CS2是寄生電容,和PCB 電路板的走線,焊盤(pán)及芯片的管腳有關(guān)。一般為5-10pF(在本文的計(jì)算中可設(shè)為8pF)。對(duì)于C11和C12,沒(méi)有確定的值(15pF-30pF),這和實(shí)際設(shè)計(jì)有關(guān),例如取18pF。

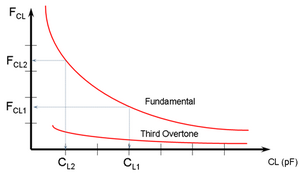

CL如有變化,并行振蕩模式的頻率也隨之變化,請(qǐng)看圖4

圖4 負(fù)載電容變化與頻率的關(guān)系

由公式(1)可得頻率變化為:

(FCL1-FCL2)/FCL1=C1/2 * [1/(C0+CL1)-1/(C0+C L2)] * 10E6 (3)

從公式(2)和公式(3)中可知C11和C12的精度將影響頻率的精度。具體數(shù)據(jù)如表1所示。其中參數(shù)的取值如前文:C1=20fF,C0=5pF,CS1=CS2=8pF,C11=C12=18pF。

表1 電容精度與頻率精度的關(guān)系

|

電容精度 |

CL1 |

CL2 |

影響頻率精度(PPM) |

|

0.50% |

12.955 |

13.045 |

3 |

|

1% |

12.910 |

13.090 |

6 |

|

5% |

12.550 |

13.450 |

28 |

|

10% |

12.100 |

13.900 |

56 |

|

20% |

11.200 |

14.800 |

112 |

在很多應(yīng)用場(chǎng)合,電容精度取5%,從上表可看出它對(duì)頻率精度的影響可達(dá)到28PPM。這在設(shè)計(jì)中容易被忽略的。

5) 其他因素:如回流焊接的影響,濕度的影響,大氣壓的影響等。這些因素影響不大,不再這里詳述。

晶體振蕩總的頻率精度就是上述五個(gè)方面之和。

硅頻率控制器(SFC)

SFC原理

由于石英材料及其振蕩原理的局限性,近年來(lái),人們不斷探索用新技術(shù)來(lái)替代它。如MEMS技術(shù),但是它的中心振蕩頻率不是很高(如16MHz)所以如果需要高的頻率輸出,必須經(jīng)過(guò)一級(jí)PLL, 增加了成本,相位噪音和功耗。

IDT在這一領(lǐng)域做了深入的研究,采用專(zhuān)利的CMOS諧波振蕩器(CHO),推出了全硅頻率控制器。它的核心是一個(gè)高頻的振蕩模塊,根據(jù)設(shè)置不同的分頻系數(shù)可得到不同的輸出頻率。這樣,既不需要石英做為振蕩源,也不需要PLL做倍頻。

SFC工作狀態(tài)需要電源而晶體不需要。但是,由于ASIC必須提供晶體起振電路,所以晶體也相應(yīng)地增加了ASIC的能耗。

硅頻率控制器(SFC)的參數(shù)

精度

硅頻率控制器的頻率公差在50PPM。-20-70°C頻率溫度特征是50PPM。硅頻率控制器不使用石英,所以沒(méi)有老化方面的問(wèn)題。精度只需考慮兩個(gè)方面即可。可參照以下表2中的例子。晶體精度的取值請(qǐng)參照前文的計(jì)算。

表2 兩類(lèi)產(chǎn)品的比較

|

晶體 |

|

SFC |

||

|

頻率公差 |

50ppm |

|

50ppm |

|

|

溫度特征 |

50ppm |

|

50ppm |

|

|

老化 |

32ppm/10yr |

|

|

|

|

負(fù)載電容變化 +/-5% |

28ppm |

|

|

|

|

其它 |

|

|

|

|

|

總共 |

160ppm |

|

100ppm |

|

從這個(gè)例子可以看出,雖然都是50PPM的頻率公差和溫度特征,計(jì)算出晶體的精度可達(dá)160PPM。而硅頻率控制器的精度是100PPM。

最簡(jiǎn)單的設(shè)計(jì)

硅頻率控制器不需要任何輔助器件即可工作。晶體必須外掛兩顆電容才能正常工作,這不但節(jié)約了成本,還節(jié)約了寶貴的空間,這符合產(chǎn)品小型化發(fā)展的趨勢(shì)。

超低供電電流

在工作狀況下,供電電流是1.9mA。靜態(tài)工作電流更是只有1uA。其它基于晶體和MEMS的產(chǎn)品是它的4-10倍。這對(duì)于手持設(shè)備更是一個(gè)福音。因?yàn)閷?duì)于相同的電池容量,低電流意味著更長(zhǎng)的使用時(shí)間,這越來(lái)越受到產(chǎn)品制造商的重視。

快速啟動(dòng)時(shí)間

標(biāo)準(zhǔn)啟動(dòng)時(shí)間是400uS。而晶體的啟動(dòng)時(shí)間有時(shí)競(jìng)達(dá)到10mS。更快的啟動(dòng)時(shí)間可以使產(chǎn)品從上電或待機(jī)狀態(tài)迅速進(jìn)入正常工作狀態(tài)。這也增強(qiáng)了產(chǎn)品的競(jìng)爭(zhēng)力,在市場(chǎng)上占有利的地位。

寬頻率輸出范圍

不需要PLL,硅頻率控制器可輸出4-50MHz。對(duì)于通用的頻率,如10M,14.31818M,19.44M,20M,25M,33M,33.3333M,40M,48M,50M等等可以直接訂購(gòu),對(duì)于不通用或者特殊頻率,可通過(guò)工廠設(shè)置輸出分頻系數(shù)得到。

更高的工作可靠性

現(xiàn)在時(shí)尚的產(chǎn)品總是被人們喜歡隨身攜帶,如掉在地上,被硬物碰到等小意外發(fā)生是不可避免的。這往往會(huì)造成晶體停振而使產(chǎn)品失效。硅頻率控制器由于沒(méi)有采用晶體,所以不會(huì)受到振動(dòng)和擠壓的影響。這對(duì)于產(chǎn)品的長(zhǎng)期穩(wěn)定性工作是非常重要的。而這也是設(shè)備制造商越來(lái)越喜歡它的原因之一。另外,硅頻率控制器沒(méi)有高阻抗的輸入 管腳,這樣更利于通過(guò)EMI的測(cè)試。

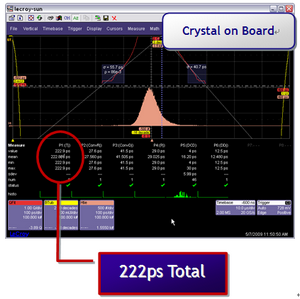

更好的抖動(dòng)指標(biāo)

下例是在SATA GEN2連接性能測(cè)試結(jié)果。從中可以看出硅頻率控制器的抖動(dòng)小于晶體的抖動(dòng)。

圖5 晶體抖動(dòng)指標(biāo)實(shí)測(cè)圖

圖6 硅頻率控制器SFC的抖動(dòng)指標(biāo)實(shí)測(cè)圖

塑殼封裝

硅頻率控制器的封裝采用成本更低的塑殼即可。而晶體必須采用陶瓷密封裝。所以硅頻率控制器的成本可以更低。并且塑殼封裝的資源非常豐富,不受到廠家供貨周期和數(shù)量的限制。

硅頻率控制器的尺寸通常是2.5*2*0.55mm。并會(huì)有更小的尺寸推出。眾所周知,小封裝的晶體會(huì)大幅度增加成本。但這對(duì)于硅頻率控制器是非常容易實(shí)現(xiàn)的并可能是更少的價(jià)格。

更快的供貨周期

如前文所述,硅頻率控制器的核心是穩(wěn)定的高速振蕩模塊。工廠可預(yù)先生產(chǎn),然后根據(jù)客戶(hù)的需求來(lái)配置輸出頻率,這樣可大大縮短產(chǎn)品供貨周期。

SFC 晶源

硅頻率控制器是一種CMOS技術(shù),和ASIC是同一種工藝,所以ASIC很容易將硅頻率發(fā)生器的晶源集成進(jìn)去。如果是石英,因?yàn)槭遣煌墓に嚕詴?huì)帶來(lái)很多工藝和可靠性方面的問(wèn)題。

硅頻率控制器產(chǎn)品應(yīng)用

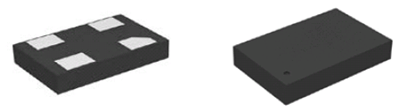

硅頻率控制器的外觀如圖7

圖7 硅頻率控制器的外觀圖

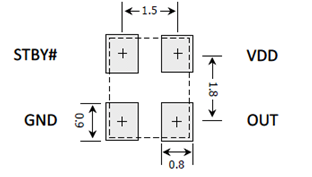

硅頻率控制器的管腳分布以2.5*2*0.55mm 為例,如圖8所示

圖8 硅頻率控制器的管腳分布圖(2.5*2*0.55mm)