摘要:提出一種基于FPGA技術(shù)的多路模擬量、數(shù)字量采集與處理系統(tǒng)的設(shè)計方案,分析整個系統(tǒng)的結(jié)構(gòu),并討論FPGA內(nèi)部硬件資源的劃分和軟件的設(shè)計方案等。本設(shè)計方案外部電路結(jié)構(gòu)簡單可靠,特別適用于多路檢測系統(tǒng)中,而且可以根據(jù)需要容易地對系統(tǒng)進行擴展,對于檢測系統(tǒng)來講具有一定的通用性。

關(guān)鍵詞:FPGA;A/D采集;數(shù)字量采集;Verilog HDL語言設(shè)計

0 引言

在電氣測控系統(tǒng)中,常常需要采集各種模擬量信號、數(shù)字量信號,并對它們進行相應(yīng)的處理。一般情況下,測控系統(tǒng)中用普通MCU(如51、196等單片機或控制型DSP)就可以完成系統(tǒng)任務(wù),但當系統(tǒng)中要采集的信號量特別多時(特別是各種信號量、狀態(tài)量),僅僅靠用普通MCU的資源就往往難以完成任務(wù)。本文所提出的一種基于FPGA技術(shù)的模擬量、數(shù)字量采集與處理系統(tǒng),利用FPGA的I/O端口多,且可以自由編程支配、定義其功能的特點,能很好地解決采集的信號路數(shù)多的問題。

1 系統(tǒng)組成

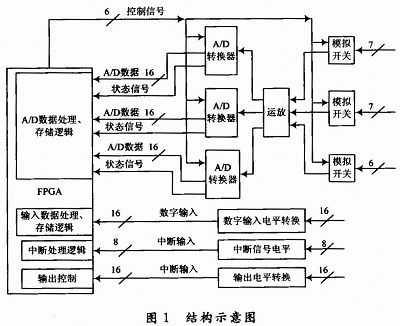

本系統(tǒng)中的外圍電路設(shè)計相對簡單、可靠,且鑒于FPGA自身的特點,系統(tǒng)具有較好的擴展性,在監(jiān)測和控制系統(tǒng)中也具有一定的通用性。系統(tǒng)主要包括:FPGA芯片區(qū)、多路選擇與A/D采樣電路、時鐘電源區(qū)、PROM代碼下載電路等幾部分。結(jié)構(gòu)示意如圖1所示。

2 FPGA芯片特點分析及資源分配

本系統(tǒng)中的FPGA是采用Altera公司的EP1C20F400。該系列的內(nèi)核采用1.5 V供電,I/O端口供電電壓為3.3V。

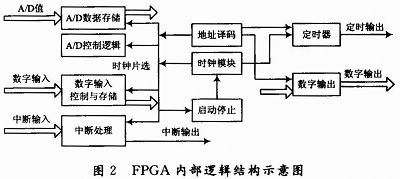

FPGA內(nèi)部資源劃分為四大部分,如圖2所示。

(1)FPGA邏輯運算中心。用來接收其他各部分的數(shù)據(jù),并按照程序中設(shè)定的方案對所收到的數(shù)據(jù)進行相應(yīng)的分析和處理。包括:對從MCU接收來的數(shù)據(jù)指令進行分析,并按其指令要求進行相應(yīng)操作;接收A/D采樣來的數(shù)據(jù),對數(shù)據(jù)進行處理,存儲等工作。

(2)A/D控制單元。主要負責(zé)控制外部A/D芯片和多路開關(guān)的選通時序,以及實現(xiàn)對A/D采要過程的合理控制,利用FPGA實現(xiàn)A/D自動采集與數(shù)據(jù)存儲。

(3)數(shù)字量監(jiān)測控制單元。負責(zé)所有要監(jiān)視和控制的數(shù)字量的狀態(tài)數(shù)據(jù)的采集和控制命令的輸出。這一部分主要實現(xiàn)數(shù)字量輸出的控制、數(shù)字量輸入的存儲、數(shù)字量輸入狀態(tài)變化識別(中斷輸入)。

(4)FPGA接口邏輯控制單元。在FPGA內(nèi)部設(shè)計了FPGA模塊與外界MCU的接口單元,該部分主要用于同CPU的接口,使數(shù)據(jù)采集系統(tǒng)可以方便的與PCI、ISA及其他總線連接。

3 模擬量采集的控制與管理

在模擬量采集外圍電路中,A/D芯片采用的是AD公司的AD976A。多路模擬量是通過AD438的多路開關(guān)后輸入到AD976A芯片的。

A/D采樣部分可分為:寄存器組、時鐘發(fā)生模塊、采樣控制狀態(tài)機、數(shù)據(jù)存儲模塊。

3.1 寄存器組

寄存器組用于設(shè)置/讀取A/D的工作狀態(tài),包括:采樣頻率設(shè)置寄存器、工作模式選擇寄存器、工作狀態(tài)寄存器及FIFO中斷寄存器。

(1)采樣頻率設(shè)置寄存器Frereg1,F(xiàn)rereg2(R/W):兩個16位寄存器,用于設(shè)置12路A/D的采樣頻率,其位含義如下:

頻率設(shè)置如下:

為保留位。

(2)工作模式選擇寄存器modereg(R/W)。176位寄存器,用于設(shè)置A/D的工作模式和啟動、停止FPGA,各位的定義如下:

(3)FIFO中斷寄存器(fifo_int)(R):16位寄存器,用來記錄FIFO的狀態(tài),各位定義如下:

3.2 時鐘發(fā)生模塊

(1)把時鐘分頻為1 MHz時鐘,作為狀態(tài)機的工作時鐘;

(2)生成20 Hz,50 Hz,100 Hz時鐘并結(jié)合Frereg的值給出12路A/D啟動中斷信號。

3.3 采樣控制狀態(tài)機

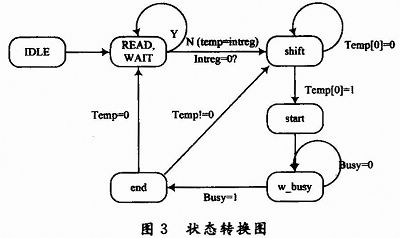

每個A/D用一個采樣控制狀態(tài)機,用于自動控制A/D的數(shù)據(jù)采集。其狀態(tài)轉(zhuǎn)換圖如圖3所示。

IDLE:空閑狀態(tài)。

READ:temp=intreg,進入下一狀態(tài)

WAIT:等待中斷,如果中斷寄存器(intreg)不為0,進入下一狀態(tài),否則返回READ。

SHIFT:根據(jù)temp[0]的值進行下一步操作,若temp[0]=0則temp>>1,同時通道計數(shù)器(counter)加1;若temp[0]=1,則根據(jù)counter的值給出通道選擇信號,進入下一狀態(tài)。

START:發(fā)出RC=0信號,進入下一狀態(tài)。

W_BLISY:RC=1,等待A/D轉(zhuǎn)換結(jié)束信號,如果結(jié)束,temp>>1,發(fā)出寫FIFO信號,進入下一狀態(tài)。

END:無效FIFO寫信號,若temp=0,表明已無中斷,coutnter=0,進入WAIT;否則,counter+1,進入SHIFT。

3.4 數(shù)據(jù)存儲模塊

用于存儲A/D轉(zhuǎn)換結(jié)果,對于每路A/D用一個FIFO。

4 數(shù)字采集模塊

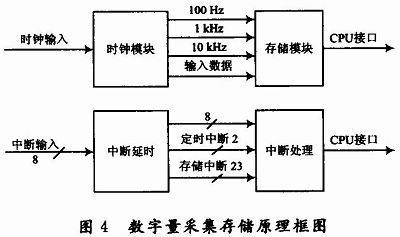

數(shù)字采集模塊主要完成數(shù)字量輸入的采集與存儲,中斷信號狀態(tài)識別功能。其原理圖如圖4所示。

5 結(jié)論

本文提出了一種基于FPGA技術(shù)的多路模擬量、數(shù)字量采集與處理系統(tǒng),設(shè)計了相應(yīng)的外圍硬件電路和系統(tǒng)處理軟件。在仿真和綜合調(diào)試成功的基礎(chǔ)上,本系統(tǒng)成功用于某重點預(yù)研項目的控制系統(tǒng)試驗中。試驗結(jié)果表明,本系統(tǒng)成功地完成了對多路模擬量、數(shù)字量的采集處理任務(wù)。