自動化控制要求實時采集數(shù)據(jù),快速控制,多樣分析,通信靈活,雖然采用單個處理器構(gòu)成的硬件平臺不能滿足要求。采用以MCU+DSP雙處理器為核心的硬件平臺則是較合理的設(shè)計方案。利用DSP實現(xiàn)數(shù)據(jù)實時采集、分析、計算;MCU完成管理、通信、人機(jī)接口等異步系統(tǒng)控制功能。該硬件平臺的MCU與DSP接口設(shè)計與數(shù)據(jù)傳輸是系統(tǒng)設(shè)計的重要部分,將直接影響系統(tǒng)性能和數(shù)據(jù)傳輸效率。數(shù)據(jù)傳輸通常采用雙端口RAM、串行通信、并行主機(jī)等接口方式。其中,并行主機(jī)接口的方式可以滿足大量數(shù)據(jù)實時傳輸要求。這里以MCF5272型和ADSP-BF527型數(shù)字信號處理器構(gòu)建一種MCU+DSP雙處理器的嵌入式平臺,詳細(xì)論述DSP通過主機(jī)DMA端口(Host DMA Port,簡稱HOSTDP)實現(xiàn)主機(jī)引導(dǎo)加載程序以及DSP與主機(jī)的通信。

2 MCU+DSP雙處理器接口設(shè)計

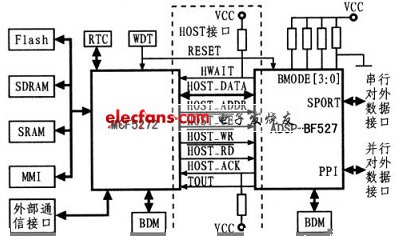

圖l為MCU+DSP雙處理器ADSP-BF527與MCF5272的接口電路。該嵌入式平臺采用ColdFire系列的MCF5272型MCU作為主機(jī)。MCF5272具有基于第二代ColdFire V2的內(nèi)核,32位數(shù)據(jù)和地址總線,SDRAM接口,4個16位定時器,3通道PWM輸出,主頻高達(dá)66 MHz,豐富的外部接口和較強(qiáng)的通信功能。此外,該器件還具有出色的編碼密度和系統(tǒng)性能。

圖1 ADSP-BF527與MCF5272的接口電路

該系統(tǒng)DSP采用ADSP-BF527型數(shù)字信號處理器,該器件采用了微信號架構(gòu)(MSA),時鐘頻率達(dá)600 MHz,功耗低至O.8 V,支持強(qiáng)大的片上總線系統(tǒng),具有多個獨(dú)立的DMA控制器,擁有較強(qiáng)的并行數(shù)據(jù)處理能力。ADSP-BF527帶有一個HOSTDP,便于與外部主機(jī)構(gòu)成雙處理器架構(gòu),完成多種數(shù)據(jù)處理和控制任務(wù)。ADSP-BF527的HOSTDP內(nèi)部分為主機(jī)外部接口模塊(HEI)、外圍訪問總線(PAB)接口模塊、FIFO模塊、控制邏輯模塊和DMA接口模塊。

圖1中,接口電路各信號的功能為:HWAIT為握手信號,防止Boot Kernel忙時主機(jī)寫數(shù)據(jù);HOST_DATA為16位數(shù)據(jù)總線,主機(jī)與從機(jī)數(shù)據(jù)交換的通道;HOST_ADDR為訪問屬性信號,O表示訪問數(shù)據(jù)接口,l表示訪問配置接口;HOST_CE為主機(jī)對從機(jī)使能;HOST_WR為主機(jī)寫入HOSTDP使能信號;HOST_RD為主機(jī)讀取HOSTDP使能信號;HOST_ACK為數(shù)據(jù)傳輸握手信號,應(yīng)答模式下為HRDY,中斷模式下為FRDY;TOUT為讀寫操作超時信號,應(yīng)答模式下Host—Timeout計數(shù)溢出時產(chǎn)生;BMODE[3:0]為啟動模式設(shè)置信號。

3 ADSP—BF527啟動與程序加載

ADSP—BF527復(fù)位包括硬件和軟件復(fù)位,復(fù)位中斷優(yōu)先級最高。當(dāng)釋放RESET信號后,該處理器開始從片內(nèi)BootROM的0xEF00 0000地址讀取指令并執(zhí)行。片內(nèi)Boot ROM含有一個Boot引導(dǎo)核,用于預(yù)引導(dǎo)和加載用戶數(shù)據(jù)。

3.1 預(yù)引導(dǎo)

ADSP—BF527復(fù)位后,Boot引導(dǎo)核首先調(diào)用Preboot子程序。Preboot子程序通過訪問一次可編程ROM(OTP)中的工廠設(shè)置頁(FPS)和預(yù)引導(dǎo)設(shè)置頁(PBS)來設(shè)置系統(tǒng)映射寄存器(MMR),包括鎖相環(huán)(PLL)、電源調(diào)節(jié)、SDRAM控制器、異步外部總線接口單元(EBIU)、HWAIT的信號模式以及0TP定制引導(dǎo)。

PBS由用戶設(shè)置,每次使用4頁。當(dāng)PBS出現(xiàn)錯誤時,可置0TPINVALID位,使其無效,再使用下一個4頁。如果設(shè)置PBS首頁的PLL和電源調(diào)節(jié)錯誤,可采用BMODE=0000引導(dǎo)模式補(bǔ)救。該模式預(yù)引導(dǎo)程序不讀取PBS頁,F(xiàn)PS處理后,ADSP-BF527處理器變?yōu)榭臻e狀態(tài)。

處于安全考慮,PBS頁設(shè)置引導(dǎo)模式禁止/使能位,禁止其他引導(dǎo)方式。這樣即使BMODE引腳設(shè)置對應(yīng)這些禁止引導(dǎo)方式,不會引導(dǎo)Boot引導(dǎo)核進(jìn)入空閑狀態(tài)。

3.2 引導(dǎo)模式設(shè)置

預(yù)引導(dǎo)結(jié)束后,Boot引導(dǎo)核根據(jù)BMODE[3:0]引腳設(shè)置啟動相應(yīng)的引導(dǎo)方式加載用戶數(shù)據(jù)(引導(dǎo)流)。引導(dǎo)流為已定義格式,包含若干數(shù)據(jù)塊和特殊指令,每數(shù)據(jù)塊都含有一個16字節(jié)的塊頭,該塊頭由DSP的開發(fā)工具Visual DSP++設(shè)置生成,用于指示引導(dǎo)核是否完成引導(dǎo)過程。BMODE[3:0]引腳設(shè)置的引導(dǎo)模式包括無引導(dǎo)、主機(jī)引導(dǎo)和從機(jī)引導(dǎo)模式。引導(dǎo)模式設(shè)置如表1所示。

其中無引導(dǎo)模式由廠商編程設(shè)置0TP頁完成。主機(jī)引導(dǎo)模式中DSP自行加載用戶數(shù)據(jù).通常是從并行接口的Flash或者SPI、TWI接口的存儲器讀取數(shù)據(jù)。從機(jī)模式DSP作為從機(jī),主機(jī)控制RESET信號。通常主機(jī)先設(shè)置RESET信號,然后通過檢測HWAIT引腳等待預(yù)引導(dǎo)程序?qū)崿F(xiàn),最后提供加載用戶數(shù)據(jù)。

3.3 HOST DMA引導(dǎo)模式

該系統(tǒng)為MCU+DSP架構(gòu),主處理器MCF5272通過HOSTDP控制從機(jī)ADSP-BF527。ADSP—BF527的程序作為MCF5272數(shù)據(jù)寫入Flash存儲器中。該系統(tǒng)加電復(fù)位后,MCF5272向從機(jī)加載程序并引導(dǎo)啟動。因此采用HOST DMA引導(dǎo)設(shè)計較靈活,獨(dú)立存儲器個數(shù)少,提高性能并降低成本。系統(tǒng)維護(hù)時,F(xiàn)lash中ADSP-BF527程序通過修改主機(jī)通信接口,提高產(chǎn)品維護(hù)效率。該設(shè)計的BMODE[3:0]引腳電平設(shè)置為1110,采用從機(jī)16位HOSTDP引導(dǎo)模式。

當(dāng)主機(jī)復(fù)位ADSP—BF527后,ADSP-BF527可從片上BootROM的0xEF00 0000地址執(zhí)行預(yù)引導(dǎo)程序。預(yù)引導(dǎo)結(jié)束后,向主機(jī)發(fā)送HWAIT信號,主機(jī)開始向ADSP—BF527加載用戶數(shù)據(jù)。用戶數(shù)據(jù)加載完成后,主機(jī)發(fā)送HIR9命令,ADSP-BF527引導(dǎo)核執(zhí)行調(diào)用指令,程序指針跳至EVTl寄存器內(nèi)用戶應(yīng)用程序的首地址,將控制權(quán)交給用戶應(yīng)用程序。此時,引導(dǎo)結(jié)束。ADSP-BF527處理器繼續(xù)執(zhí)行用戶應(yīng)用程序。4 HOSTDP數(shù)據(jù)傳輸

ADSP-BF527通過外設(shè)接口總線設(shè)置HOST CONTROL寄存器的HOST_EN位使能HOSTDP。如果禁止HOSTDP,應(yīng)在清除HOST_EN位前將HOST_RST置位。一旦使能HOSTDP則由外部主機(jī)控制。外部主機(jī)通過編程設(shè)置DMA發(fā)送和接收數(shù)據(jù),并將其存儲到ADSP-BF527有效的內(nèi)部和外部存儲器中。

4.1 HOSTDP設(shè)置

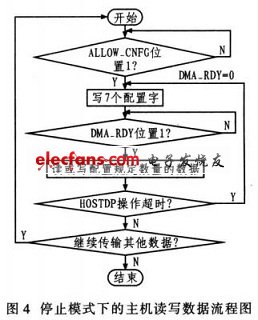

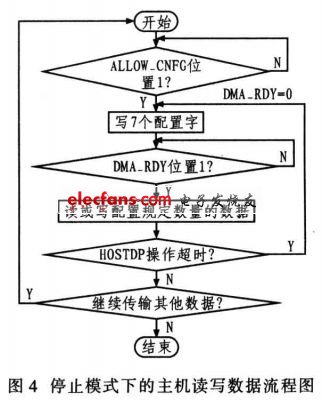

數(shù)據(jù)傳輸前,主機(jī)需配置DMA控制器。主機(jī)首先讀取從機(jī)HOST_STATUS寄存器的ALLOW_CNFG位。如果允許配置,主機(jī)將向HOSTDP發(fā)送7個16位控制字。主機(jī)通過這些控制字配置HOSTDP的DMA讀寫、DMA模式、起始地址等參數(shù)。接收所有控制字后,ADSP-BF527根據(jù)控制字重新配置HOETDP。在配置完成前,主機(jī)處理器不允許提供新控制字。通過寫入控制字,該設(shè)計將DMA設(shè)置為應(yīng)答模式,數(shù)據(jù)傳輸采用停止模式。

總線寬度16位,以先傳輸?shù)臀粩?shù)據(jù)的順序傳輸數(shù)據(jù)。配置完成后,主機(jī)以所配置的方式讀寫數(shù)據(jù),從而實現(xiàn)數(shù)據(jù)傳輸。數(shù)據(jù)傳輸過程中,通過ADSP-BF527軟件編程設(shè)置控制寄存器中HER和EHW位使能或禁止主機(jī)讀寫HOSTDP,HER和EHW的設(shè)置,不會影響到寫配置口、控制命令和讀狀態(tài)。由于主機(jī)不能查詢HOSTDP的HER和EHW位,因此,該系統(tǒng)設(shè)計ADSP-BF527一直保持HER和EHW位使能。

4.2 數(shù)據(jù)讀寫流程

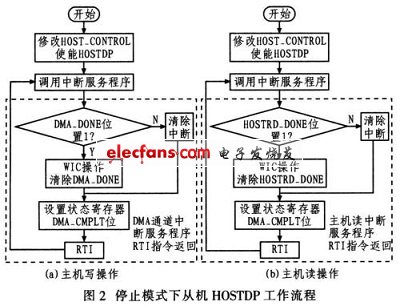

當(dāng)使能HOSTDP,DMA通道配置后,主機(jī)通過所配置的DMA通道與ADSP—BF527通信。數(shù)據(jù)讀寫時,在有效數(shù)據(jù)的最后需附加一個傳輸終止字確保數(shù)據(jù)傳輸。數(shù)據(jù)寫操作用于主機(jī)向從機(jī)的數(shù)據(jù)傳輸。MCF5272將ADSP-BF527所需的信號與設(shè)置寫入HOSTDP的FIFO,DMA同時將從FIFO移出數(shù)據(jù),并存儲到DMA配置字規(guī)定的存儲器。數(shù)據(jù)讀操作用于從機(jī)向主機(jī)數(shù)據(jù)傳輸。ADSP—BF527的DMA將從機(jī)存儲器中的數(shù)字信號處理結(jié)果移至HOSTDP的FIFO。主機(jī)執(zhí)行讀操作,從FIFO中讀取數(shù)據(jù)。

停止模式下ADSP-BF527的HOSTDP讀寫操作流程如圖2所示。其中,DMA_DONE位在DMA將FIFO數(shù)據(jù)移出后置1,在下一次主機(jī)寫數(shù)據(jù)時置O。HOSTRD_DONE位在主機(jī)將FIFO的數(shù)據(jù)移出后置l,下一次主機(jī)讀操作,DMA向FIFO傳輸數(shù)據(jù)時置為0。

應(yīng)答模式下,主機(jī)對HOSTDP的操作時序如圖3所示。在預(yù)定讀寫溢出時間內(nèi),ADSP-BF527仍未完成相應(yīng)的讀寫操作,主機(jī)未接收到HRDY信號,主機(jī)超時寄存器計數(shù)溢出并產(chǎn)生超時中斷。該設(shè)計的中斷服務(wù)程序首先通過GPIO引腳告知主機(jī)數(shù)據(jù)讀寫失敗,停止DMA通道數(shù)據(jù)傳輸;當(dāng)主機(jī)重置HRDY信號為高電平,允許下一周期繼續(xù)傳輸數(shù)據(jù);并禁止HOSTDP,在停止模式下,具體的主機(jī)讀寫數(shù)據(jù)流程如圖4所示。

5 結(jié)語

隨著自動化領(lǐng)域監(jiān)測、控制任務(wù)對嵌入式系統(tǒng)的要求不斷提高,多處理器硬件系統(tǒng)模式的快速發(fā)展,電子技術(shù)和半導(dǎo)體加工工藝的發(fā)展促使DSP和MCU的融合。因此,MCU+DSP的雙處理器結(jié)構(gòu)已成為多核處理器的發(fā)展方向。