PC104是一種專門為嵌入式控制而定義的工業(yè)控制總線,PC104與普通PC總線控制系統(tǒng)的主要區(qū)別是:

(1)小尺寸結構。

(2)堆棧式連接。

(3)輕松總線驅動。

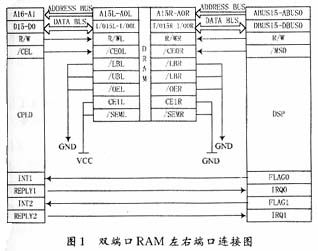

PC104有2個版本,8位和16位,分別與PC和PC/AT相對應。PC104 PLUS則與PCI總線相對應。本文主要涉及的是PC104與DSP的16位數據通信接口設計,采用了CYPRESS公司的雙端口靜態(tài)讀寫存儲器CY7C028V15AC作為共享存儲器,雙端口RAM右側接ADI公司的DSP芯片T S101,左側接PC104總線,控制邏輯用ALTERA公司ACEX系列CPLD中的EP1K100TC208來實現。

2雙端口RAM訪問模式

CY7C028V15AC是16 b×64 k的雙端口RAM,支持高速的訪問,訪問速度為20 ns,支持左右2個端口完全異步訪問。2個端口的選通信號有效,則雙端口RAM兩側可以同時對雙端口RAM進行讀寫操作。需要解決的是當同時訪問到一個存貯塊時的沖突問題。有2種方法可以解決訪問沖突:一種是信號令牌傳遞方式,雙端口RAM內部提供了8個Semaphore鎖存單元,可以在邏輯上把雙端口RAM劃分為8個區(qū)段;當某個端口要訪問某個區(qū)塊時,首先向相應的鎖存單元請求令牌,以確定訪問是否會產生沖突,即向某一個鎖存單元寫“0”,然后讀回所寫數據,如果成功,則對應于該鎖存單元的塊是空閑的,可以訪問,否則就不能訪問。當一側正在訪問雙端口RAM的某一塊,則相應的鎖存單元對另一側是不能訪問的。申請令牌通過讀寫I/O的方式實現,實際用到的是雙端口RAM左右兩側數據總線的D0位,地址總線的A2~A0位(其譯碼對應于8個鎖存單元),以及左右兩側對鎖存單元訪問的使能控制端SEML和SEMR。另一種方式是中斷方式。在中斷方式下,RAM最高的兩個地址作為通訊郵箱,FFFEH分配給右端口,FFFFH分配給左端口。兩個郵箱的使用方法一致。以右端口為例,當DSP向FFFEH地址寫任意一個值時,左端口的中斷請求信號INTL有效,當響應完中斷請求后,PC104總線讀一次FFFEH地址就可以INTL清除中斷。

本文中采用中斷方式設計PC104與DSP的握手信號。考慮到用CPLD來設計數字邏輯的靈活性和可重復編程,用CPLD來控制中斷請求與響應信號,所以RAM最高端的兩個地址仍作為普通的R AM單元使用。雙端口RAM左右端口的連接如圖1所示。

當DSP向PC104請求數據,TS101的標志位FLAG0通過CPLD的緩沖連接到PC104的其中一條中斷信號引腳,當PC104收到中斷請求向RAM寫完數據,通過寫I/O口的方式,由CPLD產生回復信號到TS101的IRQ0,TS101在適當的時間讀取數據并進行算法處理。當TS101向PC104發(fā)送數據,則先向RAM中寫數據,寫完后由標志位FLAG1產生讀數據請求信號,通過CPLD緩沖連接到PC10 4的另一條中斷信號引腳,PC104響應中斷讀完數據,通過寫I/O口的方式由CPLD產生回復信號到TS101的IRQ1。當PC104訪問雙端口RAM時。數據總線的16位通過CPLD緩沖連接到RAM左端口的I/O15L~I/O0L,因為16位的數據訪問占用的是偶地址,所以地址總線的A16~A1在CPLD緩沖后連接到RAM的左端口的A15L~A0L地址線。PC104其余的地址線通過在CPLD里的譯碼產生RAM左端口的選通信號。當TS101訪問RAM,TS101的前16根地址線連接到RAM的A15R~A0R,前16根數據線連接到RAM右端口的I/O15R~I/O0R,用產生選通信號,通過TS 101的編程實現,訪問RAM的有效地址由用戶定義。?

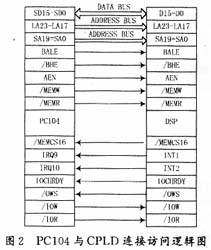

3PC104與CPLD的連接關系

通過CPLD,PC104要實現對雙端口RAM的訪問,首先要考慮的是分配給RAM的存儲地址,因為64 k×16 b的RAM需要64 k的偶地址空間,或者說128 k的連續(xù)地址空間,工控機1 M以內可由用戶使用的自由地址空間往往達不到128 k。所以應將RAM安排在1 M地址空間以外訪問。此時除了用到用于1 M尋址的地址線SA19~SA0,還要采用1 M外尋址的地址線LA23~LA17。需要注意的是,PC104的總線上的SA19~SA17與LA19~LA17是重復的。區(qū)別在于SA10~SA0是通過總線地址鎖存使能信號BALE鎖存輸出,而LA19~LA17未經鎖存,為保證在對RAM訪問期內地址信號一直有效,至少應在CPLD內將LA23~LA20進行BALE鎖存。本文中將RAM的地址安排在1 M地址空間外從100000 H開始的64 K偶地址。所有需要用到的PC104信號線都連接到CPLD,CPLD將SA16~SA1緩沖連接到RAM,其余地址線譯碼產生RAM左端口選通信號。PC104與CPLD連接的訪問邏輯如圖2所示。

其中有效表示數據總線的高8位有效,SA0有效表示數據總線的低8位有效,作為譯碼信號的一部分,對于單片16位數據線的集成電路,實際上也可以不連接,用SA0和高端地址線譯碼產生選片信號。AEN信號有效表示計算機在和某個設備進行DMA傳送,其他的設備發(fā)現AEN信號有效,就不要響應尋址信號。因此在CPLD內部邏輯里設置當AEN信號有效時,將進入CPLD的地址信號線置為高阻態(tài)。

![]()

是存儲器讀寫信號,是用于1 M以外地址空間的讀寫信號,當這兩個信號之一有效且尋址到1 M內的地址,將分別使1 M以內地址的讀寫

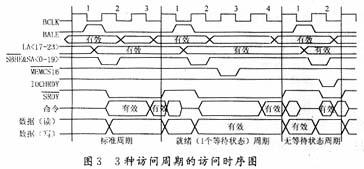

一起控制總線周期的長短。有3種存儲器訪問周期:標準周期,就緒周期,無等待狀態(tài)周期。訪問時序如圖3所示。

在設計的時候考慮到信號在CPLD里的延時,如果標準周期對于訪問的時間長度不夠,可以采 用有1個等待狀態(tài)的就緒周期,而這只需要修改CPLD的設計并重新下載到CPLD即可,由此可 見用CPLD作為控制芯片的優(yōu)點。

4結語

本文說明的這種PC104總線與DSP的數據通訊接口設計,也可以作為采用其他計算機總線與DS P進行16位數據通訊接口設計的參考。