1 AD7674和C8051060簡(jiǎn)介

1.1 AD7674簡(jiǎn)介

AD7674是一款高精度 18位逐次逼近(SAR)型ADC,具有采樣速率高、精度高、功耗低、無管道延遲的特點(diǎn),其采樣速率最高可以達(dá)到800 kHz,積分非線性誤差(INL)最大為±2.5 LSB,在整個(gè)工作溫度范圍內(nèi)可保證無丟碼。該器件是全差分輸入,5 V單電源供電,可接5 V或3.3 V數(shù)字電源。AD7674還具有許多其他特點(diǎn),包括1個(gè)內(nèi)部變換時(shí)鐘、1個(gè)內(nèi)部基準(zhǔn)緩沖器、誤差修正電路以及串行(SPI)與并行(18、16或8位總線)接口。

AD7674采用逐次逼近結(jié)構(gòu)。由于逐次逼近結(jié)構(gòu)的多路技術(shù)和低功耗,使此器件比一般∑-△ A/D轉(zhuǎn)換器的性能更優(yōu)越;而且芯片內(nèi)部還集成了跟蹤保持電路,逐次逼進(jìn)的結(jié)構(gòu)使其沒有任何通道延時(shí),這些特征使該器件廣泛地應(yīng)用于多通道系統(tǒng)中。

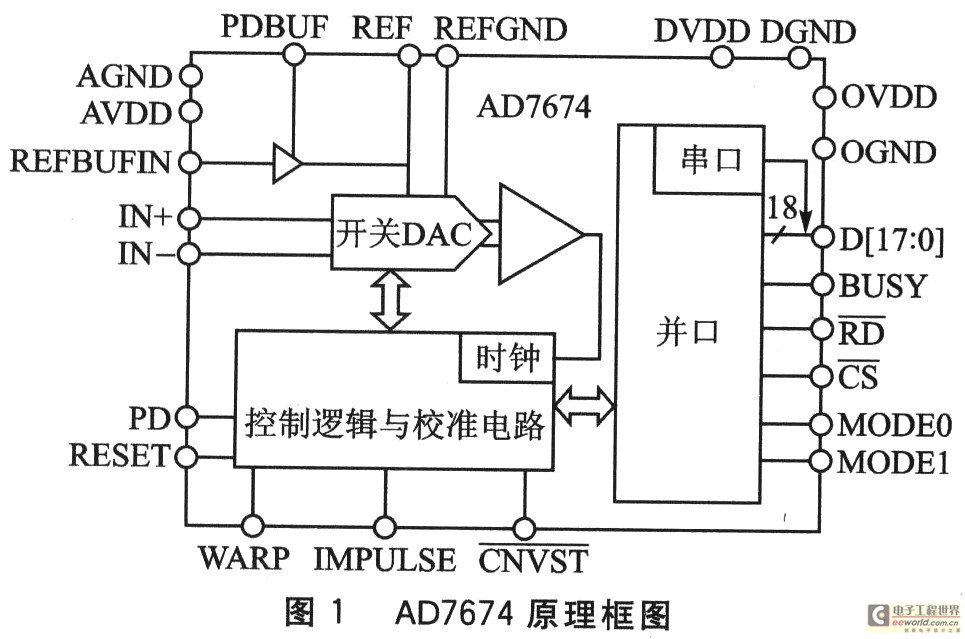

器件的原理框圖如圖1所示。

AD7674能提供3種不同轉(zhuǎn)換速率工作方式,以便對(duì)不同的具體應(yīng)用優(yōu)化性能。這3種工作模式如下:

WARP,允許采樣率高達(dá)800 kHz。然而在這種模式下只有當(dāng)轉(zhuǎn)換之間的時(shí)間不超過1 ms時(shí),才能保證其轉(zhuǎn)換的精度。如果連續(xù)兩次轉(zhuǎn)換之間的時(shí)間大于1 ms,第一次轉(zhuǎn)換的結(jié)果就會(huì)被忽略,這種模式適合于要求快速采樣率的應(yīng)用。

NORMAL,這種模式的采樣率為666 kHz,在這種模式下對(duì)采樣轉(zhuǎn)換之間的時(shí)間沒有限制,既可保證高的轉(zhuǎn)換精度又可確保快速的采樣速率。

IMPULSE,一種低功耗模式,其采樣率為570 kHz。例如當(dāng)器件工作在1 kHz時(shí),僅消耗功率136μW。該器件適合于電池供電的應(yīng)用。

1.2 C8051 F060簡(jiǎn)介

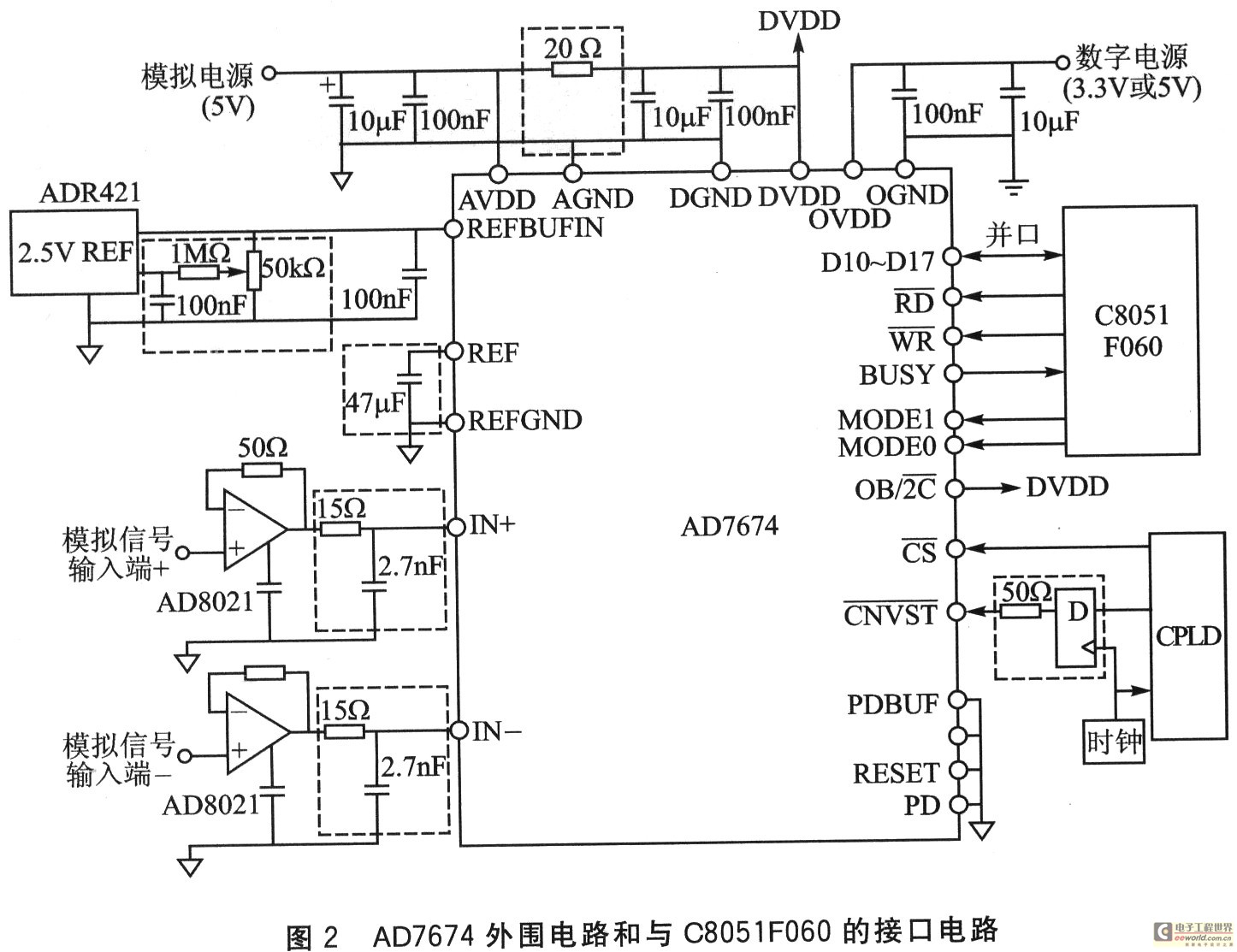

C8051F060單片機(jī)是表貼TQFP100封裝,包括1個(gè)8051內(nèi)核,2個(gè)16位AD轉(zhuǎn)換器,8個(gè)8位A/D轉(zhuǎn)換器,2個(gè)12位D/A轉(zhuǎn)換器,1個(gè)SPI接口,1個(gè)I2C接口,2個(gè)UART接口,64 KB Flash及22個(gè)中斷源。只用1塊C8051F060芯片即可完成單片機(jī)8051的各種控制,多路A/D轉(zhuǎn)換和D/A轉(zhuǎn)換,I2C、SPI數(shù)據(jù)總線傳輸,RS232、RS485串口通信等功能,從而大大減少了元器件的種類,縮小了印制板的面積,節(jié)約了成本,提高了系統(tǒng)可靠性。而其交叉開關(guān)方式的配置,使I/O口應(yīng)用更加靈活方便。2 AD7674與C8051F060的接口電路圖2為AD7674在高速采集系統(tǒng)中的外圍電路和接口電路。外圍電路包括電壓基準(zhǔn)輸入的設(shè)計(jì)、模擬電壓輸入部分的設(shè)計(jì)、模擬和數(shù)字電源供電的設(shè)計(jì)及接口電路的設(shè)計(jì)。接口電路包括AD7674與C8051F060和CPLD的接口。

關(guān)鍵字:數(shù)據(jù)采集 模數(shù)轉(zhuǎn)換器 并口 C8051F060

3 A/D轉(zhuǎn)換

本文中的AD7674采用NORMAL模式進(jìn)行數(shù)據(jù)采樣轉(zhuǎn)換。在這種模式下對(duì)采樣轉(zhuǎn)換之間的時(shí)間沒有限制,這樣可同時(shí)保證高的轉(zhuǎn)換精度和采樣速率。

CNVST信號(hào)控制AD7674轉(zhuǎn)換的開始,一旦轉(zhuǎn)換開始就不能放棄或重新開始,直到轉(zhuǎn)換完成。CNVST信號(hào)與CS和RD互不干擾。

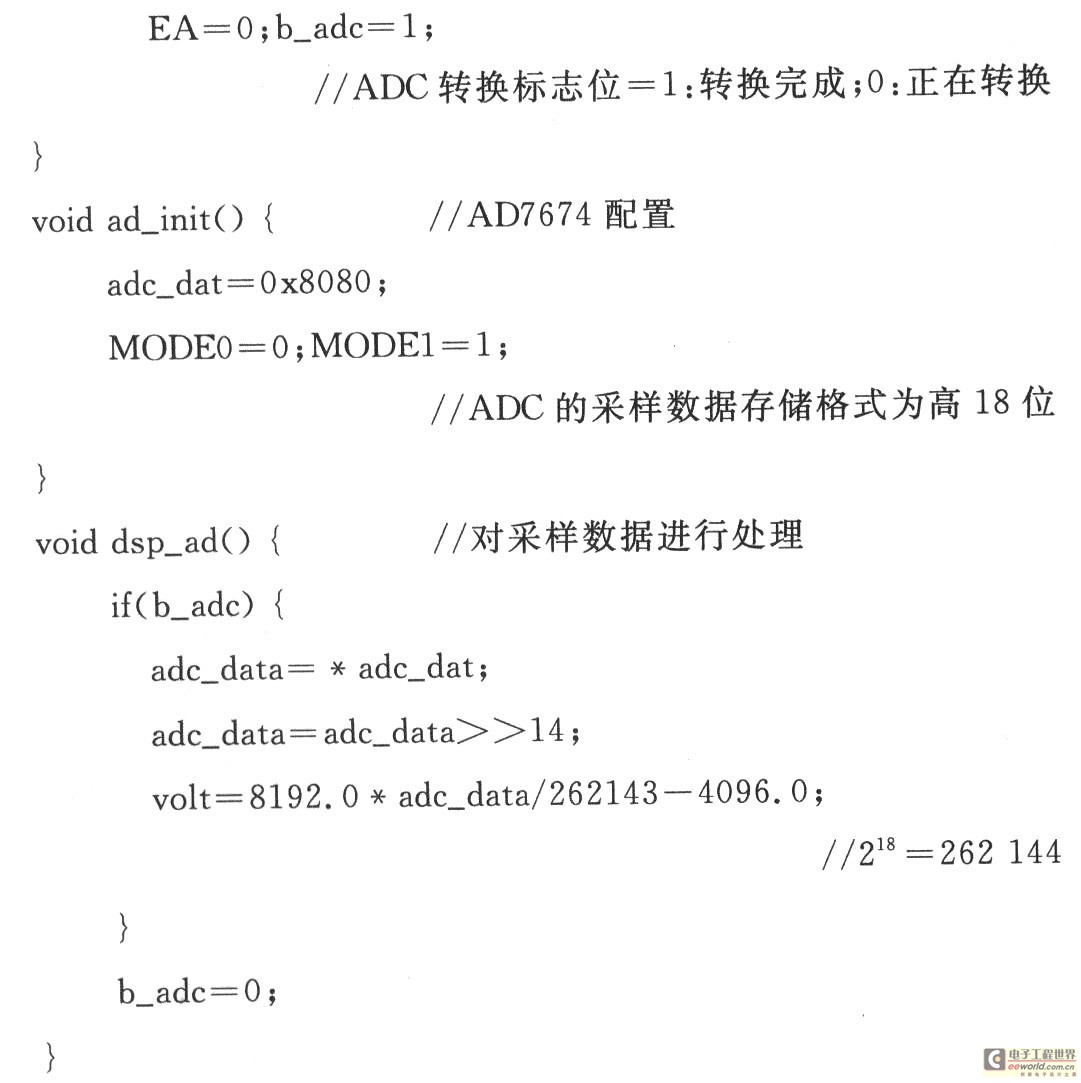

AD7674的并口總線寬度可配置為18位、16位或8位。數(shù)據(jù)既可以在每次轉(zhuǎn)換完成后讀出,也可在下一次轉(zhuǎn)換過程中讀出,讀數(shù)據(jù)時(shí)序如圖3所示。然而在轉(zhuǎn)換過程讀數(shù)據(jù)模式中,推薦在前半轉(zhuǎn)換周期讀數(shù)據(jù),這樣可以避免數(shù)字接口和模擬轉(zhuǎn)換電路之間潛在的數(shù)據(jù)沖突。本文采用的是8位并口總線寬度,配置為 MODE0=0,MODE1=1,以便于和單片機(jī)進(jìn)行數(shù)據(jù)傳輸。

值得注意的是在讀取A/D轉(zhuǎn)換數(shù)據(jù)時(shí),采用轉(zhuǎn)換完畢后讀取數(shù)據(jù)。要保證時(shí)序關(guān)系正確,一定要在數(shù)據(jù)轉(zhuǎn)換結(jié)束,而下一次轉(zhuǎn)換開始之前把數(shù)據(jù)讀走;假如讀取數(shù)據(jù)時(shí)數(shù)據(jù)轉(zhuǎn)換沒有結(jié)束或剛啟動(dòng)下一次數(shù)據(jù)轉(zhuǎn)換,則會(huì)造成讀取數(shù)據(jù)錯(cuò)誤。本文采用CPLD經(jīng)由外部有源晶振進(jìn)行分頻,產(chǎn)生轉(zhuǎn)換信號(hào)CNVST與讀信號(hào)RD相關(guān),使得RD信號(hào)和CNVST信號(hào)同步,從而保證讀取的采集數(shù)據(jù)正確無誤。

4 軟件編程

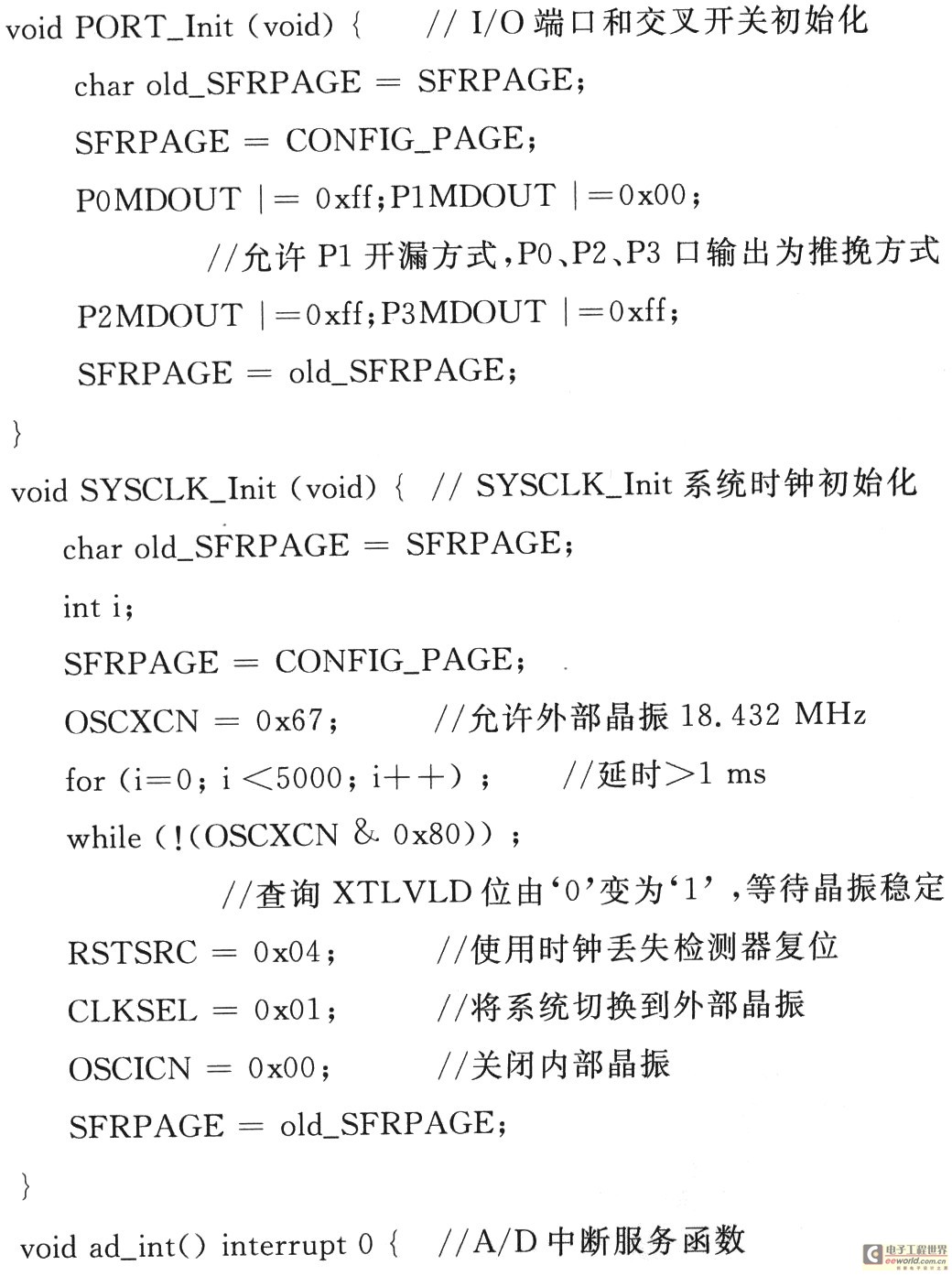

在軟件編制時(shí),首先要對(duì)單片機(jī)C8051F060進(jìn)行初始化和對(duì)AD7674進(jìn)行配置,再啟動(dòng)轉(zhuǎn)換信號(hào)進(jìn)行數(shù)據(jù)轉(zhuǎn)換和讀取數(shù)據(jù)。單片機(jī)C8051F060的初始化包括對(duì)單片機(jī)的I/O端口、交叉開關(guān)和系統(tǒng)時(shí)鐘的初始化。AD7674配置包括轉(zhuǎn)換模式、總線接口數(shù)據(jù)方式和采樣數(shù)據(jù)存儲(chǔ)格式的配置。部分源代碼程序如下:

結(jié) 語

本文詳細(xì)介紹了高速率、高精度的18位AD7674與C8051F060之間并口通信的接口電路及其軟件設(shè)計(jì)。該嵌入式數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)簡(jiǎn)潔,在Keil 集成開發(fā)環(huán)境下采用單片機(jī)C語言編寫、調(diào)試完成。由于數(shù)據(jù)采集系統(tǒng)可應(yīng)用于各種信號(hào)處理系統(tǒng)中,具有很高的推廣價(jià)值。本文采用的單片機(jī)配置靈活,傳輸速度快,接口采用并口通信,可實(shí)現(xiàn)嵌入式數(shù)據(jù)采集系統(tǒng)高速數(shù)據(jù)傳輸;同時(shí)AD7674與AD7678、AD7679等18位SAR ADC以及AD7621、AD7623等16位高速SAR ADC引腳相兼容,從而大大增強(qiáng)了系統(tǒng)開發(fā)的靈活性和拓展性。