1 LVDS技術(shù)簡介

LVDS(Low Voltage Differential Signaling)是一種低擺幅的差分信號(hào)技術(shù),它使得信號(hào)能在差分PCB線對或平衡電纜上以幾百M(fèi)b/s的速率傳輸,其低壓幅和低電流驅(qū)動(dòng)輸出實(shí)現(xiàn)了低噪聲和低功耗。LVDS在兩個(gè)標(biāo)準(zhǔn)中被定義:IEEE P159613(1996年3月通過),主要面向SCI(Scalable Coherent Inteface),定義了LVDS的電特性,還定義了SCI協(xié)議中包交換時(shí)的編碼;ANSI/TIA/EIA-644(1995年11月通過),主要定義了LVDS的電特性,并建議了655 Mb/s最大速率和11 923 Gb/s的無失真通道上的理論極限速率。在兩個(gè)標(biāo)準(zhǔn)中都指定了與物理通道無關(guān)的特性,這保證了LVDS能成為多用途的接口標(biāo)準(zhǔn)。

圖1給出了典型的LVDS互連方法。這里使用的是DS90C031 LVDS驅(qū)動(dòng)器芯片和DS90C032LVDS接收器芯片,其中DATA INPOUT和DATA OUTPOUT是TTL電平。驅(qū)動(dòng)器和接收器主要完成TTL信號(hào)和LVDS信號(hào)之間的轉(zhuǎn)換。LVDS驅(qū)動(dòng)器由一個(gè)驅(qū)動(dòng)差分線對的電流源組成,通常電流為3mA。LVD8接收器具有很高的輸入阻抗,因此驅(qū)動(dòng)器輸出的電流大部分都流過100Ω的匹配電阻,并在接收器的輸入端產(chǎn)生大約300 mA的電壓。當(dāng)驅(qū)動(dòng)器翻轉(zhuǎn)時(shí),它改變流經(jīng)電阻的電流方向,接收器產(chǎn)生有效的邏輯“1”和邏輯“0”狀態(tài)。

應(yīng)用LVDS具有許多優(yōu)勢:

(1)高速率。由于LVDS邏輯狀態(tài)間的電壓變化僅為300 mV,因而能非常快地改變狀態(tài)。例如當(dāng)信號(hào)電平在333 ps內(nèi)變化300 mV時(shí),壓擺率僅0.9 V/ns,低于將信號(hào)失真和串?dāng)_減到最小時(shí)的標(biāo)準(zhǔn)壓擺率1 V/ns。如果使用上升和下降時(shí)間不大于比特寬度2/3的老標(biāo)準(zhǔn),那么具有333 ps躍變的信號(hào)能在1 Gb/s下工作,仍保有很大的余地。

(2)低功耗。隨著工作頻率的增加,LVDS的電源電流仍保持平坦,而CMOS和GTL技術(shù)的電源電流則會(huì)隨頻率增加而呈指數(shù)上升,這得益于使用恒流線路驅(qū)動(dòng)器。電流源把輸出電流限制到約3.5 mA,同時(shí)也限制跳變期間產(chǎn)生的任何尖峰電流。由于沒有尖峰電流,就有可能獲得1.5 Gb/s的高數(shù)據(jù)率而不明顯增加功耗。恒流驅(qū)動(dòng)輸出還能容忍傳輸線的短路或接地,而不會(huì)產(chǎn)生熱問題。LVDS降低了終端電阻壓降,因此還降低了電路的總功耗。

(3)噪聲性能好。LVDS產(chǎn)生的電磁干擾低,這是因?yàn)榈碗妷簲[幅、低邊沿速率、奇模式差分信號(hào),以及恒流驅(qū)動(dòng)器的Icc尖峰只產(chǎn)生很低的輻射。傳輸通路上的高頻信號(hào)跳變產(chǎn)生輻射電磁場,場強(qiáng)正比于信號(hào)攜帶的能量,通過減小電壓擺幅和電流能量,LVDS把該場強(qiáng)減到最小;差分驅(qū)動(dòng)器引入了奇模式傳輸,在傳輸線上流過大小相等、極性相反的電流,電流在該線對內(nèi)返回,面積很小的電流回路產(chǎn)生最低的電磁干擾;當(dāng)差分傳輸線緊耦合時(shí),串入的信號(hào)是作為共模電壓出現(xiàn)在接收器輸入的共模噪聲中,差分接收器只響應(yīng)正負(fù)輸入之差,因此當(dāng)噪聲同時(shí)出現(xiàn)在2個(gè)輸入中時(shí),差分信號(hào)的幅度并不受影響。共模噪聲抑制也同樣適用于其他噪聲源,比如電源波動(dòng),襯底噪聲和接地回跳等。

(4)具有故障安全(fail-safe)特性確保可靠性。LVDS驅(qū)動(dòng)器和接收器還能實(shí)現(xiàn)熱插拔,因?yàn)楹懔黩?qū)動(dòng)解決了損壞問題。另一特點(diǎn)是接收器的故障保護(hù)功能,它能防止在輸入引腳懸空時(shí)產(chǎn)生輸出振蕩。除上述各種優(yōu)點(diǎn)外,LVDS只需要簡單的端接電阻。這些電阻可以集成到芯片之中,與每條傳輸線配備多個(gè)電阻和電容元件相比,大大降低了所需的費(fèi)用。另外,LVDS能容忍傳輸線通路微小的阻抗失配,只要差分信號(hào)在緊耦合的傳輸通路中通過平衡不連續(xù)處,信號(hào)仍能保持其完整性。非阻抗受控連接器、電路板過孔和芯片封裝對差分信號(hào)的影響要比對單端信號(hào)的影響小得多。表1給出了RS 422與LVDS之間的簡單比較,LVDS的優(yōu)勢是顯而易見的。

2 LVDS在某成像光電跟蹤產(chǎn)品中的應(yīng)用

2.1 系統(tǒng)應(yīng)用簡介

某成像光電跟蹤產(chǎn)品信息處理平臺(tái)采用FPGA+DSP的設(shè)計(jì)框架,結(jié)構(gòu)框圖如圖2所示。

該信息處理平臺(tái)在FPGA和DSP外圍增加調(diào)理電路、A/D裝換器、PROM、SBSRAM、DPRAM、FLASH、電源及電源濾波電路等。FPGA+DSP架構(gòu)最大的特點(diǎn)是結(jié)構(gòu)靈活,適于模塊化設(shè)計(jì),能有效地提高算法效率,因而非常適用于成像系統(tǒng)的信息處理。從圖2可以看出,該系統(tǒng)通過FPGA,利用LVDS標(biāo)準(zhǔn)電路設(shè)計(jì)完成圖像數(shù)據(jù)的輸出。在該系統(tǒng)中,LVDS有三路差分輸出,其中兩路傳送數(shù)據(jù)(DA,DB),一路傳送時(shí)鐘(C)。傳送格式的要求如下:DA(DAX)為發(fā)送16位數(shù)據(jù)線,傳送系統(tǒng)給圖像采集設(shè)備的所有數(shù)據(jù)。包括每幀開頭發(fā)送一個(gè)幀計(jì)數(shù),幀正程發(fā)送圖像數(shù)據(jù)(實(shí)時(shí)圖像數(shù)據(jù)、濾波圖像數(shù)據(jù)及二值像數(shù)據(jù),按DSP要求傳送)。圖像數(shù)據(jù)為12位或14位,按需要傳送。16位數(shù)據(jù)的分配如下:最高位為奇偶校驗(yàn)位,“1”表示奇數(shù),“0”表示偶數(shù);次高位為正逆掃信號(hào),“1”表示正掃,“0”表示逆掃;在每幀的開頭,圖像數(shù)據(jù)輸出之前,添加2個(gè)驗(yàn)證字——FDB18540,作為接收方判斷每幀數(shù)據(jù)傳送的起始點(diǎn);幀正程開始后,傳圖像數(shù)據(jù)14位,如傳的是12位圖像數(shù),則其14,13位填0,后12位為圖像數(shù)據(jù)。

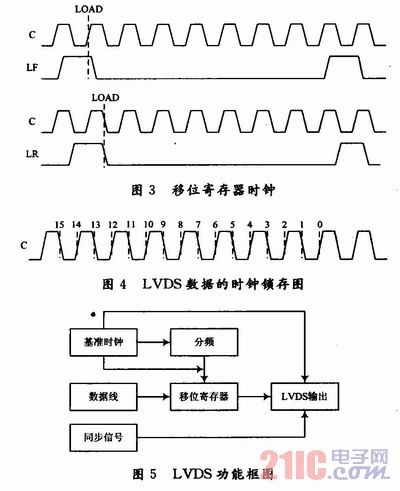

DB(DBX):發(fā)送同步信號(hào),每字同步,與首數(shù)據(jù)最高位同時(shí)發(fā)出,寬度為半個(gè)時(shí)鐘C(CX):時(shí)鐘信號(hào),始終保持。在LVDS設(shè)計(jì)實(shí)現(xiàn)過程中參考XAPP233的設(shè)計(jì)方法,16位數(shù)據(jù)通過并轉(zhuǎn)串移位寄存器進(jìn)行移位處理,將偶數(shù)位鎖存于傳送時(shí)鐘的上升沿,奇數(shù)位鎖存于傳送時(shí)鐘的下降沿。其輸入/輸出采用DDR技術(shù),保證雙沿觸發(fā)。移位寄存器時(shí)鐘示意圖如圖3所示。最終輸出數(shù)據(jù)的時(shí)鐘鎖存的位置如圖4所示。LVDS電路功能框圖如圖5所示。

2.2 系統(tǒng)中LVDS設(shè)計(jì)的要點(diǎn)

該系統(tǒng)中LVDS應(yīng)用于FPGA+DSP的高速數(shù)字處理平臺(tái),在設(shè)計(jì)及調(diào)試過程中,曾出現(xiàn)由于終端電阻匹配不當(dāng)帶來的噪聲較大的問題、由于通道選擇不當(dāng)帶來的信號(hào)畸變問題、以及印制板布線不當(dāng)帶來的信號(hào)串?dāng)_及噪聲等問題,通過這些實(shí)際問題的解決總結(jié)了以下幾點(diǎn)。

2.2.1 終端電阻

不管使用的LVDS傳輸通道是PCB線對還是電纜,LVDS要求使用一個(gè)與通道相匹配的終端電阻(100±20)Ω,以防止信號(hào)在通道終端發(fā)生反射,同時(shí)減少電磁干擾。該電阻終止了環(huán)流信號(hào),應(yīng)該將它盡可能靠近接收器輸入端放置。該系統(tǒng)使用了兩個(gè)阻值各為50 Ω的電阻串聯(lián),并在中間連接點(diǎn)通過一個(gè)電容接地,很好地濾去了共模噪聲。

2.2.2 通道(電纜和連接器)選擇

使用受控阻抗通道,差分阻抗約為100 Ω,不會(huì)引入較大的阻抗不連續(xù)性;當(dāng)電纜長度小于0.15 m時(shí),大部分電纜都能有效工作,當(dāng)電纜長度在0.15~10 m之間時(shí),CAT3(Categor 3)雙絞線對電纜效果好(本系統(tǒng)采用該設(shè)計(jì)),當(dāng)電纜長度于10 m,并且要求高速率傳輸時(shí),建議使用CAT5雙絞線對。

2.2.3 印制板設(shè)計(jì)

盡量使用多層板設(shè)計(jì)(該系統(tǒng)最終采用8層PCB板),保證LVDS信號(hào)、地、電源、TTL信號(hào)分處于不同的PCB層,或者至少處于不同的分區(qū);使TTL信號(hào)和LVDS信號(hào)相互隔離,最好將TTL和LVDS信號(hào)放在電源/地層隔離的不同層上;使LVDS驅(qū)動(dòng)器和接收器與LVDS端間連接盡可能短。電源層和地層應(yīng)盡可能使用粗線。

2.2.4 板上導(dǎo)線

微波傳輸線(microst rip)和帶狀線(stipline)都有具備良好的性能;前者一般具備更高的差分阻抗,不需要額外的過孔,后者則在信號(hào)間提供了更好的屏蔽。

2.2.5 差分線對

差分線對使用與傳輸媒質(zhì)的差分阻抗和終端電阻相匹配的受控阻抗線,并且使差分線對離開集成芯片后立刻盡可能地相互靠近(距離小于10 mm),這樣能減少反射并能確保耦合到的噪聲為共模噪聲。使差分線對的長度相互匹配以減少信號(hào)扭曲,防止引起信號(hào)間的相位差。而且2條差分線之間應(yīng)盡可能保持平行,以避免差分阻抗的不連續(xù)性。不要僅依賴自動(dòng)布線功能,而應(yīng)仔細(xì)修改以實(shí)現(xiàn)差分阻抗匹配并實(shí)現(xiàn)差分線的隔離。盡量減少過孔和使用90°折線來改變線跡走向,避免其他引起線路不連續(xù)性的因素。

2.2.6 抗噪聲設(shè)計(jì)

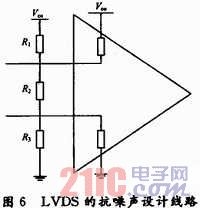

如果電纜感應(yīng)到的噪聲超過LVDS接收器內(nèi)部線路設(shè)計(jì)的容限,接收器就會(huì)不確定地開關(guān)或振蕩。在本系統(tǒng)中通過外加電阻來提高噪聲容限,如圖6所示。圖6中R1,R3是可選的外接電阻,用來提高噪聲容限,R1,R3取12 kΩ,R2取100Ω。

3 結(jié)語

該系統(tǒng)經(jīng)過內(nèi)場的高低溫、振動(dòng)、電磁兼容等試驗(yàn),同時(shí)經(jīng)過外場繞飛、系留及靶試。內(nèi)外場試驗(yàn)表明,某成像光電跟蹤產(chǎn)品利用LVDS穩(wěn)定可靠地進(jìn)行了圖像數(shù)據(jù)的傳輸及測試,解決了高速率、大容量、長距離的圖像數(shù)據(jù)傳輸問題,并具備良好的電磁兼容性。另外,該項(xiàng)技術(shù)不僅在某成像光電跟蹤產(chǎn)品中得到可靠驗(yàn)證,目前還被推廣應(yīng)用到其他數(shù)據(jù)傳輸系統(tǒng)中。