比較器可以比較一個模擬信號和另一個模擬信號或者參考信號,并且輸出比較得到的二進制信號,。這里所說的模擬信號是指在任何給定時刻幅值都連續(xù)變化的信號,。嚴格意義上講,二進制信號在任何時刻只能取得兩個給定值中的一個,。

比較器被廣泛使用于開關電源和數模轉換器中,,此外還應用于過零檢測系統(tǒng)(zero-crossing detectors)、峰值檢測系統(tǒng)(peak detectors),、全波整形系統(tǒng)(full-waverectifiers)等,。

1 比較器的設計

本文設計的比較器是一個高增益的三級比較器,第一級為普通差分放大器,,第二級為折疊式共源共柵差分放大器,,第三級為共源極放大器和一個推挽式反向放大器。另外還有一個為放大器提供偏置的偏置電路,。

1.1 比較器一級放大器

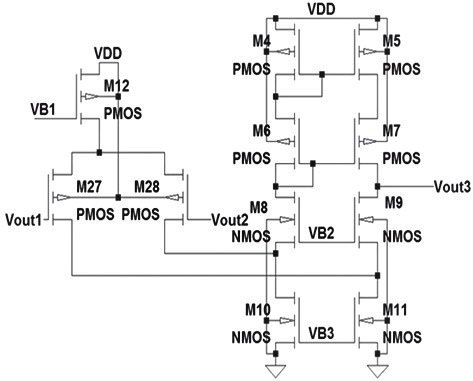

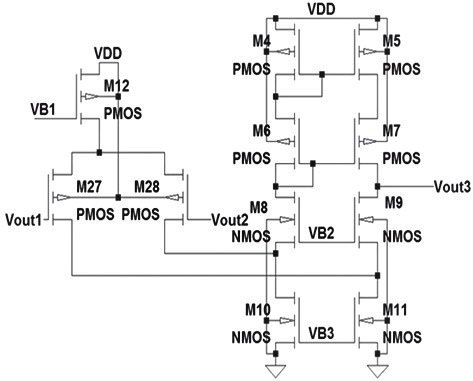

第一級放大器即比較器的輸入級電路,,如圖1所示,為普通結構的差分放大器,和帶隙基準電壓源的運算放大器的第一級結構基本相同,,所以不再對其進行分析,。

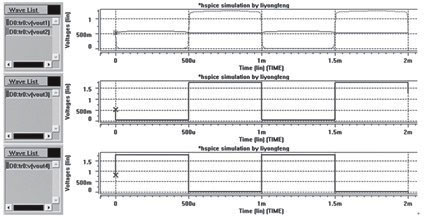

調節(jié)管子參數使其所有管子處于飽和區(qū),仿真其增益-頻率特性,,結果如圖2所示,。

圖1 比較器的輸入級

圖2 增益極折疊式共源共柵差分放大器

1.2 比較器第二級放大器

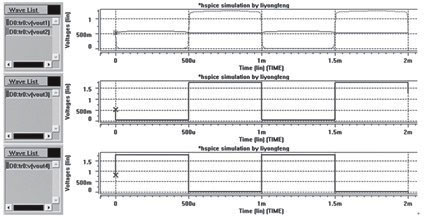

比較器的第二級放大器又稱中間級或增益極。采用PMOS管作為折疊式共源共柵結構的的輸入管,,電路如圖2所示,。PMOS管可以采用以襯源短接以消除襯偏效應。對其進行輸出增益仿真如圖3所示,。

圖3 放大級瞬時仿真波形

1.3 比較器輸出級

如圖4所示,,輸出級由M13和M14組成的共源極放大電路和M15和M16組成的推挽式反向放大器共同組成。

圖4 比較器的輸出級

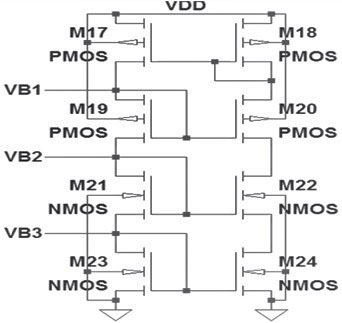

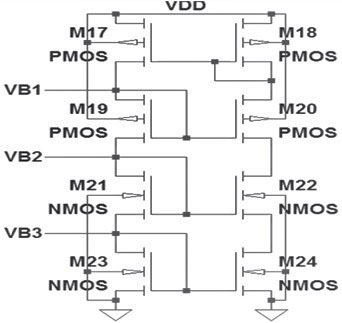

1.4 偏置電路設計

如圖5所示,,偏置電路采用共源共柵電流鏡的,,二極管連接的M19、M21和M23用來作為分壓電路,,調節(jié)管子參數使所有管子處于飽和區(qū),。

圖5 比較器偏置電路

比較器可以比較一個模擬信號和另一個模擬信號或者參考信號,并且輸出比較得到的二進制信號,。這里所說的模擬信號是指在任何給定時刻幅值都連續(xù)變化的信號。嚴格意義上講,,二進制信號在任何時刻只能取得兩個給定值中的一個,。

比較器被廣泛使用于開關電源和數模轉換器中,此外還應用于過零檢測系統(tǒng)(zero-crossing detectors),、峰值檢測系統(tǒng)(peak detectors),、全波整形系統(tǒng)(full-waverectifiers)等。

1 比較器的設計

本文設計的比較器是一個高增益的三級比較器,,第一級為普通差分放大器,,第二級為折疊式共源共柵差分放大器,第三級為共源極放大器和一個推挽式反向放大器,。另外還有一個為放大器提供偏置的偏置電路,。

1.1 比較器一級放大器

第一級放大器即比較器的輸入級電路,如圖1所示,,為普通結構的差分放大器,,和帶隙基準電壓源的運算放大器的第一級結構基本相同,所以不再對其進行分析,。

調節(jié)管子參數使其所有管子處于飽和區(qū),,仿真其增益-頻率特性,結果如圖2所示。

圖1 比較器的輸入級

圖2 增益極折疊式共源共柵差分放大器

1.2 比較器第二級放大器

比較器的第二級放大器又稱中間級或增益極,。采用PMOS管作為折疊式共源共柵結構的的輸入管,,電路如圖2所示。PMOS管可以采用以襯源短接以消除襯偏效應,。對其進行輸出增益仿真如圖3所示,。

圖3 放大級瞬時仿真波形

1.3 比較器輸出級

如圖4所示,輸出級由M13和M14組成的共源極放大電路和M15和M16組成的推挽式反向放大器共同組成,。

圖4 比較器的輸出級

1.4 偏置電路設計

如圖5所示,,偏置電路采用共源共柵電流鏡的,二極管連接的M19,、M21和M23用來作為分壓電路,,調節(jié)管子參數使所有管子處于飽和區(qū)。

圖5 比較器偏置電路

2 比較器的仿真結果分析

基于0.18μm CMOS工藝在Hspice下進行仿真,。采用電源電壓VDD=1.8V,。

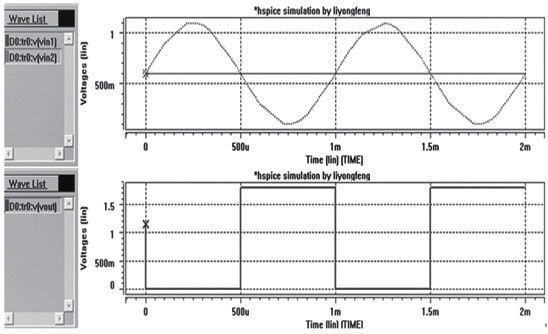

首先對本文設計的比較器進行瞬態(tài)仿真,當輸入Vin1=0.6V,,Vin2=sin(0.6 500m 1k)時,,輸入輸出波形如圖6所示。圖3所示的是一級輸出,、二級輸出和三級共源級輸出的波形,。

圖6 輸入輸出的瞬時仿真

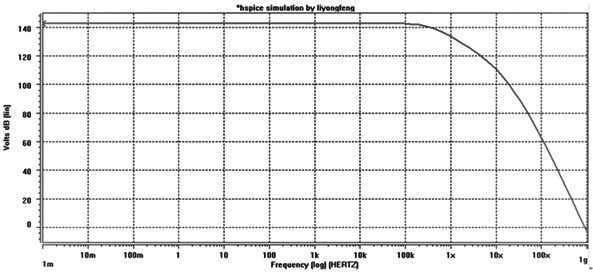

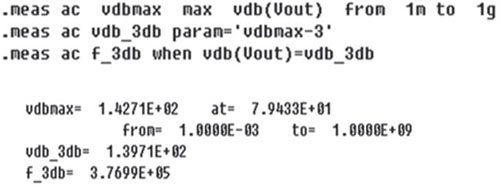

對輸出的增益進行仿真,如圖7所示,??梢娮畲笤鲆鏋?43dB。在-3dB處增益為143dB,,頻率為377kHz,。用。meas語句測試其最大增益,、-3dB增益和-3dB增益頻率如圖8所示,。

圖7 輸出總增益仿真

圖8 輸出增益和頻率的測試

3 結束語

文中電路圖在LTspice下得到netlist后,在Hspice中進行仿真,。文獻中增益為104dB,,工作頻率145kHz,文獻[2]的增益為104dB,,工作頻率為710kHz,。本文在結構上都采用三級結構,可見本文設計的比較器既可用作PWM比較器也可用于限流比較器,,其本質都是相同的,。