摘 要: 邏輯分析儀的現(xiàn)狀、發(fā)展趨勢及研制虛擬邏輯分析儀的必要性,論述了基于FPGA技術(shù)的虛擬邏輯分析儀的設(shè)計方案及具體實(shí)現(xiàn)方法,介紹了其中控制器的設(shè)計原理。將先進(jìn)的FPGA技術(shù)引入硬制版的設(shè)計中,為研制PC虛擬儀器提出了一種新思路;充分利用硬件軟化的思想,將儀器的諸多功能集成在軟件中實(shí)現(xiàn),利用面向?qū)ο蟆⒋翱诘燃夹g(shù),實(shí)現(xiàn)了靈活、通用的虛擬儀器面板功能。

關(guān)鍵詞: 虛擬儀器 虛擬邏輯分析儀(FVLA) 現(xiàn)場可編程門陣列(FPGA) 面向?qū)ο蠹夹g(shù) 控制器

電子技術(shù)的迅速發(fā)展從客觀上要求測試儀器向自動化及柔性化方向發(fā)展,基于微計算機(jī)的虛擬測試儀器的出現(xiàn)和廣泛使用,將對測試儀器產(chǎn)生極為深刻的影響[1]。虛擬儀器是指具有虛擬儀器面板的個人計算機(jī)儀器。操作人員通過友好的圖形界面及圖形化編程語言控制儀器的運(yùn)行,完成對被測試量的采集、分析、判斷、顯示、存儲及數(shù)據(jù)生成。虛擬儀器的發(fā)展依賴計算機(jī)技術(shù),可以肯定:隨著微計算機(jī)的發(fā)展,虛擬儀器將會逐步取代傳統(tǒng)的測試儀器而成為測試儀器的主流。軟件技術(shù)、I/O總線的發(fā)展及標(biāo)準(zhǔn)化進(jìn)程、DSP、可編程邏輯器件技術(shù)的發(fā)展都使這一趨勢成為可能。

邏輯分析儀(Logic Analyzer簡稱LA)也稱邏輯示波器,主要用于分析數(shù)字系統(tǒng)的邏輯關(guān)系,有效地解決越來越復(fù)雜的數(shù)字系統(tǒng)的檢測和故障診斷問題,是數(shù)據(jù)域測試儀器中最有用、最有代表性的一種儀器[2]。邏輯分析儀與個人計算機(jī)相結(jié)合(即虛擬邏輯分析儀)是近年來的一個新的發(fā)展方向,兩者的結(jié)合擴(kuò)展了邏輯分析儀的分析和計算能力,降低了成本,而且使儀器的通用性增強(qiáng),在這種情況下,邏輯分析儀作為微計算機(jī)的外設(shè),不再是獨(dú)立的完整儀器了,在邏輯分析儀中占有很大比重的控制電路、顯示電路、指示電路等功能全部由微計算機(jī)完成。虛擬邏輯分析儀(LA與PC相結(jié)合)具有許多優(yōu)勢:性能提高、成本降低、使用簡便和功能易于擴(kuò)展等[2],特別是高性能價格比,決定了LA與微機(jī)相結(jié)合的技術(shù)方案有著廣闊的前景。

國際上虛擬儀器發(fā)展十分迅速,而國內(nèi)基本處于起步階段。就目前來說,我國的許多科研單位、大學(xué)、生產(chǎn)部門依舊是傳統(tǒng)的測試儀器占據(jù)主導(dǎo)地位,微計算機(jī)與測試儀器基本上還處于互不相關(guān)的狀態(tài),這大大地影響了我國電子行業(yè)的發(fā)展。研究PC虛擬儀器是我們的當(dāng)務(wù)之急,尤其是在數(shù)據(jù)域測試中占核心地位的邏輯分析儀。實(shí)踐證明,PC虛擬儀器在技術(shù)上是可行的,也是十分適合中國國情的,具有極其光明的前途。

因此我們開展了虛擬儀器方面的研究工作,進(jìn)行了虛擬儀器及其相關(guān)技術(shù)的研究,并研制開發(fā)了新一代虛擬儀器——一種基于FPGA技術(shù)的虛擬邏輯分析儀(Visual Logic Analyzer,簡稱FVLA)。它是微機(jī)系統(tǒng)及數(shù)字電路設(shè)計、偵錯、軟件開發(fā)和仿真的理想儀器。

1 虛擬邏輯分析儀(FVLA)的總體設(shè)計方案

我們主要針對國內(nèi)需求,著重從性能價格比和實(shí)用的角度出發(fā),利用微機(jī)現(xiàn)有的軟、硬資源,與微機(jī)相結(jié)合開發(fā)研制虛擬邏輯分析儀(FVLA)。它是新型的數(shù)據(jù)域分析儀器,除具有傳統(tǒng)邏輯分析儀的一般功能外,還具有激勵信號發(fā)生功能、智能化輔助分析功能及全中文交互式的圖形用戶界面等性能。利用硬件軟化的思想,將FVLA的采樣部分即具有數(shù)據(jù)獲取能力的部分做成微機(jī)擴(kuò)展插卡,其它諸部分:控制、顯示等利用微機(jī)的軟件技術(shù)實(shí)現(xiàn)。

從實(shí)用性、研制周期、性能價格比等角度考慮,F(xiàn)VLA的研制分兩個版本,第一版完成基本邏輯分析儀功能及第二版帶激勵的邏輯分析儀功能。FVLA中占很大比重的控制電路、顯示電路、指示電路等功能全部由微計算機(jī)完成,其中顯示電路由監(jiān)視器代替,而控制電路等由軟件實(shí)現(xiàn)。利用面向?qū)ο蠹夹g(shù)及Windows消息機(jī)制結(jié)合Visual C++ MFC 4.21類庫完成FVLA控制軟件的設(shè)計及實(shí)現(xiàn),將復(fù)雜、繁瑣的虛擬邏輯分析儀控制面板諸多功能,集成在FVLA主控GUI中實(shí)現(xiàn),并提供智能化的輔助分析和特征分析功能。

FPGA是現(xiàn)場可編程門陣列(Field Programmable Gate Array,簡稱FPGA)。FPGA器件及其開發(fā)系統(tǒng)是開發(fā)大規(guī)模數(shù)字集成電路的新技術(shù),它將現(xiàn)代VLSI邏輯集成的優(yōu)點(diǎn)和可編程器件設(shè)計靈活,制作及上市快速的長處相結(jié)合,使設(shè)計者在FPGA開發(fā)系統(tǒng)軟件的支持下,現(xiàn)場直接根據(jù)系統(tǒng)要求定義和修改其邏輯功能,使一個包含數(shù)千個邏輯門的數(shù)字系統(tǒng)設(shè)計實(shí)現(xiàn),采用FPGA技術(shù),即可幾天內(nèi)完成,所以,無論從產(chǎn)品上市速度,還是以設(shè)計制作成本而言,在較大的應(yīng)用范圍內(nèi)FPGA均優(yōu)于掩膜設(shè)計制作的ASIC。因此我們將FVLA中關(guān)鍵的較復(fù)雜的采樣控制電路:觸發(fā)選擇、分頻選擇、存儲器控制邏輯等采用FPGA技術(shù)實(shí)現(xiàn)。

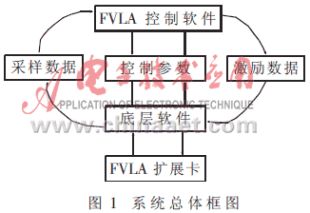

系統(tǒng)總體框圖如圖1。

FVLA硬件擴(kuò)展插卡

寄生在微機(jī)上,作為微機(jī)的功能擴(kuò)展卡,主要負(fù)責(zé)高速數(shù)據(jù)采集,存儲及高速地發(fā)出激勵的作用。

底層軟件

主要功能是對硬件初始化(對硬件中的FPGA進(jìn)行設(shè)置),對硬件控制、管理及為上層軟件提供一個簡潔的界面及數(shù)據(jù)傳輸。

FVLA控制軟件

提供功能完善的圖形用戶界面,代替?zhèn)鹘y(tǒng)邏輯分析儀繁鎖、復(fù)雜的控制面板功能,完成用戶對FVLA的工作參數(shù)的設(shè)定及對采樣的數(shù)據(jù)處理;提供定時圖、狀態(tài)表等多種顯示分析功能;產(chǎn)生激勵信號,驅(qū)動被測數(shù)字系統(tǒng)被動工作等。

2 硬件插卡的設(shè)計思想

FVLA硬件結(jié)構(gòu)如圖2所示。

· I/O接口:接收微機(jī)送來的控制字或激勵數(shù)據(jù),將狀態(tài)字和采樣數(shù)據(jù)發(fā)送給微機(jī);

控制器:控制采樣頻率,控制觸發(fā)方式及觸發(fā)通道,為高速存儲器提供地址及讀寫時序等,控制系統(tǒng)實(shí)現(xiàn)不同的工作模式,這部分是FVLA比較復(fù)雜和關(guān)鍵的電路部分;

· 高速存儲器:保存采樣數(shù)據(jù)和激勵數(shù)據(jù);

· 激勵部分:處理激勵數(shù)據(jù),激勵被測系統(tǒng)按指定方式工作;

· 采樣部分:捕獲數(shù)據(jù),通過探頭或電纜將被測系統(tǒng)的模擬量轉(zhuǎn)換為高低電平二進(jìn)制數(shù)據(jù);

· ASIC測試平臺:是FVLA同高級綜合系統(tǒng)的接口,其上加載被測試ASIC,通過扁平電纜與FVLA相連,構(gòu)成完整的ASIC測試系統(tǒng)。

由于FPGA(現(xiàn)場可編程門陣列)可實(shí)現(xiàn)無限次地反復(fù)編程,快速方便實(shí)用,具有可現(xiàn)場模擬調(diào)試驗(yàn)證等特點(diǎn),所以本系統(tǒng)中比較復(fù)雜的控制器部分,采樣部分、激勵部分、I/O接口部分都采用FPGA實(shí)現(xiàn);其它的由外圍芯片組成。外圍芯片上主要有RAM及數(shù)據(jù)緩沖、鎖存等數(shù)據(jù)通道部分。

3 控制軟件的功能設(shè)計

控制軟件主要包含以下八個功能模塊:

· FVLA工作參數(shù)設(shè)定模塊:主要完成FVLA采樣時鐘的設(shè)定,觸發(fā)方式選擇,觸發(fā)通道的設(shè)定,采樣通道數(shù),工作模式的選擇,硬件主時鐘,硬端口地址的設(shè)定等。

· 信號、硬通道映射模塊:對物理通道重新分組、命名形成定時圖等各顯示模塊中待觀察的信號,與被測系統(tǒng)中的各信號保持一致,便于理解分析。信號流覽模塊在FVLA工作的任何時刻都可激活,以利于用戶了解高層信號所對應(yīng)的物理通道信息。

· 定時圖顯示模塊:這是FVLA最基本的顯示方式,它把每一采樣通道所采集的信息在屏幕上顯示成一行偽方波,橫向表示時間,縱向表示若干信號的離散值,信號可任意分組,支持拖放,即任一波形可隨時改變顯示位置,提供二個活動桿,實(shí)現(xiàn)相對、絕對時間分析,用戶拖動活動桿時,可顯示此活動桿處的各信號的值,信號名、時間等,此外波形可任意縮小、放大,即可顯示全局,又可顯示局部,還可提供輔助分析能力,智能比較,快速查詢等。

· 狀態(tài)表顯示模塊:狀態(tài)表是用字符組成不同形式的表格顯示數(shù)字系統(tǒng)的邏輯狀態(tài)或邏輯程序,不同信號可選用不同碼字顯示,如地址信號可選用十六進(jìn)制,而控制信號則選用二進(jìn)制方式顯示。

· 狀態(tài)圖顯示:狀態(tài)圖顯示某一信號(組)的不同值出現(xiàn)的次數(shù),可跟蹤和刷新顯示,“基準(zhǔn)線”移動時在狀態(tài)條上顯示信號的值及出現(xiàn)頻度。

· 狀態(tài)直方圖顯示模塊:狀態(tài)直方圖是對某一信號(向量)的進(jìn)一步分析,可將該信號的取值定義若干小范圍,橫向表示范圍,縱向表示每一范圍出現(xiàn)的頻度。

· 時間間隔圖:統(tǒng)計和顯示事件間隔,分若干時間間隔段,用直方圖表示。

· 激勵信號生成模塊:主要用于生成激勵信號,提供激勵文件編輯功能,擁有常見編輯器的基本功能,提供一個公用接口,接收其它編輯器生成的激勵格式文本文件,例如Xilinx公司 的XNF格式文件,將其轉(zhuǎn)換為定時圖能顯示的格式文件。

4 FVLA控制器的(FPGA)的設(shè)計原理

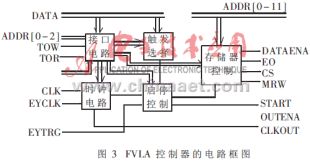

FVLA控制器的電路框圖如圖3所示。

4.1 FVLA控制器(FPGA)的外部特性

FVLA控制器版本1(普通邏輯分析儀)和版本2(帶激勵的)具有相同的外部特性,地址空間分配兼容,送控制字的順序和方法等均相同。控制器的引腳可分為三類:與微機(jī)(PC機(jī))接口有關(guān)的信號、 與高速存儲器有關(guān)的信號、其它信號:諸如系統(tǒng)內(nèi)部時鐘信號,外部時鐘,時鐘輸出,啟動采樣信號,采樣數(shù)據(jù)鎖存信號,激勵數(shù)據(jù)鎖存信號等。

地址空間是靈活的,可以通過測試儀插件板上的DIP開關(guān)設(shè)定。

主要包括三個控制字:控制字1包含分頻控制、觸發(fā)控制、工作模式控制;控制字2包含分頻控制、觸發(fā)通道選擇;控制字3包含采樣和激勵地址設(shè)定。

工作模式共有8種:鍵控采樣、讀采樣數(shù)據(jù)、單純采樣、單純采樣毛刺檢測、單純激勵、激勵采樣、激勵采樣毛刺檢測、鍵控激勵采樣。由第一控制字的末3位指定。

4.2 FVLA控制器(FPGA)的內(nèi)部原理

FVLA控制器第一版本與第二版本(帶激勵)的邏輯分析儀的電路的總體結(jié)構(gòu)相同,僅是接口電路和高速存儲器控制部分不同。

基本分為五個部分:接口電路、時鐘電路、觸發(fā)選擇、啟停控制、存儲器控制。接口電路從微機(jī)總線接收控制字,并將它們鎖存,然后再送給其它4個部分,時鐘電路對測試儀插件板本身的時鐘CLK或外部時鐘EXCLK進(jìn)行分頻處理,以獲得各種采樣時鐘,然后送到啟停電路,觸發(fā)電路從32個(或用戶設(shè)定)通道中識別觸發(fā)信號,將結(jié)果送給啟停電路;啟停控制部分根據(jù)觸發(fā)狀態(tài),時鐘內(nèi)部的計數(shù)值來控制存儲器的啟與停,存儲器控制部分則根據(jù)各種工作模式的不同要求,形成高速存儲器的控制信號及FPGA外部電路所需的各種控制信號。

4.3 FVLA存儲器的控制原理

這部分用來產(chǎn)生存儲器以及FPGA外部電路所需的控制信號。不同的工作模式所需的控制信號不同,二個版本此部分的實(shí)現(xiàn)差別比較大。

4.3.1 版本1的存儲器控制

圖4為存儲器控制原理圖。地址計數(shù)器用來形成存儲器所需的地址信號。在采樣模式,由測試儀插件板上的時鐘CLK作為計數(shù)器的時鐘,并按一定的時序要求產(chǎn)生各種控制信號;在讀模式,由ADDRCLK作為計數(shù)器時鐘,并產(chǎn)生控制信號,ADDRCLK是由讀XX2產(chǎn)生的。

4.3.2 版本2的存儲器控制

版本2的電路共有8種工作模式,與版本1相比較,主要增加了以下功能:

·實(shí)現(xiàn)激勵數(shù)據(jù)與采樣數(shù)據(jù)共用一個高速存儲器;

·實(shí)現(xiàn)靈活設(shè)定激勵數(shù)據(jù)與采樣數(shù)據(jù)在高速存儲器占用空間的比值;

·實(shí)現(xiàn)每次激勵所對應(yīng)的采樣次數(shù)的設(shè)定與變化;

·實(shí)現(xiàn)單純激勵時所需的時序信號;

·實(shí)現(xiàn)激勵采樣時所需的控制信號。

具體內(nèi)部電路圖如下:

IC1,IC2為兩個地址計數(shù)器,分別為激勵地址計數(shù)器和采樣地址計數(shù)器,IC3為二選一多路器,據(jù)不同控制信號,將IC1,IC2選出輸出到地址總線,實(shí)現(xiàn)在一個存儲器中共存激勵數(shù)據(jù)和采樣數(shù)據(jù)。初始化后,這二個地址計數(shù)器均取控制字3中的設(shè)定值(邊界地址),采樣計數(shù)器為UP計數(shù),計數(shù)滿后再裝入邊界地址,如此重復(fù)地采樣,存儲數(shù)據(jù),使采樣數(shù)據(jù)局限于邊界地址和FFH之間。激勵地址計數(shù)器為DOWN計數(shù),計數(shù)到0后再將邊界地址裝入使激勵數(shù)據(jù)局限于0到邊界地址之間。

IC4為采樣與激勵切換控制器,通常處于采樣狀態(tài),采樣地址計數(shù)器與地址總線接通,并產(chǎn)生共享存儲器的控制信號,當(dāng)采樣滿N次時,切換到激勵狀態(tài),使激勵地址計數(shù)器與地址總線接通,并產(chǎn)生讀存的控制信號。采樣個數(shù)由控制字3的高4位設(shè)定。

CONTRL為一組合邏輯網(wǎng)絡(luò),據(jù)M2~M0采樣的不同的工作模式,采樣激勵切換控制器的輸出TC以及時鐘CLK,產(chǎn)生存貯器所需的各種控制信號,其邏輯表達(dá)式如下:

STMCLK=STM(M5+M4)+CLK·M4+ADDRCLK·M7

CMPCLK=ADDRCLK(M0+M1)+CLK(M2+M3+M5+M6)+STM(M5+M6)

STMENA=M5+M6

STMMVL=STM(M5+M6)+M4+M7

EO=M0+M2+M3+SONTENA(M5+M6)+M7

CS=ADDRCLK(M0+M1+M7)+CLK(M2+M3+M5+M6+M4)

MRW=CS(M0+M2+M3+M5+M6+M7)+STM(M5+M6)+M1+M4

DATAEN=CS(M0+M2+M3)+SMPCLK(M5+M6)+M1+M4+M7

ONTENA=M0+M1+M2+M3+STM(M5+M6)+CSM4

OE=M0+M1+M2+M5+M6+M4+CS·M7

5 與同類產(chǎn)品的分析比較

目前市場上已有幾種微機(jī)用邏輯分析儀卡及配套軟件。但有的速度較慢,有的仍使用DOS平臺。尚未見到帶有激勵信號發(fā)生器的產(chǎn)品。本項(xiàng)產(chǎn)品與這些產(chǎn)品相比具有以下特點(diǎn):

· 虛擬儀器擴(kuò)展卡采用FPGA技術(shù)實(shí)現(xiàn),使印制版大為縮小,并且可在不重新設(shè)計印制板的情況下進(jìn)行硬件的改進(jìn);

· 具有激勵信號發(fā)生器的功能,能夠?qū)崟r向被測系統(tǒng)發(fā)出激勵信號;

· 用同一塊印制板,通過對FPGA不同的編程來實(shí)現(xiàn)邏輯分析儀和激勵信號發(fā)生器兩種儀器;

· 提供DOS和Windows 兩種平臺,硬件要求低;

· 可以將預(yù)先測得的正常波形存儲,作為標(biāo)準(zhǔn);測試的波形可以與之疊印顯示,人工比較,也可以自動地與之比較,比較的模糊程度可由用戶自行設(shè)定。

· 總線信號可以用十六進(jìn)制“捆綁”顯示, 也可以展開成單信號線顯示;

· 與高級綜合系統(tǒng)相聯(lián)結(jié),可接收VHDL模擬器的激勵向量,用該向量生成被測系統(tǒng)所需的激勵信號。

總之,PC總線虛擬儀器是一個新興而又前途光明的研究方向,研究PC虛擬儀器是我們的當(dāng)務(wù)之急。本文主要針對國內(nèi)實(shí)際情況及數(shù)據(jù)域測試要求,研究并探討了一個實(shí)際的PC虛擬儀器——一種基于FPGA技術(shù)的虛擬邏輯分析儀的設(shè)計思想及實(shí)現(xiàn)。充分利用微機(jī)的軟、硬資源,著重從性能價格比,實(shí)用角度出發(fā)設(shè)計、研制虛擬儀器。充分利用“軟件即儀器”思想,將邏輯分析儀除采樣部分外的其它功能設(shè)備均用軟件實(shí)現(xiàn)。利用FPGA技術(shù),將FVLA卡上的關(guān)鍵控制電路做入FPGA來實(shí)現(xiàn)硬制卡。利用面向?qū)ο蠹夹g(shù)及Windows圖形用戶界面技術(shù)設(shè)計并實(shí)現(xiàn)了FVLA的控制軟件,將復(fù)雜繁鎖的傳統(tǒng)邏輯分析儀面板上諸多功能集成在FVLA主控GUI中實(shí)現(xiàn),提供了全中文、多種顯示、操作方便、靈活、直觀等其它同類產(chǎn)品不可比擬的軟件性能;并具有激勵信號發(fā)生功能。此儀器目前已進(jìn)入試用階段,在研制末敏彈時,用其測試末敏彈ASIC的輸入、內(nèi)部狀態(tài)(為了檢測內(nèi)部狀態(tài),將一些內(nèi)部信號接到輸出管腳)和輸出之間的邏輯關(guān)系,可直觀地觀察多路信號,簡化和縮短了研制周期。實(shí)踐證明虛擬儀器技術(shù)是可行的,且具有諸多優(yōu)點(diǎn),尤適合中國現(xiàn)狀。將FPGA技術(shù)引入硬制卡的研制中,為研制PC虛擬邏輯分析儀提供了一種新思路。

參考文獻(xiàn)

1 劉 陽.虛擬儀器的現(xiàn)狀及發(fā)展趨勢.電子技術(shù)應(yīng)用,1996;(21)4

2 Logic analyxer.EDN.1986;(29)3

3 朱明程.FPGA技術(shù)的最新發(fā)展.電子技術(shù)應(yīng)用,1997;(22)2

4 朱明程.FPGA原理及應(yīng)用設(shè)計.北京:電子工業(yè)出版社,1994

5 Logic analysis by telephone-let your teriniml do the walking EDN.March,1989;(20)

6 林 君,程德福著.微型計算機(jī)卡式儀器原理、設(shè)計與應(yīng)用.北京:國防工業(yè)出版社,1990;(11)

7 高德遠(yuǎn),馬婉良譯著.Xilinx現(xiàn)場可編程門陣列及其應(yīng)用.西安:西北工業(yè)大學(xué)出版社,1996;(10)