本文設(shè)計了一種采用增益增強(qiáng)結(jié)構(gòu)的帶開關(guān)電容共模反饋的折疊式共源共柵跨導(dǎo)運(yùn)算放大器,可用于流水線結(jié)構(gòu)的A/D中。出于對性能及版圖因素的考慮,采用了單端放大器作為增益提高輔助放大器。并通過改進(jìn)共模負(fù)反饋電路,使得放大器輸出共模反饋電壓穩(wěn)定更快,抖動更小。本設(shè)計在Cadence環(huán)境下對運(yùn)放的電路和版圖進(jìn)行了仿真。結(jié)果表明,放大器的各項性能參數(shù)達(dá)到了理想的效果。

1 電路結(jié)構(gòu)的分析與設(shè)計

CMOS跨導(dǎo)運(yùn)算放大器常用結(jié)構(gòu)有兩級放大結(jié)構(gòu)、套筒結(jié)構(gòu)和折疊共源共柵結(jié)構(gòu)等形式。兩級放大結(jié)構(gòu)的運(yùn)放電路結(jié)構(gòu)雖然具有高增益、高擺幅等優(yōu)點(diǎn),但由于每一級至少引入一個極點(diǎn),為了保障整個放大器的相頻特性滿足要求,需要額外的頻率補(bǔ)償電路,從而提升了放大器的電流和功耗,限制了放大器帶寬,同時降低了放大器速度,因此不能滿足本設(shè)計中對于運(yùn)放帶寬和速度的要求。套筒式結(jié)構(gòu)雖然具有較高的增益、較好頻率特性及較低功耗,但是受到結(jié)構(gòu)限制,其輸出擺幅和共模輸入范圍小,不滿足設(shè)計要求。折疊式共源共柵結(jié)構(gòu)針對套筒結(jié)構(gòu)輸出擺幅小的缺點(diǎn)進(jìn)行改進(jìn),通過增加電路支數(shù),提高功耗,在提供較高的增益前提下,又滿足了大帶寬、高擺幅和高速的要求。通過對折疊共源共柵結(jié)構(gòu)應(yīng)用增益增強(qiáng)技術(shù),可以在不影響信號帶寬、壓擺率和相位特性的情況下進(jìn)一步提高電路直流增益。因此,針對本設(shè)計的特殊要求,選取了應(yīng)用增益增強(qiáng)技術(shù)的折疊式共源共柵結(jié)構(gòu)。

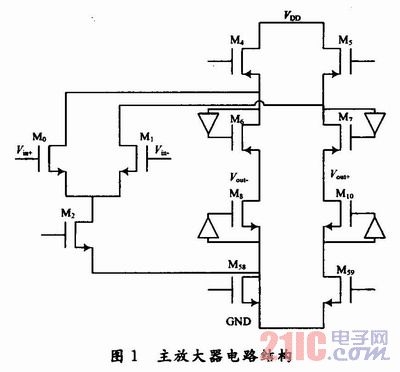

1.1 主運(yùn)放電路

本文設(shè)計的折疊共源共柵運(yùn)算放大器如圖1所示。M0,M1為差分輸入對管;M2為差分對管恒流源;M4,M5為電流源;M6,M7為共柵管;M8,M10,M58,M59為共源共柵電流源負(fù)載。由于NMOS管的載流子遷移率更高,采用NMOS管作差分輸入級可提高運(yùn)放增益和帶寬。

當(dāng)無增益提高輔助運(yùn)放時,主運(yùn)放的小信號電壓增益為:

可見,與基本的恒流源負(fù)載放大電路相比,輸出節(jié)點(diǎn)的輸出電阻增大gmRout倍,所以共源共柵結(jié)構(gòu)的運(yùn)算放大器能夠提供高增益。

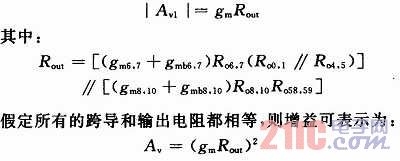

1.2 開關(guān)電容共模負(fù)反饋電路

由于折疊共源共柵放大器需要極其精準(zhǔn)的偏置電壓才能使電路輸出共模穩(wěn)定在一個固定值,因此必須引入一個共模負(fù)反饋電路,來使整個電路的輸出共模穩(wěn)定在要求的輸出電壓共模上。常用的共模負(fù)反饋電路分為連續(xù)時間型共模負(fù)反饋和開關(guān)電容共模負(fù)反饋兩種。由于開關(guān)電容共模負(fù)反饋即無靜態(tài)功耗,又對放大器本身有較小的影響,因此本設(shè)計中選擇了開關(guān)電容共模負(fù)反饋電路來穩(wěn)定輸出共模。圖2為傳統(tǒng)的開關(guān)電容共模反饋電路,out,out-為差分輸出電壓信號,clock1,clock2為兩相不交疊時鐘信號,Vcm為供比較的參考電壓,等于希望輸出的共模電壓;為了提供大的輸出擺幅,通常取電源電壓的一半,Vt為偏置電路產(chǎn)生的偏置電壓,Vb1為產(chǎn)生的調(diào)節(jié)電壓,用于穩(wěn)定輸出共模電壓。

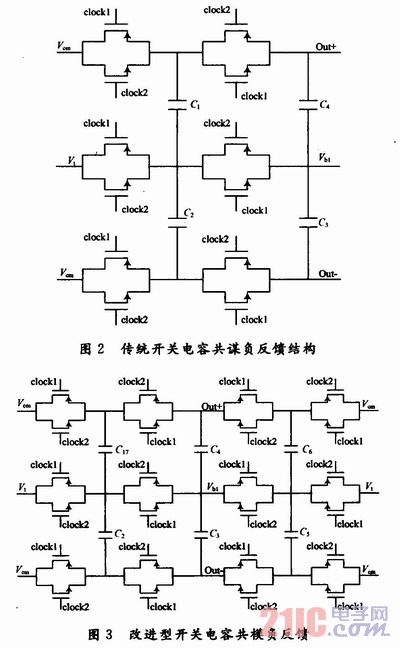

由于開關(guān)電容共模負(fù)反饋需要不停計算輸出共模和Vcm之間的差值來控制放大器,使其輸出共模穩(wěn)定在需要的電壓值上。對于傳統(tǒng)的開關(guān)電容共模負(fù)反饋電路,一個時鐘周期內(nèi)有半個時鐘周期需要C1,C2兩個電容用來取Vcm與Vt的差值,不能用來和輸出共模作用產(chǎn)生反饋電壓,因此共模電平建立速度較慢,因此我們再引入一組采樣電容,使兩組采樣電容采集Vcm與Vt的差值,分別在不同的時鐘周期與輸出電壓的共模進(jìn)行計算。這樣電路減小了共模反饋電壓的建立時間,減小了由于開關(guān)開啟關(guān)斷而造成的反饋電壓的抖動。改進(jìn)后的共模負(fù)反饋電路如圖3所示。

由于開關(guān)定容共模負(fù)反饋電路中的電容是直接掛在輸出節(jié)點(diǎn)上的,過大的電容值會降低放大器的帶寬和壓擺率,同時,為了減小動態(tài)開關(guān)動作導(dǎo)致的時鐘饋通效應(yīng)以及其他寄生雜散電容的影響和后端工藝精度等問題,該電容值也不能太小。因此本設(shè)計中我們?nèi)∷须娙荽笮?.5pF。

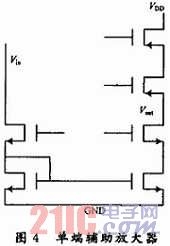

1.3 用于增益提高的輔助放大器電路

采用增益增強(qiáng)技術(shù),能夠有效地提高運(yùn)算放大器的直流增益,且不影響其速度。考慮到版圖布局對稱對于減小放大器失調(diào)的貢獻(xiàn),本設(shè)計中引入4個單端電流鏡共源共柵放大器作為增益提高放大器,分成兩組分別用于提高從共柵管處的等效電阻和共源共柵電流鏡的等效電阻,從而極大的提高了直流增益。輔助放大器采用電流輸入,通過輸入管尺寸與相對應(yīng)共柵器件尺寸的比例決定輔助放大器從主放電路中輸入的電流。對比傳統(tǒng)的差分結(jié)構(gòu),單端放大器可以更好的對稱分布在主放大器版圖兩側(cè),而由于放大器采用等比于主支路的電流輸入,相對于電壓輸入的放大器,消除了由于輸入共模電壓變化產(chǎn)生的影響。輔助放大器結(jié)構(gòu)如圖4所示。

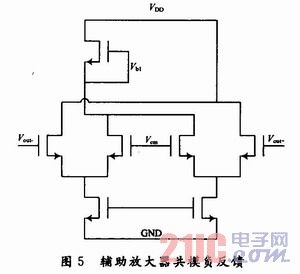

由于輔助放大器輸出擺幅有限,增益較高,故選取了采用差分對管取樣的共模負(fù)反饋結(jié)構(gòu),這種結(jié)構(gòu)會限制放大器輸出擺幅,但卻不會影響放大器增益,并且功耗較低,因此適合用于輔助放大器中。共模負(fù)反饋電路如圖5所示。

1.4 偏置電路

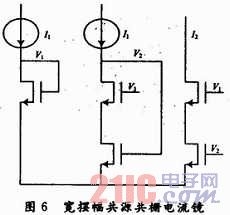

由于整個電路中有許多共源共柵管需要提供偏壓,因此采用了共源共柵寬擺幅電流鏡來對這些管子提供偏置,寬擺幅共源共柵電流鏡在保證電流復(fù)制精度的同時提高了擺幅,使得電路在保證輸出擺幅的同時保持正常工作。寬擺幅共源共柵電流鏡電路圖如圖6所示,其中I2=I1。

2 電路仿真結(jié)果

整個運(yùn)放及其偏置電路采用SMIC 0.18μmCMOS混合信號工藝進(jìn)行設(shè)計,并在Cadence環(huán)境下用Specture進(jìn)行模擬仿真,電源電壓3.3V,負(fù)載電容3 pF。對電路進(jìn)行AC仿真,仿真結(jié)果顯示電路直流增益119.3 dB,單位增益帶寬378.1 MHz,相位裕度60°,如圖7所示。

放大器建立到輸出電壓0.1%精度時的建立時間為7.9 ns,測試波形如圖8所示。

共模輸入范圍600mV~3.3V;電壓輸出范圍0.6~3.1V;功耗39mW。

3 版圖設(shè)計

整體電路包括1個主放大器,2個gainboost和1個共模負(fù)反饋,主放大器和gainboost各有自己的偏置電路。gainboost的偏置電路和gai-nboost放大器靠近放置以使連線最短,2個gainboot分別放在主放大器兩側(cè)以使總體版圖對稱,開關(guān)電容共模負(fù)反饋放在主放大器下面以使out,out-和Vb1連線最短。主放大器做ABAB匹配,采用雙側(cè)供電,以保證差模信號較好匹配,主放大器偏置分拆在主放大器兩側(cè),以使總體版圖形狀更加規(guī)則整齊,節(jié)省面積。

4 結(jié)語

介紹了一種折疊式共源共柵運(yùn)算放大器的設(shè)計。實際的設(shè)計仿真值為:小信號低頻電壓增益119.3 dB;單位增益帶寬378.1 MHz;相位裕度60°;建立時間7.9 ns;電源電壓3.3 V;共模輸入范圍600 mV~3.3 V;電壓輸出范圍0.6~3.1 V;負(fù)載電容3 pF;功耗為39 mW。整個設(shè)計滿足設(shè)計指標(biāo)要求,并應(yīng)用于欠采樣技術(shù)的12 b,60 MHz流水線ADC設(shè)計中。