摘 要:飛行器自毀系統(tǒng)是飛行器的重要組成部分,它的可靠性和穩(wěn)定性是飛行器可靠工作的基礎(chǔ),。分析飛行器自毀系統(tǒng)工作原理,,采用復(fù)雜可編程邏輯器件(CPLD)實(shí)現(xiàn)了飛行器自毀系統(tǒng)設(shè)計(jì),結(jié)合CPLD的特點(diǎn),提出一種基于改進(jìn)型有限狀態(tài)機(jī)" title="有限狀態(tài)機(jī)">有限狀態(tài)機(jī)的飛行器自毀系統(tǒng)時(shí)序控制" title="時(shí)序控制">時(shí)序控制的設(shè)計(jì)方法,,并在CPLD中予以實(shí)現(xiàn),。仿真及實(shí)驗(yàn)表明,基于有限狀態(tài)機(jī)的飛行器自毀系統(tǒng)定時(shí)精度達(dá)到納秒級(jí),,可以有效地控制自毀信號(hào)輸出并消除毛刺現(xiàn)象,,很好地滿足系統(tǒng)性能要求。該方法具有結(jié)構(gòu)簡(jiǎn)單緊湊,、成本低,、可靠性高、精度高等優(yōu)點(diǎn),。

關(guān)鍵詞:飛行器,;自毀系統(tǒng);有限狀態(tài)機(jī),;時(shí)序控制

O 引 言

飛行器自毀系統(tǒng)是飛行器的重要組成部分,,它具有非常重要的軍事及民用價(jià)值。飛行器自毀系統(tǒng)主要是實(shí)現(xiàn)飛行器在非正常飛行狀態(tài)" title="飛行狀態(tài)">飛行狀態(tài)時(shí)的可靠自毀,。飛行器按正常狀態(tài)飛行,,如果出現(xiàn)異常可以通過外部的飛行狀態(tài)參數(shù)傳感器及自毀電路控制自身自毀,。隨著飛行器研制技術(shù)的不斷發(fā)展,,對(duì)飛行器自毀系統(tǒng)小型化、模塊化,、通用化的要求越來越迫切,,CPLD的出現(xiàn)可以滿足這一要求。由于CPLD硬件電路的特點(diǎn),,必須研究適合CPLD硬件架構(gòu)的設(shè)計(jì)方法,,以達(dá)到系統(tǒng)在運(yùn)行速度與資源消耗上的平衡。有限狀態(tài)機(jī)及其技術(shù)是實(shí)用數(shù)字系統(tǒng)設(shè)計(jì)中實(shí)現(xiàn)高效率高可靠邏輯控制的重要途徑,,有限狀態(tài)機(jī)是一種簡(jiǎn)單,、結(jié)構(gòu)清晰、設(shè)計(jì)靈活的方法,,它易于建立,、理解和維護(hù),特別應(yīng)用在具有大量狀態(tài)轉(zhuǎn)移和復(fù)雜時(shí)序控制的系統(tǒng)中,,更顯其優(yōu)勢(shì),。這里針對(duì)自毀系統(tǒng)的特點(diǎn),提出一種符合CPLD結(jié)構(gòu),、基于有限狀態(tài)機(jī)的設(shè)計(jì)方法,。

l 自毀系統(tǒng)硬件設(shè)計(jì)

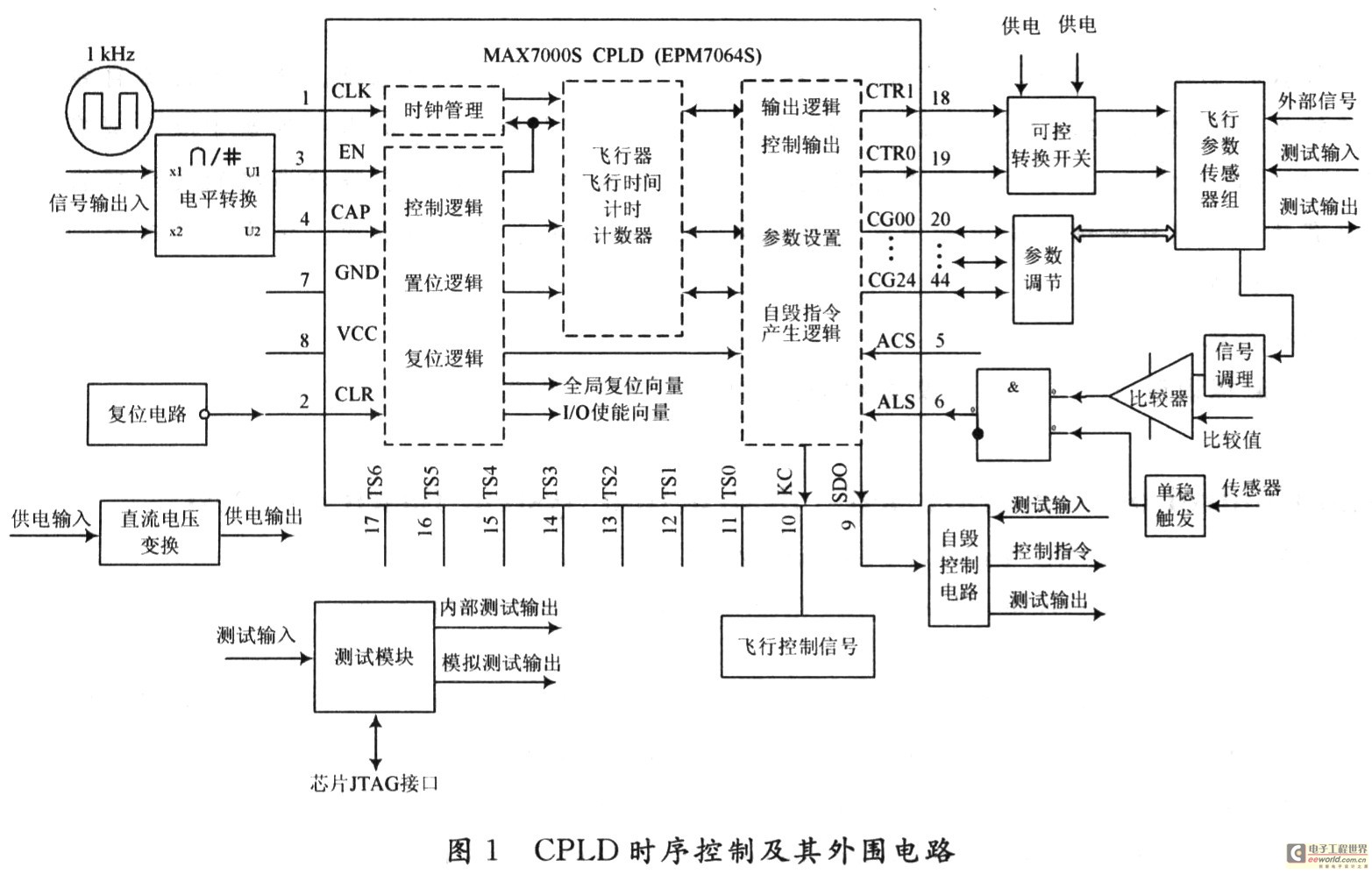

硬件設(shè)計(jì)采用以高性能CPLD芯片為核心的數(shù)字電路和高性能運(yùn)算放大器及飛行參數(shù)傳感器組為主要元件的模擬電路相結(jié)合的方案,。系統(tǒng)主要由系統(tǒng)時(shí)鐘、CPLD控制芯片,、飛行參數(shù)傳感器組,、傳感器組輸出判斷與產(chǎn)生電路、自毀控制邏輯,、測(cè)試模塊和電源等模塊組成,。該設(shè)計(jì)使用Altera公司的EPM7064SLC44-10芯片,其內(nèi)部包含有64個(gè)宏單元,,1 250個(gè)可用的系統(tǒng)門,,引腳到引腳的邏輯延遲時(shí)間為5.0 ns,計(jì)數(shù)器工作頻率可達(dá)175.4 MHz,。

用CPLD實(shí)現(xiàn)上述自毀條件的時(shí)序控制邏輯的核心電路及其外圍電路如圖1所示,。CPLD芯片為整個(gè)系統(tǒng)的核心,它用來實(shí)現(xiàn)計(jì)時(shí)以及整個(gè)系統(tǒng)的時(shí)序控制,。直流電壓變換電路用于將輸入的直流電壓轉(zhuǎn)換成EPM7064S所需的電壓,,以及外圍電路所需的工作電壓。系統(tǒng)時(shí)鐘電路為計(jì)時(shí)裝置提供穩(wěn)定的時(shí)鐘信號(hào)及后續(xù)分頻使用的時(shí)鐘基準(zhǔn),;電平轉(zhuǎn)換電路將飛行器上輸入信號(hào)" title="輸入信號(hào)">輸入信號(hào)進(jìn)行調(diào)理后轉(zhuǎn)換為芯片可識(shí)別的TTL/CMOS電平標(biāo)準(zhǔn),;復(fù)位電路在系統(tǒng)上電后給控制芯片提供復(fù)位信號(hào)。

飛行參數(shù)傳感器組電路用來實(shí)時(shí)監(jiān)控飛行器的各項(xiàng)指標(biāo),,當(dāng)飛行狀態(tài)出現(xiàn)異常時(shí)則由傳感器組產(chǎn)生相應(yīng)模擬值到由高性能運(yùn)算放大器及比較器為主要元件的模擬電路,。模擬電路對(duì)傳感器的輸入值進(jìn)行處理后送到CPLD時(shí)序控制模塊中??煽亻_關(guān)能通過對(duì)CPLD編程實(shí)現(xiàn)多路轉(zhuǎn)換,,從而使被監(jiān)控的飛行參數(shù)傳感器改變,進(jìn)而改變飛行器的自毀條件,。通過CPLD進(jìn)行飛行器內(nèi)部時(shí)序控制,,最后輸出的自毀指令輸入到飛行控制信號(hào)模塊中,從而改變飛行器的飛行狀態(tài),,使之自毀,。

2 有限狀態(tài)機(jī)模型及選擇

2.1 有限狀態(tài)機(jī)模型

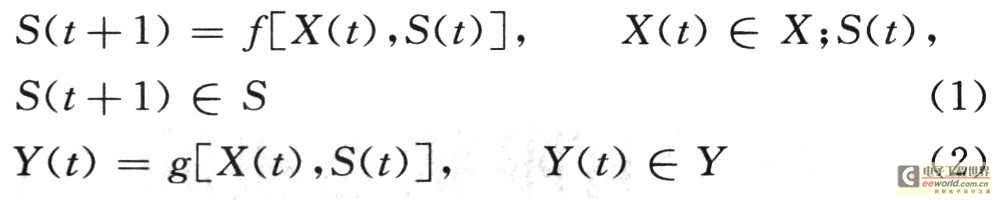

有限狀態(tài)機(jī)(Finite State Machine,F(xiàn)SM)可以用下面包含5種元素的集合來表示{X,,Y,,S,f,,g},這里S={S1,,S2,,…,,Sk}是FSM中狀態(tài)的集合;X={X1,,X2,,…,Xn}是FSM中輸入的集合,;Y={Y1,,Y2,…,,Ym)是FSM中輸出的集合,;f為狀態(tài)轉(zhuǎn)移函數(shù),表示由輸入信號(hào)變量X和當(dāng)前狀態(tài)S決定下一個(gè)狀態(tài),,即:XY;→S,;g為輸出函數(shù),表示由輸入信號(hào)變量X和狀態(tài)S決定狀態(tài)機(jī)的輸出變量Y,,即:XS→Y,。從上面定義可以看出,有限狀態(tài)機(jī)包含5類基本要素:即狀態(tài),、輸入,、輸出、轉(zhuǎn)移函數(shù)及輸出函數(shù),。它們分別用矢量函數(shù)表示如下:

不用的分類規(guī)則,,狀態(tài)機(jī)分類也不同。在實(shí)際的應(yīng)用中,,根據(jù)有限狀態(tài)機(jī)是否使用輸入信號(hào),,設(shè)計(jì)人員經(jīng)常將其劃分為Moore有限狀態(tài)機(jī)和Mealy型有限狀態(tài)機(jī)兩種類型。Moore型狀態(tài)機(jī)的輸出只與當(dāng)前的狀態(tài)有關(guān)而與輸入無關(guān),,而Mealy型狀態(tài)機(jī)的輸出不僅與當(dāng)前狀態(tài)有關(guān),,還與當(dāng)前的輸入有關(guān),它們共同決定Mealy狀態(tài)機(jī)的輸出,。圖2和圖3分別表示了Moore,,Mealy狀態(tài)機(jī)的結(jié)構(gòu)圖。

有限狀態(tài)機(jī)還有很多分類方法,,比如根據(jù)復(fù)位信號(hào)的不同可以分為同步復(fù)位狀態(tài)機(jī)和異步復(fù)位狀態(tài)機(jī),。根據(jù)輸出是否寄存分為直接輸出、寄存輸出,、根據(jù)狀態(tài)編碼輸出等類型,。

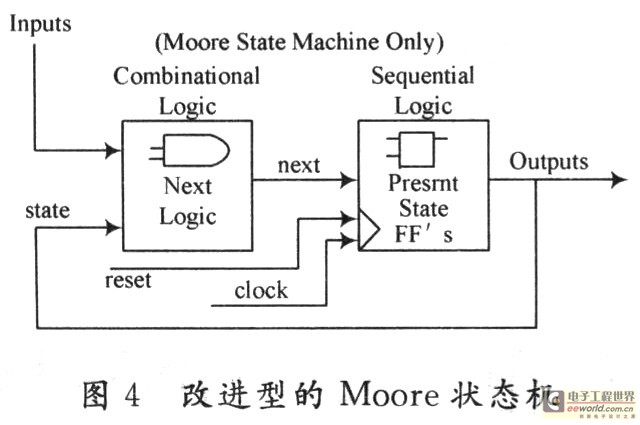

對(duì)于Moore型有限狀態(tài)機(jī),輸出信號(hào)將在時(shí)鐘信號(hào)的觸發(fā)沿到的幾個(gè)門時(shí)延后得到輸出值,,同時(shí)在該時(shí)鐘周期" title="時(shí)鐘周期">時(shí)鐘周期的剩余時(shí)間內(nèi)保持不變,,即使輸入信號(hào)在該時(shí)鐘周期內(nèi)發(fā)生變化,,輸出信號(hào)的值也不會(huì)改變。由于Moore型有限狀態(tài)機(jī)的輸出與當(dāng)前的輸入部分無關(guān),,因此當(dāng)前輸入產(chǎn)生的任何效果將會(huì)延遲到下一個(gè)時(shí)鐘周期,。可見,,Moore型狀態(tài)機(jī)的最大優(yōu)點(diǎn)就是可以將輸入部分與輸出部分隔離開,。

對(duì)于Mealy型有限狀態(tài)機(jī),由于它的輸出是輸入信號(hào)的函數(shù),,因此如果輸入信號(hào)發(fā)生變化,,則輸出可以在1個(gè)時(shí)鐘周期的中間發(fā)生改變。與Moore型有限狀態(tài)機(jī)相比,,它對(duì)輸入信號(hào)的變化相應(yīng)要早1個(gè)時(shí)鐘周期,。但它也會(huì)將輸入端口的噪聲傳遞給輸出信號(hào)。

綜合以上幾點(diǎn)的考慮,,該設(shè)計(jì)采用Moore型有限狀態(tài)機(jī)實(shí)現(xiàn)飛行器自毀系統(tǒng)的時(shí)序控制,。

2.2 毛刺和信號(hào)時(shí)延處理

Moore型有限狀態(tài)由于有組合邏輯進(jìn)程的存在,狀態(tài)機(jī)輸出信號(hào)會(huì)出現(xiàn)毛刺(競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象),;另一方面,,如果狀態(tài)信號(hào)是多位值的,則在電路中對(duì)應(yīng)了多條信號(hào)線,。由于存在傳輸延遲,,各信號(hào)線上的值發(fā)生改變的時(shí)間則存在先后,從而使得狀態(tài)遷移時(shí)在初始狀態(tài)和目的狀態(tài)之間出現(xiàn)臨時(shí)狀態(tài),,因此出現(xiàn)毛刺,。

參考各方面文獻(xiàn),現(xiàn)在消除輸出信號(hào)的“毛刺”一般可采用3種方案:一是調(diào)整狀態(tài)編碼,,使相鄰狀態(tài)間只有1位信號(hào)改變,,從而消除競(jìng)爭(zhēng)冒險(xiǎn)的發(fā)生條件,避免了毛刺的產(chǎn)生,。這種方案適用于順序遷移的狀態(tài)機(jī),;二是在有限狀態(tài)機(jī)的基礎(chǔ)上采用時(shí)鐘同步信號(hào),即把時(shí)鐘信號(hào)引入組合進(jìn)程,。狀態(tài)機(jī)每一個(gè)輸出信號(hào)都經(jīng)過附加的輸出寄存器,,并由時(shí)鐘信號(hào)同步,因而保證了輸出信號(hào)沒有毛刺,。這種方法存在一些弊端,;由于增加了輸出寄存器,硬件開銷增大,,這對(duì)于一些寄存器資源較少的芯片是不利的,;從狀態(tài)機(jī)的狀態(tài)位到達(dá)輸出需要經(jīng)過兩級(jí)組合邏輯,,這就限制了系統(tǒng)時(shí)鐘的最高工作頻率;由于時(shí)鐘信號(hào)將輸出加載到附加的寄存器上,,所以在輸出端得到信號(hào)值的時(shí)間比狀態(tài)的變化延時(shí)1個(gè)時(shí)鐘周期;三是直接把狀態(tài)機(jī)的狀態(tài)碼作為輸出信號(hào),,即采用狀態(tài)碼直接輸出型狀態(tài)機(jī),,使?fàn)顟B(tài)和輸出信號(hào)一致,使得輸出譯碼電路被優(yōu)化掉了,,因此不會(huì)出現(xiàn)競(jìng)爭(zhēng)冒險(xiǎn),。這種方案,占用芯片資源少,,信號(hào)與狀態(tài)變化同步,,因此速度快。

因此該設(shè)計(jì)采用狀態(tài)作為輸出信號(hào)且?guī)в袕?fù)位信號(hào)的Moore型有限狀態(tài)機(jī),。其結(jié)構(gòu)框圖如圖4所示,。

3 QuartusⅡ環(huán)境下有限狀態(tài)機(jī)的設(shè)計(jì)

3.1 系統(tǒng)總體結(jié)構(gòu)

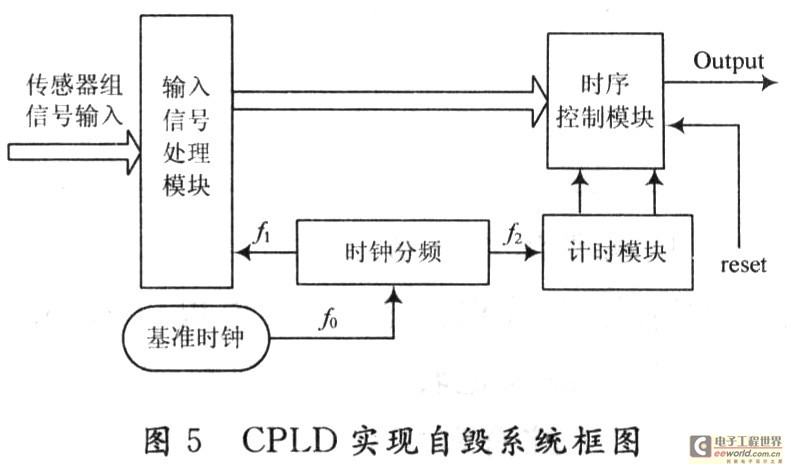

飛行器自毀系統(tǒng)在飛行器起飛后開始工作,并實(shí)時(shí)監(jiān)控飛行參數(shù)傳感器組及計(jì)時(shí)模塊產(chǎn)生的控制信號(hào),。圖5給出了自毀控制電路的硬件實(shí)現(xiàn)方案,。在CPLD中實(shí)現(xiàn)系統(tǒng)的總體結(jié)構(gòu)如圖5所示。CPLD外圍的高性能運(yùn)算放大器為主要元件的模擬電路以及傳感器組用來產(chǎn)生時(shí)序控制信號(hào)(c1,,c2,,c3,c4,,c5),,并輸入到輸入信號(hào)處理模塊。時(shí)鐘分頻用來產(chǎn)生各個(gè)模塊工作所需的時(shí)鐘,。計(jì)時(shí)模塊用來產(chǎn)生飛行總時(shí)間(tmax),。時(shí)序控制模塊用來產(chǎn)生自毀輸出信號(hào)(Output),它是整個(gè)系統(tǒng)的控制核心,,它的可靠性和穩(wěn)定性是飛行器能否實(shí)現(xiàn)可靠自毀的基礎(chǔ),。這里采用狀態(tài)作為輸出信號(hào)且?guī)в袕?fù)位信號(hào)的Moore型有限狀態(tài)機(jī)設(shè)計(jì)時(shí)序控制模塊實(shí)現(xiàn)飛行器可靠自毀。

3.2 改進(jìn)型有限狀態(tài)機(jī)實(shí)現(xiàn)時(shí)序控制

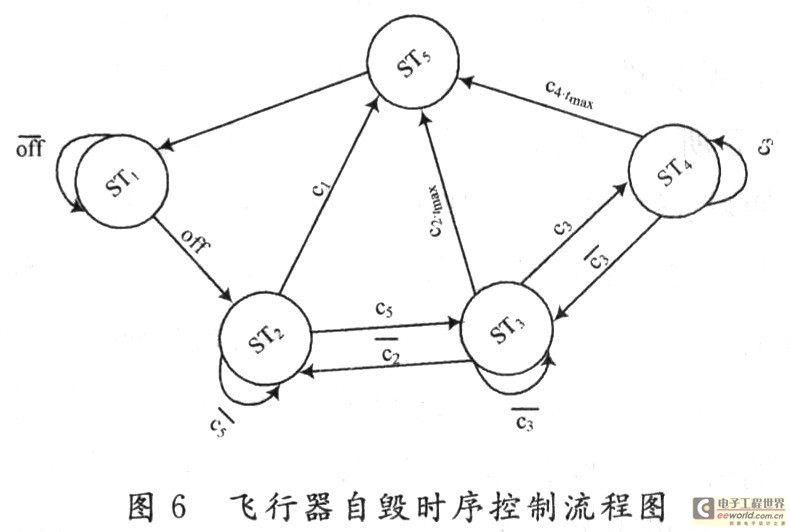

飛行器自毀時(shí)序控制流程圖如圖6所示,。飛行器自毀系統(tǒng)的時(shí)序狀態(tài)變化由各個(gè)傳感器的輸入及CPLD計(jì)時(shí)器狀態(tài)決定,。飛行參數(shù)傳感器組輸入不同的狀態(tài)指令,時(shí)序控制系統(tǒng)就可以在不同的狀態(tài)間變化,,其中ST5狀態(tài)是整個(gè)自毀系統(tǒng)的控制輸出,。根據(jù)圖6可以得到5個(gè)狀態(tài)觸發(fā)器的激勵(lì)方程:

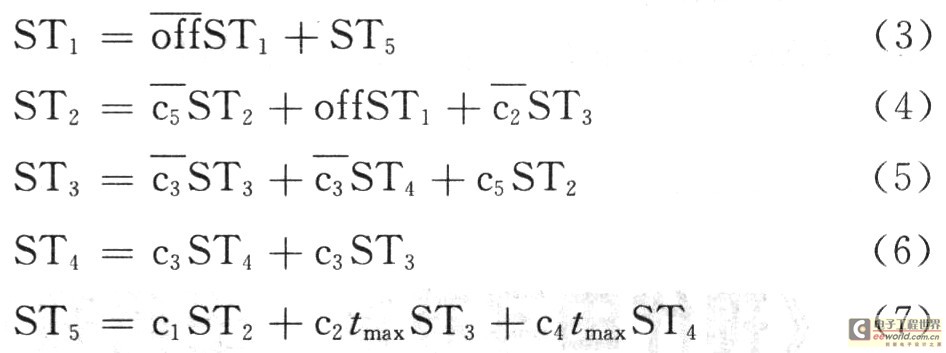

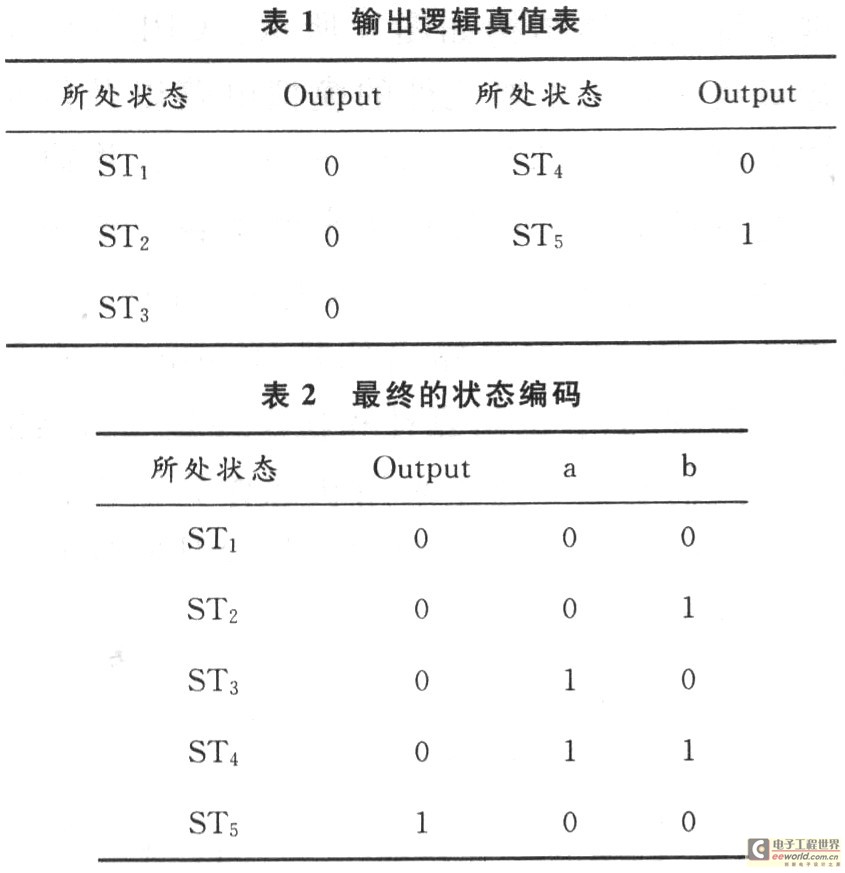

采用VHDL語言描述這種改進(jìn)的Moore型有限狀態(tài)機(jī)之前,首先要對(duì)Moore型有限狀態(tài)機(jī)的狀態(tài)進(jìn)行編碼操作,。如表1所示,,由于有限狀態(tài)機(jī)的輸出只有Output,,為了在綜合時(shí)更好地識(shí)別這5個(gè)不同的狀態(tài),需要添加狀態(tài)位,。在表2中添加兩個(gè)冗余的狀態(tài)位a,,b來區(qū)分STl,ST2,,ST3,,ST4。

3.3 VHDL編程注意事項(xiàng)

本設(shè)計(jì)采用單進(jìn)程描述方式,,也可以采用兩進(jìn)程描述,。用兩進(jìn)程時(shí)最好把轉(zhuǎn)移條件判斷邏輯和輸出邏輯分開,這樣有利于綜合器優(yōu)化代碼,,利于用戶添加合適的時(shí)序約束,,利于布局布線。狀態(tài)機(jī)要有默認(rèn)狀態(tài),,這是從狀態(tài)機(jī)的安全性方面考慮的,。在狀態(tài)機(jī)的設(shè)計(jì)中,一般要包含一個(gè)初始狀態(tài),,當(dāng)芯片上電復(fù)位時(shí),,狀態(tài)機(jī)能夠進(jìn)入到初始狀態(tài)。這需要在狀態(tài)機(jī)設(shè)計(jì)中加入復(fù)位信號(hào),。

4 電路仿真

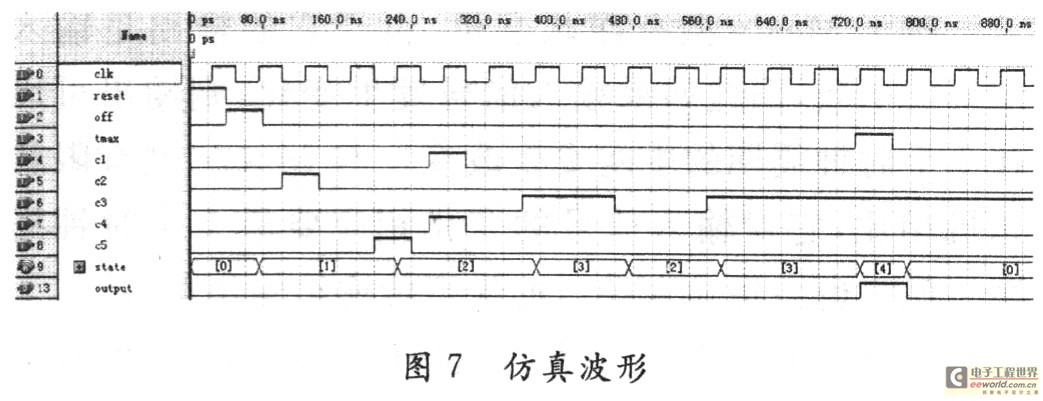

在QuartusⅡ環(huán)境下,,將VHDL文本程序保存為工程,工程文件經(jīng)編譯后即可進(jìn)行電路仿真,。仿真波形如圖7所示,,從波形結(jié)果可以看出,復(fù)位信號(hào)(reset)有效,,使?fàn)顟B(tài)機(jī)恢復(fù)到初始狀態(tài),,飛行器起飛(off)有效開始,時(shí)序控制系統(tǒng)經(jīng)歷了飛行過程中5個(gè)不同的狀態(tài),,如圖7中state變量所示,。并最終輸出自毀指令(Output),VHDL程序設(shè)計(jì)符合要求,。整個(gè)時(shí)序控制可靠,,消除了毛刺現(xiàn)象。在QuartusⅡ環(huán)境下,,只需要1根下載編程電纜,,通過PC機(jī)的并行口連接到目標(biāo)板的JTAG口,將下載信息下載到目標(biāo)器件中。

5 結(jié) 語

仿真及實(shí)驗(yàn)結(jié)果證明,,采用上述的有限狀態(tài)機(jī)思想進(jìn)行飛行器自毀系統(tǒng)時(shí)序控制設(shè)計(jì),,不但可以減小占用CPLD資源,降低成本,,方便測(cè)試,,并且可以有很好的系統(tǒng)性能?;谟邢逘顟B(tài)機(jī)的飛行器自毀系統(tǒng)定時(shí)精度達(dá)到納秒級(jí),,可以有效可靠地控制自毀信號(hào)輸出,有效消除毛刺現(xiàn)象,,提高了飛行器自毀系統(tǒng)的穩(wěn)定性、可靠性,。