美國模擬器件公司生產(chǎn)的固定頻率電流模式DC/DC步降變換器控制器ADP1864與凌特公司的LTC1772和LTC3801引腳兼容。ADP1864輸入電壓" title="輸入電壓">輸入電壓Vin范圍為3.15~14V,輸出電壓" title="輸出電壓">輸出電壓Vo為O.8V~Vin,輸出電流可達5Ao ADP1864驅(qū)動一個P溝道MOSFET,效率可達92%。ADP1864的應用領(lǐng)域主要包括無線裝置、1~3節(jié)鋰離子電池供電的設備、機頂盒、處理器內(nèi)核電源和硬盤驅(qū)動器等。

封裝、引腳功能及工作原理

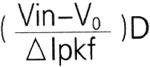

ADP1864采用6引腳TSOT封裝,引腳排列如圖1所示。

|

ADP1864的各引腳功能見表1 。

|

ADP1864內(nèi)部振蕩器(OSC)頻率為580kHz。在每個振蕩周期開始時,IC引腳6上的輸出驅(qū)動Q1導通,L1中產(chǎn)生電流并且增加。當電流感測放大器電壓等于在引腳COMP上的電壓

時,內(nèi)部觸發(fā)器復位,PGATE腳上的電壓變?yōu)楦唠娖剑琎1截止,電感電流減小,直到下一個振蕩周期開始為止。

應用電路

輸出電壓Vo在分壓器電阻R2上的感測信號經(jīng)IC的FB引腳輸入到內(nèi)部誤差放大器的負輸入端。誤差放大器正輸入端連接0.8V的參考電壓VREF,誤差放大器輸出電壓即是引腳COMP上的電壓。

ADP1864提供軟啟動功能,可以限制輸入浪涌電流、電感電流增加速率和輸出電壓過沖。ADP1864在負載短路時,引腳FB上的電壓將迅速降低。當VFB

對于圖2所示的電路,設Vin=3.3V,Vo=2.5V,Io=2A,主要元件的選擇如下:

1、R1/R2值的確定 ADP1864引腳FB上的門限電壓VFB=VREF=0.8V,于是VFB=Vo(R2/(R1+R2))。因此 R1=R2× 圖片4 ,若選取R2=80.6kΩ,則R1=170.4kΩ 。2、電感器L1電感值的選擇 L1電感值L可按照L=

,若選取R2=80.6kΩ,則R1=170.4kΩ 。2、電感器L1電感值的選擇 L1電感值L可按照L= 計算,式中Alpk為電感器峰-峰值紋波電流,可選取其為輸出電流的30%,△Ipk=0.31o=2A×0.3=0.6A;f為開關(guān)頻率,f=580kHz;D為占空因數(shù),D=(Vo+VD)/(Vin+VD),VD為D1正向壓降,Vo=0.5V。因此,D=(2.5V+0.5V)/(3.3V+0.5V)=0.79。根據(jù)式得

計算,式中Alpk為電感器峰-峰值紋波電流,可選取其為輸出電流的30%,△Ipk=0.31o=2A×0.3=0.6A;f為開關(guān)頻率,f=580kHz;D為占空因數(shù),D=(Vo+VD)/(Vin+VD),VD為D1正向壓降,Vo=0.5V。因此,D=(2.5V+0.5V)/(3.3V+0.5V)=0.79。根據(jù)式得 ![]() 。

。

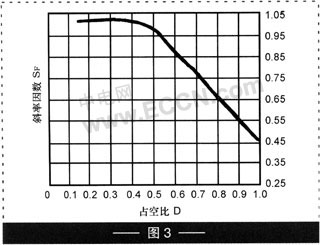

3、電流傳感電阻RCS值的確定 電流感測電阻Rcs上的峰值電流感測電壓Vcs(PK)=O.125V,Vcs值可根據(jù) ![]() 。式中,SF為斜率因數(shù),它與占空比D之間的關(guān)系如圖3所示。由于D=0.79,從圖3可知,SF=0.65。則

。式中,SF為斜率因數(shù),它與占空比D之間的關(guān)系如圖3所示。由于D=0.79,從圖3可知,SF=0.65。則![]() 。

。

、功率MOSFET的選擇 由于輸入電壓最小值僅為3.15V,Q1的柵極啟動門限電壓(Vt)至少為1V。Q1的額定電流(有效值)ID(rms)可由式 ![]() 估算,由于占空比D=0.79,Io=2A,因此

估算,由于占空比D=0.79,Io=2A,因此![]()

為降低Q1的功率耗散,其導通態(tài)電阻RCS(on)應遠低于100mΩ。

5、肖特基二極管D1的選擇 D1的正向壓降Vd不應大于O.5V,平均電流1D(AV)可按式ID(AV)=(1-D)1o=(1-0.79)×2A=0.42A。

6、輸入電容Cin和輸出電容Co的選擇 Cin典型值為10 μ F,為使其有較小的等效串聯(lián)電阻(ESR),宜選用陶瓷電容器。

Co選擇日本三洋公司的47 μ F低ESR的陶瓷電容器。對于ADP1864引腳COMP上的RC串聯(lián)補償網(wǎng)絡,推薦R3=15kΩ,C1=470pF。

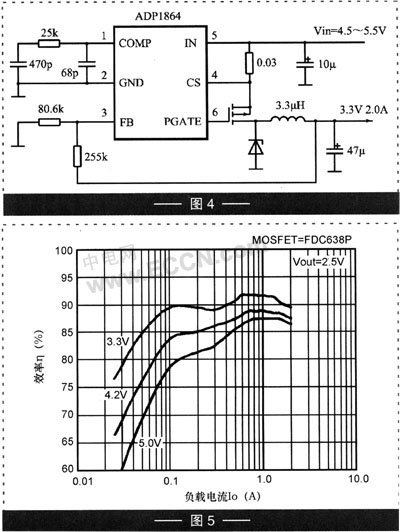

輸入電壓Vin=4.5~5.5V、輸出為3.3V/2A的應用電路及元件選擇如圖4所示。

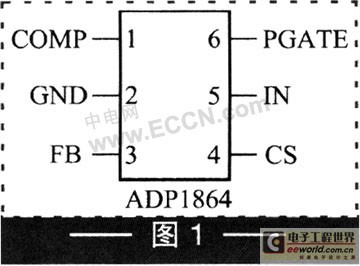

圖5所示為電路效率與負載電流之間的關(guān)系曲線。由該曲線可知,當輸入電壓Vin為3.3V、輸出為2.5V/2A時,效率超過88%。