六自由度" title="自由度">自由度電磁" title="電磁">電磁跟蹤" title="跟蹤">跟蹤系統(tǒng)根據(jù)電磁感應(yīng)的原理來計算出目標的六個自由度參數(shù),從而唯一確定目標的位 置和姿態(tài)。怎樣由接收到的模擬信號計算得到目標的位置和姿態(tài)參數(shù)是影響整個系統(tǒng)性能的關(guān)鍵所在。在 一些早期的產(chǎn)品中對感應(yīng)天線接收信號的處理主要采用模擬電路和單片機來完成,由于模擬電路精度低,受 器件性能影響大,單片機的指令執(zhí)行速度慢,使整個系統(tǒng)無法準確實時地確定目標的位置。本文提出的DSP" title="DSP">DSP 數(shù)據(jù)采集系統(tǒng)利用了DSP快速的指令執(zhí)行周期和強大的數(shù)字信號處理功能和CPLD靈活的時序和邏輯控 制功能,快速準確地完成了對每一路接收信號的采集和計算,得到了準確的數(shù)字接收矩陣,為進一步計算目 標的六個自由度參數(shù)打下良好基礎(chǔ)。本文主要介紹了DSP數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計方案和軟件設(shè)計流程。

1 電磁跟蹤系統(tǒng)的工作原理

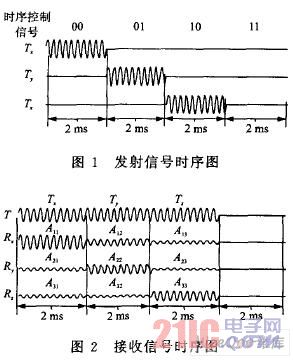

六自由度電磁跟蹤系統(tǒng)的發(fā)射和接收天線均為三維正交環(huán)形天線。發(fā)射電路向發(fā)射天線的xyz軸按時

式中x為發(fā)射矩陣,為一單位對角陣,G為系統(tǒng)總增益,H、M為包含了接收天線相對于發(fā)射天線的位置和接收天線姿態(tài)角度的坐標變換矩陣。因此接收矩陣是影響目標參數(shù)精度的關(guān)鍵。

2 DSP系統(tǒng)的硬件設(shè)計

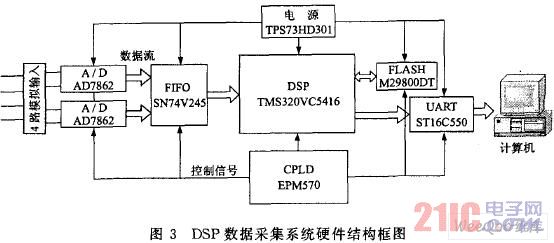

由六自由度電磁跟蹤系統(tǒng)的原理,為了得到系統(tǒng)接收矩陣Y,DSP系統(tǒng)要同時采集四路模擬信號:T,Rx ,R y,Rz ,而每一路的信號都是時分復用的。因此要求系統(tǒng)能準確區(qū)分每一路每個時間段的數(shù)據(jù),然后計算出每一段數(shù)據(jù)的幅度,將其發(fā)送到計算機。DSP數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)如圖3所示。

四路模擬信號由兩片A/D同時進行采樣,采樣得到的數(shù)字比特流通過FIFO緩存后有序地傳送到DSP芯片,DSP快速地對采集來的數(shù)字信號進行計算,最后將計算結(jié)果通過異步串行接口傳送到計算機。各器件之間的時序配合由CPLD來控制。

2.1 DSP外圍電路及通信接口的設(shè)計

本系統(tǒng)所采用的TMS320VC5416是TI公司推出的一款低功耗高性能16位定點DSP,具有160 MIPS 的指令執(zhí)行速度,片內(nèi)集成有128 K×16 bit的RAM 和16 K×16 bit的ROM。它的外圍電路主要包括時 鐘,電源,復位以及外程序存儲器。本系統(tǒng)采用外部時鐘,電源和復位采用TI公司的專用芯片TPS73HD301。

由于TM320VC5416無片內(nèi)FLASH,因此系統(tǒng)采用M29w8O0DT作為程序存儲器,系統(tǒng)上電后,DSP內(nèi)部 引導程序把M29W800DT 中的工作程序加載到片內(nèi)SRAM ,提高程序執(zhí)行效率。 系統(tǒng)通信電路包括并行通信和串行通信兩部分。

由于TMS320VC5416片內(nèi)沒有UART端口,要實現(xiàn) 和計算機的串行數(shù)據(jù)通信,系統(tǒng)采用了ST16C550,通過IO訪問ST16C550來實現(xiàn)與主機的串行通信。 系統(tǒng)中FI ASH,F(xiàn)1FO,ST16C550通過CPI D分別映射到DSP的數(shù)據(jù)空間和IO空間,DSP與他們的 通信主要通過16位的外部并行數(shù)據(jù)總線。因此用到的DSP的外部接口主要有16位地址總線,16位數(shù)據(jù)總線和一組用于訪問片外存儲器與I/0端口的控制信號。

2.2 A/D與DSP的接口設(shè)計

AD7862是AD公司推出的高速、低功耗、雙極性12位的A/D轉(zhuǎn)換芯片,其中包含了兩個獨立的快速 ADC模塊(允許同時采樣和轉(zhuǎn)換兩路信號),4路模擬輸入信號,2.5 V的內(nèi)部電壓基準以及12位的高速并 行接口,最高采樣率達250 kHz。

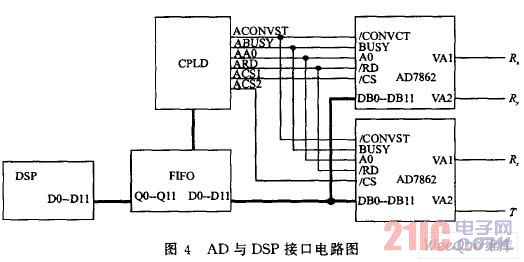

系統(tǒng)要求對4路頻率為16 kHz 的模擬信號進行同時采樣,采樣時不 能有相位差。AD7862雖然有4路模 擬輸入通道,然而內(nèi)部只有兩個 ADC,即每片A/D只能同時采樣兩 路模擬信號,因此系統(tǒng)中采用了兩 片AD7862來完成對模擬信號的采 樣[3]。A/D與DSP接口如圖4所 示。

從這部分電路可以看到,DSP 不直接與數(shù)/模轉(zhuǎn)換模塊接口,而是利用CPLD屏蔽A/D轉(zhuǎn)換的初始化以及讀寫操作過程,并將兩個A/D 轉(zhuǎn)換單元通過FIFO緩存后映射到DSP的10空間。這樣DSP可以在未知ADC控制方式的情況下,通過定 時訪問外設(shè)的方式來獲得4個通道的模數(shù)轉(zhuǎn)換后的數(shù)據(jù)。這種方法大大提高了DSP的工作效率,而且當系 統(tǒng)要求增加ADC的數(shù)目時,不需要改變電路,極大的提高了系統(tǒng)的可擴展性。

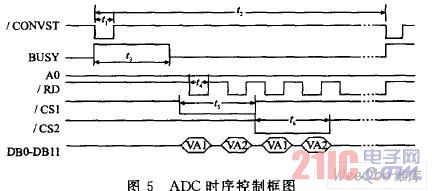

電路中兩片A/D除了片選控制信號以外其 他的數(shù)據(jù)總線以及控制總線全部是分別連在一起 的。將片選控制與其他控制分開的原因在于:A/ D芯片的初始化以及轉(zhuǎn)換過程需要同時完成,但 是數(shù)據(jù)的輸出需要分別完成,否則會出現(xiàn)總線沖 突。ADC時序控制框圖如圖5所示。

AD7862最高采樣率可到250 kHz,然而根據(jù) 正弦信號抽樣的基本原則,抽樣率應(yīng)為原信號的 整數(shù)倍,又考慮到對抽樣后的數(shù)據(jù)做DFT運算時 希望數(shù)據(jù)點數(shù)N 最好為2的整次冪,因此設(shè)計系 統(tǒng)實際采樣率為128 kHz。

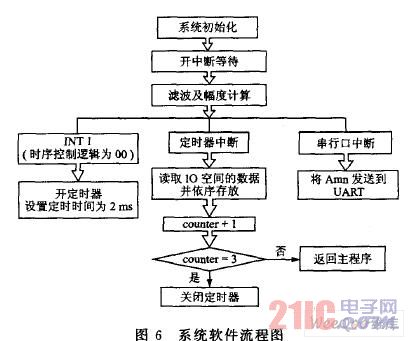

3 系統(tǒng)的軟件設(shè)計

TMS32O5416的軟件設(shè)計主要包括初始化程 序,主程序,外部中斷程序,定時器中斷程序和串 行口中斷程序。初始化程序完成DSP及外圍芯片 的初始化,主程序?qū)⒉杉降臄?shù)據(jù)濾波后進行 FFT運算提取幅度值。串行口中斷程序完成接收 矩陣的發(fā)送。系統(tǒng)軟件的工作流程如圖6所示,當模擬信號進來并開始采樣時,即發(fā)射部分的時序控制邏輯為OO時,產(chǎn)生INT1,DSP開啟定時器中斷并設(shè)置定 時器的值為2 ms。定時器中斷后,DSP從FIFO 中讀取前2 ms時間段內(nèi)采集到的所有數(shù)據(jù),