【摘 要】 通過設(shè)計實例詳細(xì)介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發(fā)FPGA/CPLD的方法,,以及與電路圖輸入和其它HDL語言相比,,使用VHDL語言的優(yōu)越性,。

關(guān)鍵詞:VHDL,,F(xiàn)PGA/CPLD,EDA

1 引 言

EDA(電子設(shè)計自動化)關(guān)鍵技術(shù)之一是采用硬件描述語言(HDL)描述電路系統(tǒng),,包括電路結(jié)構(gòu),、行為方式、邏輯功能以及接口,。就FPGA和CPLD(分別是現(xiàn)場可編程門陣列和復(fù)雜可編程邏輯器件的簡稱)開發(fā)來說,,比較流行的HDL主要有VHDL、ABEL-HDL,、AHDL等,,其中,VHDL對系統(tǒng)的行為描述能力最強,,已被IEEE確定為標(biāo)準(zhǔn)HDL,,并得到目前所有流行EDA軟件的支持,,進而成為系統(tǒng)設(shè)計領(lǐng)域最佳的硬件描述語言。用VHDL設(shè)計電路系統(tǒng),,可以把任何復(fù)雜的電路系統(tǒng)視為一個模塊,,對應(yīng)一個設(shè)計實體。在VHDL層次化設(shè)計中,,它所設(shè)計的模塊既可以是頂層實體,,又可以是較低層實體,但對不同層次模塊應(yīng)選擇不同的描述方法(如行為描述或結(jié)構(gòu)描述),。本文在設(shè)計實例中詳細(xì)介紹了用VHDL語言開發(fā)FPGA/CPLD的方法,,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優(yōu)越性,。

2 設(shè)計實例

一個復(fù)雜電路系統(tǒng)的設(shè)計都是采用自頂向下將系統(tǒng)按功能逐層分割的層次化設(shè)計方法,。在頂層設(shè)計中,要對內(nèi)部各功能塊的連接關(guān)系和對外的接口關(guān)系進行描述,,而功能塊實際的邏輯功能和具體的實現(xiàn)形式則由下一層模塊來描述,。在系統(tǒng)的底層設(shè)

計中,如采用VHDL進行描述,,由于其對系統(tǒng)很強的行為描述能力,,可以不必使系統(tǒng)層層細(xì)化,從而避開具體的器件結(jié)構(gòu),,從邏輯行為上直接對模塊進行描述和設(shè)計,,之后,EDA軟件中的VHDL綜合器將自動將程序綜合成為具體FPGA/CPLD等目標(biāo)芯片的網(wǎng)表文件,,無疑可使設(shè)計大為簡化,。下面以數(shù)字鐘的設(shè)計為例予以說明。

數(shù)字鐘的功能主要有:

·能夠?qū)γ?、分,、小時進行計時(按每日24小時計時制)。

·秒,、分,、小時位能夠調(diào)整。

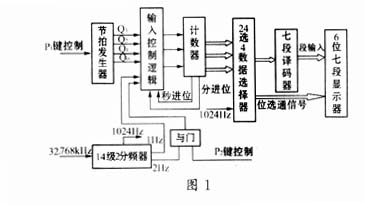

根據(jù)數(shù)字鐘的功能要求,,可將數(shù)字鐘分為四個功能塊:秒脈沖發(fā)生器,、計數(shù)器、校時器和顯示電路,。而這些功能塊又可進一步分割為更小的模塊,,如計數(shù)器模塊可再分為秒、分,、小時計數(shù)器,。其它功能塊的細(xì)化過程不再詳述,,數(shù)字鐘的系統(tǒng)框圖如圖1所示。圖中,,P1鍵為自動計時,、校時、校分和校秒四種工作狀態(tài)選擇鍵,,P2鍵為系統(tǒng)處于校時狀態(tài)時對時,、分、秒進行校準(zhǔn)的校時鍵,,32.768kHz為作為脈沖源的晶振頻率,,經(jīng)14級2分頻器分頻在其最高位、次高位以及第五位輸出端分別可獲得1Hz,、2Hz和1024Hz的脈沖信號,,這三個脈沖信號分別用作計時脈沖,、校時脈沖和顯示電路的掃描時鐘,。下面用VHDL語言設(shè)計底層的小時計數(shù)器。小時計數(shù)器為一個24進制BCD碼計數(shù)器,,其模塊示意圖如圖2所示,。reset、clk分別為異步清零端和時鐘端,,qb和qa分別為十位和個位的四位BCD碼輸出端,。該模塊計數(shù)方式的實現(xiàn)比較復(fù)雜,當(dāng)十位數(shù)為0或1時,,個位進行10進制計數(shù),,當(dāng)十位數(shù)為2時,個位進行4進制計數(shù),。如用電路圖描述,,則必須選擇和調(diào)用若干門、觸發(fā)器或宏單元,,并需對所調(diào)用的器件進行合適的控制,。而若采用VHDL語言對其功能進行描述,問題則顯得非常簡單,。

END counr24—arc,;

上述程序中由語句ENTITY與ENDcount24包含的部分稱為程序的實體,它的電路意義就相當(dāng)于器件的外部接口,,在電路圖上相當(dāng)于一個元件符號,。該實體是一個完整、獨立的語言模塊,,它描述了coun t24的接口信息,,定義了count24的端口引腳clk,、reset、qa,、qb的輸入,、輸出性質(zhì)及其數(shù)據(jù)類型;由語句ARCHITECTURE開始,,到END count24arc結(jié)束為結(jié)構(gòu)體層次,,結(jié)構(gòu)體層次用于描述count24內(nèi)部的邏輯功能,在電路上相當(dāng)于器件的內(nèi)部電路結(jié)構(gòu),。描述邏輯功能的具體做法是,,在結(jié)構(gòu)體的進程區(qū)內(nèi),通過定義兩個整型中間變量cntb,、cnta分別表示十位和個位,,之后用IF語句說明當(dāng)時鐘到來時,這兩個變量的計數(shù)和進位情況,,當(dāng)進程結(jié)束后,,再將這兩個中間變量分別賦給輸出變量qb和qa。整個程序不長,,邏輯描述十分簡潔,、明了。

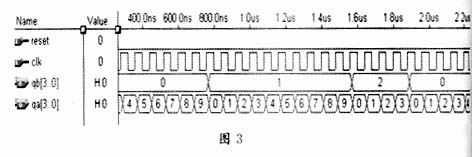

上述程序輸入完成后,,首先要經(jīng)EDA軟件進行編譯,,本設(shè)計采用的是美國Altera公司的MAX+PLUS2II軟件,經(jīng)該軟件中的Compiler編譯器編譯后,,若有任何信息,、錯誤和警告,都將在VHDL編譯器窗口上提示,,設(shè)計者可根據(jù)提示對設(shè)計進行修改,。當(dāng)編譯通過時,建網(wǎng)表,、邏輯綜合,、適配、劃分,、時域分析,、裝配等均已自動完成,并生成多個后續(xù)工作要用的文件,。編譯的成功表明已為所設(shè)計的項目建立了一個編程文件,,但還不能保證該設(shè)計在各種可能的情況下都有正確的響應(yīng),因而編譯通過后,還必須用MAX+PLUSII的Simulator仿真器和Timing Analyzer工具分別進行功能仿真和時序仿真,,以驗證設(shè)計是否完全符合要求,,若發(fā)現(xiàn)有問題,則必須返回原設(shè)計進行修改,。上述模塊經(jīng)功能仿真和時序仿真都沒有發(fā)現(xiàn)任何問題,。圖3所示即為上述模塊的仿真波形。該模塊設(shè)計完成后存檔,,待建立頂層文件時調(diào)用,。

接下來再用VHDL語言對底層中其它所有模塊一一進行設(shè)計,這包括:秒,、分計數(shù)器(均為60進制計數(shù)器),、14級2分頻器、24選4數(shù)據(jù)選擇器,、BCD七段譯碼器,、節(jié)拍發(fā)生器等。所有程序均經(jīng)MAX+PLUS2II軟件的編譯和仿真,。當(dāng)模塊設(shè)計完成后均要存檔,,待建立頂層文件時調(diào)用。

除底層模塊外,,其它各層次模塊(包括頂層)也都適于用VHDL語言描述,。只是應(yīng)選擇不同的描述方法而已。當(dāng)?shù)讓又兴心K均設(shè)計完成后,,采用VHDL語言中的結(jié)構(gòu)描述法,用元件調(diào)用語句調(diào)用底層各模塊并進行連接,,即可建立數(shù)字鐘的頂層文件,。數(shù)字鐘的頂層文件也必須經(jīng)過EDA軟件的編譯和仿真,在此過程中,,如有需要,,還可隨時打開查看并修改任一層次的設(shè)計。當(dāng)最后確認(rèn)設(shè)計完全符合設(shè)計要求時,,再將編譯后的頂層文件下載到目標(biāo)芯片PFGA/CPLD中,。

綜上所述,整個系統(tǒng)各層次模塊均采用VHDL語言描述,,其優(yōu)點主要有下述三個方面∶(1)能進行系統(tǒng)級的行為描述,,從邏輯行為上對模塊進行描述和設(shè)計,大大降低了設(shè)計難度,。(2)描述的設(shè)計思想,、電路結(jié)構(gòu)和邏輯關(guān)系清晰明了,便于存檔,、查看,、維護和修改,。(3)支持大規(guī)模設(shè)計的分解和已有設(shè)計的再利用。

僅上述這三個優(yōu)點,,就是電路圖輸入和其它HDL語言所不能實現(xiàn)的,。

3 結(jié)束語

集成電路規(guī)模越是龐大,VHDL語言的優(yōu)越性就越顯突出,。目前,,數(shù)百萬門規(guī)模的FPGA/CPLD已進入實用,VHDL強大的系統(tǒng)描述能力,、規(guī)范的程序設(shè)計結(jié)構(gòu)和靈活的語句表達風(fēng)格使其必將擔(dān)負(fù)起大系統(tǒng)設(shè)計的幾乎全部設(shè)計任務(wù),。