本系統(tǒng)原設(shè)計為8通道QCM檢測,即采用8套完全相同的以 MAX913芯片為核心的振蕩器,通過2個CD4069反相器反相后分別送到4個差頻器74LS74的D端,每一個差頻器74LS74內(nèi)部有2個D觸發(fā)器。2個6M高精度有源晶振分別經(jīng)時鐘芯片CDCV304后變成8個6M輸出信號,分別送到4個差頻器74LS74的CLK端。經(jīng)過4個差頻器 74LS74差頻后的頻率信號送到可編程邏輯器件EPM570GT100C3芯片的I/O口。EPM570GT100C3在這里做頻率計,通過軟件編程來實(shí)現(xiàn)。記下的差頻頻率通過8位數(shù)據(jù)線送到51單片機(jī)AT89S52,同時AT89S52對EPM570GT100C3控制,以選擇哪個通道,AT89S52處理后的數(shù)據(jù)經(jīng)過232串口送到上位機(jī)。

QCM凝血傳感器屬于非質(zhì)量響應(yīng)型傳感器,利用石英晶體振蕩頻率變化對晶體所處體系密度和粘度變化的高度敏感性來檢測體系性狀的改變。QCM凝血傳感器通過紅細(xì)胞阻抗特性的變化引起傳感器的響應(yīng)來檢測紅細(xì)胞凝集時間和沉降速率。因此,利用基于QCM傳感器的生物芯片檢測技術(shù),研制了凝血分析儀。

石英晶體振蕩頻率對晶體表面質(zhì)量負(fù)載(質(zhì)量效應(yīng))和反應(yīng)體系物理性狀如密度、粘度、電導(dǎo)率等(非質(zhì)量效應(yīng))的改變高度敏感,具有亞ng級的質(zhì)量檢測能力,其靈敏度可達(dá)1ng/Hz。

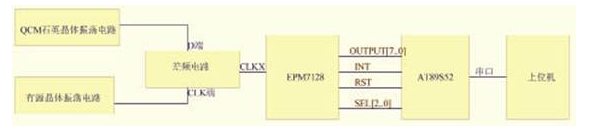

以一個通道為例來進(jìn)行基于QCM傳感器的生物芯片檢測電路的設(shè)計,由于一個通道所使用的邏輯門比較少,因此選擇可編程邏輯器件EPM7128LC84-10。圖1所示是系統(tǒng)總體設(shè)計框圖。

硬件設(shè)計

1、石英晶體振蕩及差頻電路

為了保證QCM在滴入生物試劑后能振蕩起來,必須采用一套比較特殊的自激振蕩器電路,普通的用反相器構(gòu)成的振蕩器電路不易起振,自激振蕩器通常是由基本放大電路、正反饋網(wǎng)絡(luò)和選頻網(wǎng)絡(luò)三部分組成的。在石英晶體振蕩電路中,石英晶體作為正反饋網(wǎng)絡(luò)的主要組成部分,也是一種選頻網(wǎng)絡(luò),只有在石英晶體振蕩器的固有諧振頻率下才能滿足條件。根據(jù)這一原理,采用以MAX913芯片為核心的振蕩器,它的輸出是TTL電平,便于單片機(jī)或可編程邏輯器件的信號采集。測量用QCM振蕩電路輸出的方波信號送入差頻器74LS74的D端,參考用高精度6M晶振輸出的方波信號送入差頻器74LS74的CLK端,得到的差頻信號送入可編程邏輯器件進(jìn)行計數(shù),采用差頻的目的是為了降低輸入到可編程邏輯器件EPM7128的頻率。石英晶體振蕩及差頻電路如圖2所示。

2、EPM7128和AT89S52的控制電路

經(jīng)過差頻器74LS74后的差頻信號,從74LS74的5腳輸出送到可編程邏輯器件EPM7128的6腳I/O口上。由于可編程邏輯器件引腳比較靈活,又有可擦除可編程的能力,因此對原設(shè)計進(jìn)行修改時,只需要修改原設(shè)計文件再對可編程邏輯器件芯片重新編程即可,而不需要修改電路布局,更不需要重新加工印刷線路板,這就大大提高了系統(tǒng)的靈活性,且具有很好的保密性,在這里通過軟件編程將其設(shè)計為頻率計。在開始測量時,上位機(jī)通過串口給51 單片機(jī)AT89S52發(fā)出命令,AT89S52先給EPM7128的22腳一個RST復(fù)位命令,使EPM7128復(fù)位后開始工作計頻,頻率測量計時時間為 100ms,計時結(jié)束后,EPM7128的46腳發(fā)出中斷信號送給AT89S52的外中斷0口(INT0),單片機(jī)接收到中斷信號后從P1口的 P10~P12給EPM7128發(fā)出3個選擇信號SEL0~SEL2。由于在EPM7128設(shè)計的是32位計數(shù)器,而51單片機(jī)是8位機(jī),因此需要4次分時處理32位數(shù)據(jù)信號,由選擇信號SEL0~SEL2來控制。最終從EPM7128輸出8位數(shù)據(jù)信號到AT89S52的P0數(shù)據(jù)口,經(jīng)單片機(jī)處理后通過串口發(fā)到上位機(jī)進(jìn)行最后的數(shù)據(jù)處理和圖形界面顯示。此部分硬件電路圖如圖3所示。

AT89S52的14、15腳外接晶振和電容組成單片機(jī)的振蕩電路,4腳是復(fù)位端,由IPM810控制,IPM810具備上電復(fù)位、手動復(fù)位及欠壓復(fù)位功能。AT89S52使用PLCC44腳封裝的貼片器件,利用單片機(jī)AT89S52的P1口和復(fù)位口進(jìn)行在線編程,使用at89isp軟件在線編程,進(jìn)行程序的燒寫。

EPM7128的83腳是全局時鐘,外接工作用的時鐘信號。該時鐘信號可以使用有源晶振來產(chǎn)生,也可以使用無源晶振加振蕩器產(chǎn)生。 EPM7128的14、71、23、62腳分別是TDI、TDO、TMS、TCK端,是JTAG編程口。EPM7128也是采用在線編程方式進(jìn)行程序的燒寫,采用JTAG在線編程。其他引腳基本上都是I/O口,可根據(jù)需要指定。本設(shè)計中可編程邏輯器件EPM7128和51單片機(jī)AT89S52共有13根線相連,進(jìn)行數(shù)據(jù)通訊和控制,其中OUTPUT0~OUTPUT7是數(shù)據(jù)通訊,SEL0~SEL2是AT89S52對EPM7128的片選控制信號,INT 則是EPM7128對AT89S52發(fā)出的中斷控制信號。

軟件設(shè)計

本系統(tǒng)中ALTERA公司可編程邏輯器件EPM7128的內(nèi)核程序采用Verilog HDL硬件描述語言編寫,使用MAX+plusII10.1編譯系統(tǒng)或Quartus II 4.2編譯系統(tǒng)編譯,設(shè)計實(shí)現(xiàn)了分頻、頻率計數(shù)、數(shù)據(jù)選擇等功能。51單片機(jī)AT89S52用C語言和匯編語言混合編程,使用Keil C51編譯系統(tǒng)編譯。

1、可編程邏輯器件EPM7128的頂層電路

頂層電路如圖4所示,由分頻模塊、計數(shù)模塊、數(shù)據(jù)選擇模塊組成,分頻模塊和計數(shù)模塊采用Verilog HDL硬件描述語言編寫,數(shù)據(jù)選擇模塊用圖形輸入方式。12M的振蕩信號送到EPM7128的CLK端,經(jīng)過分頻模塊后變成10Hz的頻率信號給計數(shù)模塊提供基準(zhǔn)時基。AT89S52給EPM7128的RST端提供復(fù)位RST信號,使EPM7128復(fù)位,開始記錄差頻器送到EPM7128的CLKX1端的頻率信號。記時時間到,EPM7128的輸出端INT發(fā)出中斷信號,通知單片機(jī)接收數(shù)據(jù)。由于計數(shù)模塊的計時器是32位的,因此通過3個8位的二選一數(shù)據(jù)選擇器,在單片機(jī)給出的SEL0~SEL2片選信號控制下,分時選擇從EPM7128的輸出端OUTPUT7~OUTPUT0輸出的8位數(shù)據(jù)信號到 AT89S52的P0數(shù)據(jù)口。

2、可編程邏輯器件EPM7128的分頻模塊

分頻模塊的目的是將可編程邏輯器件EPM7128的83腳輸入的12M頻率信號,分頻成10Hz頻率信號給計數(shù)模塊做基準(zhǔn)時鐘,即計時時間是100ms。

3、可編程邏輯器件EPM7128的計數(shù)模塊

由分頻模塊分頻后的10Hz信號送到計數(shù)模塊,它通過門控電路,加到可以控制開、閉時間的閘門上。被測脈沖加到計數(shù)模塊中閘門的輸入端,開始測頻時,先將計數(shù)器置0,待門控信號到來后,打開閘門,允許被測脈沖通過,計數(shù)器開始計數(shù),直到門控信號結(jié)束,閘門關(guān)閉,停止計數(shù)。因此,當(dāng)門控信號的周期為1s時,在閘門開通時間1s通過閘門的被測脈沖個數(shù)即為該被測信號的頻率,為了使上位機(jī)獲得更多的數(shù)據(jù)和精度,使門控信號的周期為0.1s。

以下是可編程邏輯器件EPM7128的計數(shù)模塊的程序部分代碼:

always @ (posedge CLK_1hz or negedge RST)

begin

if (!RST)

begin

CNT_EN=0;

LOAD=1;

end

else

begin

CNT_EN=~CNT_EN;

LOAD=~CNT_EN;

end

end

assign CNT_CLR=~(~CLK_1hz&LOAD);

ssign INT=LOAD; //使用LOAD的上升沿使單片機(jī)中斷。

always @(posedge CLKX or negedge CNT_CLR)

begin

if (!CNT_CLR) //當(dāng)CNT_CLR為低電平到來時,OUT=0;計數(shù)器清零

OUT=0;

else if (CNT_EN)

begin

OUT=OUT+1; //當(dāng)CLKX的上升沿到來時,計數(shù)器加1

end end

always @(posedge LOAD) //當(dāng)鎖存信號LOAD的上升沿到來時,執(zhí)行以下語句

begin

FRE=OUT; //將OUT賦值給FRE

end

endmodule

上面給出了可編程邏輯器件EPM7128的計數(shù)模塊的程序關(guān)鍵代碼。CLK_1hz表示門控信號,CLKX表示被測脈沖,RST為系統(tǒng)復(fù)位信號,F(xiàn)RE為鎖存后的脈沖頻率數(shù)據(jù),INT為給單片機(jī)的中斷信號,這幾個信號是計數(shù)模塊中的輸入、輸出信號。在計數(shù)模塊中還有幾個內(nèi)部定義的信號,CNT_EN為計數(shù)允許信號,CNT_CLR為計數(shù)清零信號,LOAD表示鎖存信號,OUT表示鎖存前的脈沖頻率信號。門控信號為10Hz,每兩個時鐘周期進(jìn)行一次頻率測量,即在每兩個時鐘周期CLK_1hz內(nèi),先到來半個時鐘周期的CNT_CLR,用于清零;隨后,CNT_EN在一個時鐘周期 CLK_1hz內(nèi)有效,進(jìn)行計數(shù);最后,在后到來的半個時鐘周期內(nèi),當(dāng)LOAD的上升沿到來時,鎖存計數(shù)結(jié)果。

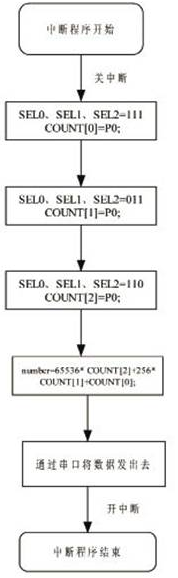

4、51單片機(jī)AT89S52的程序

51單片機(jī)先初始化定時器、串口及中斷設(shè)置等,給EPM7128發(fā)出復(fù)位信號,然后進(jìn)入大循環(huán)程序,等待外中斷。當(dāng)EPM7128計時時間到,給 AT89S52的外中斷0發(fā)出中斷信號,AT89S52的程序跳到外中斷中,進(jìn)行數(shù)據(jù)處理,分別給出選擇信號SEL0~SEL2的組合,分時接收 EPM7128的數(shù)據(jù)信號,再通過串口發(fā)給上位機(jī)。由于所測頻率不會超過10MHz,因此只讀取24位數(shù)據(jù)即可。圖5是外中斷0中斷程序流程圖。

圖5 外中斷0中斷程序流程圖

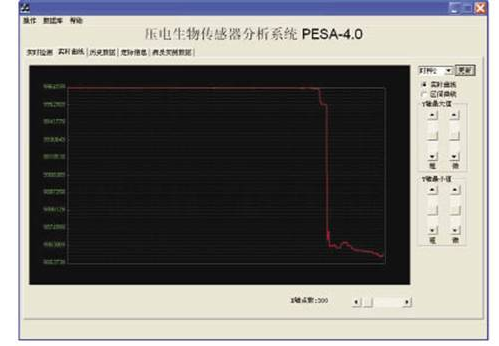

實(shí)驗(yàn)結(jié)果

先往流池內(nèi)加100微升血漿(溫浴180S),旋轉(zhuǎn)螺桿到刻度17.0,然后再通過側(cè)面小孔注射進(jìn)TT凝血酶溶液然后抽出注射器。圖6 所示是直徑6mm血漿凝結(jié)實(shí)驗(yàn)(血漿+TT凝血酶=100+100μl)。此圖是石英晶體采用AT切向,電極為銀膜,基頻I0MHZ,晶體直徑6mm(沒有使用差頻器),直接將10MHz石英晶體的頻率送到可編程邏輯器件計數(shù)的結(jié)果。

QCM作為微質(zhì)量傳感器具有結(jié)構(gòu)簡單、成本低、振動Q值大、靈敏度高、測量精度可以達(dá)到納克量級的優(yōu)點(diǎn),被廣泛應(yīng)用于化學(xué)、物理、生物、醫(yī)學(xué)和表面科學(xué)等領(lǐng)域中。壓電石英晶體傳感器用于凝血因子檢測具有使用方便、精度高和成本低等優(yōu)點(diǎn),有廣闊的臨床應(yīng)用和推廣前景。