摘要:按鍵被廣泛用于基于FPGA的數(shù)字電路系統(tǒng)設(shè)計(jì)中,機(jī)械式按鍵開(kāi)關(guān)在按鍵操作時(shí)經(jīng)常會(huì)出現(xiàn)抖動(dòng)現(xiàn)象,如果不進(jìn)行消除將會(huì)造成電路系統(tǒng)的誤操作。基于此介紹了基于VHDL語(yǔ)言的計(jì)數(shù)器型消抖電路、D觸發(fā)器型消抖電路、狀態(tài)機(jī)型消抖電路的工作原理、相關(guān)程序、波形仿真及結(jié)果分析,并下栽到EP2C35F672C8芯片上進(jìn)行驗(yàn)證,消抖效果良好,性能穩(wěn)定,可廣泛用于FPGA的按鍵電路中。

關(guān)鍵詞:VHDL;消抖;FPGA

0 引言

按鍵開(kāi)關(guān)是許多電子產(chǎn)品不可缺少的輸入設(shè)備,在智能化電子產(chǎn)品中,按鍵開(kāi)關(guān)作為人機(jī)交互的主要器件之一,可以實(shí)現(xiàn)人機(jī)對(duì)話,完成各種功能操作,而機(jī)械式按鍵開(kāi)關(guān)由于其低成本、高可靠性被廣泛使用。在按鍵操作時(shí),機(jī)械觸點(diǎn)的彈性及電壓突跳等原因,在觸點(diǎn)閉合或開(kāi)啟的瞬間會(huì)出現(xiàn)電壓抖動(dòng),實(shí)際應(yīng)用中如果不進(jìn)行處理將會(huì)造成誤觸發(fā)。常見(jiàn)的硬件消抖方法有:利用電容的充放電原理;利用RS觸發(fā)的保持功能;由同相器組成的積分去抖電路;用反相器組成的翻轉(zhuǎn)式去抖電路;不可重復(fù)觸發(fā)單穩(wěn)態(tài)等等。本文采用VHDL語(yǔ)言設(shè)計(jì)了幾種按鍵開(kāi)關(guān)的消抖電路。

1 計(jì)數(shù)器型消抖電路

1.1 計(jì)數(shù)器型消抖電路(一)

計(jì)數(shù)器型消抖電路(一)是設(shè)置一個(gè)模值為(N+1)的控制計(jì)數(shù)器,clk在上升沿時(shí),如果按鍵開(kāi)關(guān)key_in='1',計(jì)數(shù)器加1,key_in='0' 時(shí),計(jì)數(shù)器清零。當(dāng)計(jì)數(shù)器值為2時(shí),key_out輸出才為1,其他值為0時(shí)。計(jì)數(shù)器值為N時(shí)處于保持狀態(tài)。因此按鍵key_in持續(xù)時(shí)間大于N個(gè)clk時(shí)鐘周期時(shí),計(jì)數(shù)器輸出一個(gè)單脈沖,否則沒(méi)有脈沖輸出。如果按鍵開(kāi)關(guān)抖動(dòng)產(chǎn)生的毛刺寬度小于N個(gè)時(shí)鐘周期,因而毛刺作用不可能使計(jì)數(shù)器有輸出,防抖動(dòng)目的得以實(shí)現(xiàn)。clk的時(shí)鐘周期與N的值可以根據(jù)按鍵抖動(dòng)時(shí)間由設(shè)計(jì)者自行設(shè)定。

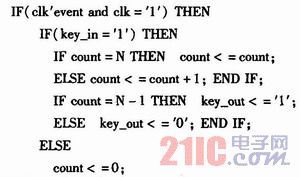

主要程序結(jié)構(gòu)如下:

![]()

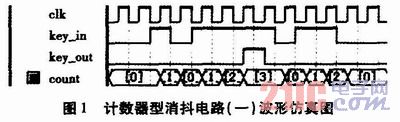

圖1是N為3的波形仿真圖,當(dāng)按鍵持續(xù)時(shí)間大于3個(gè)時(shí)鐘周期,計(jì)數(shù)器輸出一個(gè)單脈沖,其寬度為1個(gè)時(shí)鐘周期,小于3個(gè)時(shí)鐘周期的窄脈沖用作模擬抖動(dòng)干擾,從圖1可以看出,抖動(dòng)不能干擾正常的單脈沖輸出。

該方案的特點(diǎn)是能很好消除按鍵抖動(dòng)產(chǎn)生的窄脈沖,還可以濾去干擾、噪音等其他尖峰波,但遇到脈寬大于N個(gè)Tclk時(shí)鐘周期的干擾、噪音等時(shí)會(huì)有輸出從而產(chǎn)生誤操作,而對(duì)于按鍵操作要求按鍵時(shí)間必須大于N個(gè)Tclk時(shí)鐘周期,否則按鍵操作也沒(méi)有輸出。

1.2 計(jì)數(shù)器型消抖電路(二)

計(jì)數(shù)器型消抖電路(二)是控制計(jì)數(shù)器工作一個(gè)循環(huán)周期(N+1個(gè)狀態(tài)),且僅在計(jì)數(shù)器為0時(shí)輸出為“1”。電路設(shè)計(jì)了連鎖控制設(shè)施。在計(jì)數(shù)器處于狀態(tài)0時(shí),此時(shí)若有按鍵操作,則計(jì)數(shù)器進(jìn)入狀態(tài)1,同時(shí)輸出單脈沖(其寬度等于時(shí)鐘周期)。計(jì)數(shù)器處于其他狀態(tài),都沒(méi)有單脈沖輸出。計(jì)數(shù)器處于狀態(tài)N時(shí),控制en='0',導(dǎo)致計(jì)數(shù)器退出狀態(tài)N,進(jìn)入狀態(tài)0。計(jì)數(shù)器能否保持狀態(tài)0,取決于人工按鍵操作,若按鍵key_ in='1',控制en='1'(計(jì)數(shù)器能正常工作),key_in='0',計(jì)數(shù)器狀態(tài)保持。顯見(jiàn)計(jì)數(shù)器處于狀態(tài)0,人工不按鍵,則計(jì)數(shù)器保持狀態(tài)0。

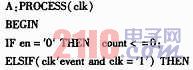

主要程序結(jié)構(gòu)如下:

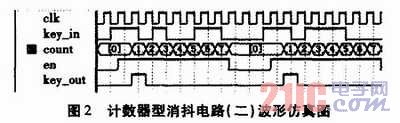

圖2是N為7的波形仿真圖。在計(jì)數(shù)器狀態(tài)為0時(shí),key_in有按鍵操作,計(jì)數(shù)器開(kāi)始連續(xù)計(jì)數(shù)直到計(jì)數(shù)器狀態(tài)為0;計(jì)數(shù)器狀態(tài)為1-7時(shí),key _in任何操作對(duì)計(jì)數(shù)器工作無(wú)影響,計(jì)數(shù)器在狀態(tài)為1時(shí),輸出一個(gè)單脈沖,脈沖寬度為1個(gè)時(shí)鐘周期。

該設(shè)計(jì)方案的特點(diǎn)是能很好消除按鍵抖動(dòng)產(chǎn)生的連續(xù)脈沖,對(duì)按鍵時(shí)間沒(méi)有要求,缺點(diǎn)是在計(jì)數(shù)器狀態(tài)為0時(shí),遇到干擾、噪音等時(shí)會(huì)有輸出,從而產(chǎn)生誤操作。

2 D觸發(fā)器型消抖電路

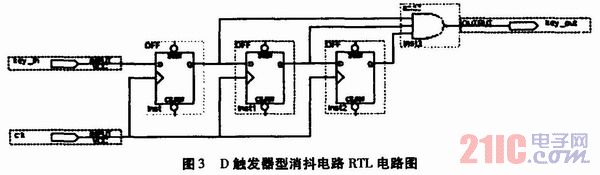

D觸發(fā)器型消抖電路設(shè)計(jì)了三個(gè)D觸發(fā)器與一個(gè)三輸入與門。三個(gè)D觸發(fā)器串行連接,其Q輸出端分別與三輸入與門的輸入端連接,D觸發(fā)器型消抖電路RTL電路如圖3所示。

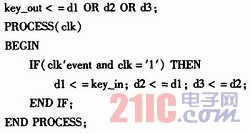

主要程序結(jié)構(gòu)如下:

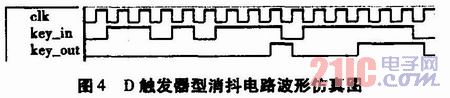

圖4為D觸發(fā)器型消抖電路波形仿真圖,由圖可見(jiàn),當(dāng)按鍵操作時(shí)間大于或等于clk時(shí)鐘周期的3倍時(shí),輸出一個(gè)正脈沖,正脈沖的寬度比key_in少2個(gè)clk時(shí)鐘周期。

D觸發(fā)器型消抖電路與計(jì)數(shù)器型消抖電路(一)相似,計(jì)數(shù)器型消抖電路(一)輸出脈沖寬度是固定的,D觸發(fā)器型消抖電路輸出脈沖寬度隨著按鍵操作時(shí)間長(zhǎng)短變化。

3 狀態(tài)機(jī)型消抖電路

狀態(tài)機(jī)型消抖電路采用有限狀態(tài)機(jī)的設(shè)計(jì)方法來(lái)描述與實(shí)現(xiàn),狀態(tài)機(jī)有S0,S1,S2三種狀態(tài),在S0狀態(tài)下key_out輸出為低電平,并以clk時(shí)鐘信號(hào)的頻率采樣按鍵輸入信號(hào),如果key_in=‘0’,則保持在S0狀態(tài),并繼續(xù)采樣按鍵輸入信號(hào)的狀態(tài),如果key_in=‘1’,則轉(zhuǎn)入S1狀態(tài);在S1狀態(tài)下key_out輸出仍為低電平,繼續(xù)采樣按鍵輸入信號(hào)的狀態(tài),如果key_in=‘1’,則轉(zhuǎn)入S2狀態(tài),如果key_in=‘0’則轉(zhuǎn)入

S0狀態(tài);在S2狀態(tài)下繼續(xù)采樣按鍵輸入信號(hào)的狀態(tài),如果key_in=‘1’,則保持在S2狀態(tài),key_out輸出正脈沖,如果key_in=‘0’,則轉(zhuǎn)入S0狀態(tài),key_out輸出低電平。

主要程序結(jié)構(gòu)如下:

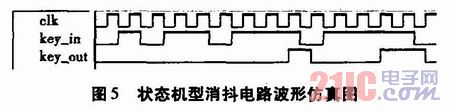

圖5為狀態(tài)機(jī)型消抖電路波形仿真圖,由圖可見(jiàn),該狀態(tài)機(jī)型消抖電路與D觸發(fā)器型消抖電路仿真結(jié)果一致。

4 結(jié)束語(yǔ)

采用VHDL語(yǔ)言實(shí)現(xiàn)按鍵的消抖電路的方法有很多,本文介紹的幾種消抖電路都通過(guò)仿真分析及實(shí)驗(yàn)驗(yàn)證,消抖效果良好,性能穩(wěn)定,而且各有自己的優(yōu)勢(shì)與缺點(diǎn),設(shè)計(jì)者可以根據(jù)設(shè)計(jì)需求選擇使用。