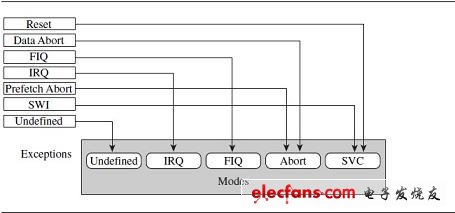

一.ARM處理器異常及其對(duì)應(yīng)的模式

當(dāng)一個(gè)異常發(fā)生時(shí),ARM處理器總是切換到ARM狀態(tài)(即非Thumb狀態(tài))。Thumb指令集沒有包含進(jìn)行異常處理時(shí)需要的一些指令,因此在異常中斷時(shí),還是要使用ARM指令。

每種異常都導(dǎo)致內(nèi)核進(jìn)入一種特定的模式。此外,可以通過修改cpsr,進(jìn)入任何ARM處理器模式。用戶和系統(tǒng)模式是僅有的可不通過相應(yīng)異常進(jìn)入的2中模式。

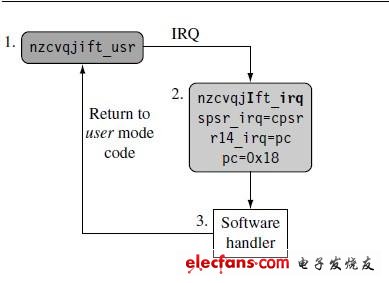

當(dāng)一個(gè)異常導(dǎo)致模式的改變時(shí),內(nèi)核自動(dòng)的:

把cpsr保存到相應(yīng)異常模式下的spsr

把pc保存到相應(yīng)模式下的lr

設(shè)置cpsr為相應(yīng)異常模式

設(shè)置pc為相應(yīng)異常處理程序的入口地址

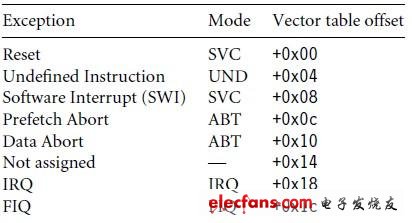

二.向量表

異常發(fā)生時(shí),ARM跳轉(zhuǎn)地址組成的表。

三.異常優(yōu)先級(jí)

復(fù)位異常是優(yōu)先級(jí)最高的異常,一旦復(fù)位異常產(chǎn)生,總是會(huì)發(fā)生復(fù)位異常。注意:當(dāng)一條不屬于ARM或Thumb指令集的指令到達(dá)流水線的執(zhí)行階段時(shí),若此時(shí)沒有其它異常發(fā)生,就會(huì)產(chǎn)生未定義指令異常。ARM處理器會(huì)“詢問”協(xié)處理器,看它能否將其作為一條協(xié)處理器指令來處理。由于協(xié)處理器在流水線之后,所以指令確認(rèn)可以在內(nèi)核的執(zhí)行階段進(jìn)行。如果這條指令不屬于任何一個(gè)協(xié)處理器,則會(huì)產(chǎn)生未定義指令異常。

四.中斷

中斷延時(shí)是指:從外部請(qǐng)求信號(hào)發(fā)出到取出對(duì)應(yīng)的中斷服務(wù)程序(ISR)的第一條指令,這期間的間隔時(shí)間。

五.中斷源及其識(shí)別方法

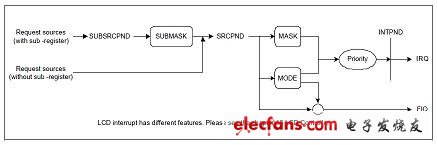

S3C2440A有60個(gè)中斷源,IRQ有兩種中斷識(shí)別方法:向量中斷和非向量中斷。FIQ只有非向量中斷。在IRQ各個(gè)中斷源中的某一個(gè)中斷源的中斷請(qǐng)求被響應(yīng)時(shí),CPU轉(zhuǎn)至0x18處自動(dòng)加載一條轉(zhuǎn)移指令轉(zhuǎn)至相應(yīng)中斷源的固定中斷向量處。IRQ各個(gè)中斷源的向量地址是固定的,每個(gè)占用一個(gè)字單元。IRQ各個(gè)中斷源若采用非向量中斷,任意一個(gè)中斷源發(fā)出中斷請(qǐng)求,都認(rèn)為發(fā)生了IRQ中斷請(qǐng)求,并自動(dòng)轉(zhuǎn)入IRQ中斷服務(wù)程序執(zhí)行。IRQ中斷服務(wù)程序主要功能是將軟件設(shè)定的中斷向量表中相應(yīng)的中斷源服務(wù)程序入口地址送給PC,并轉(zhuǎn)其執(zhí)行。在非向量中斷模式下,一般在IRQ處放置一條轉(zhuǎn)移指令:B IsrIRQ 。其中,IsrIRQ為所有IRQ中斷服務(wù)程序的總?cè)肟诘刂罚彩欠窍蛄恐袛嗄J降闹袛嘣磁袆e及散轉(zhuǎn)程序。