摘 要: 在高速邏輯設(shè)計(jì)中,需要考慮避免出現(xiàn)振鈴、串?dāng)_等傳輸線現(xiàn)象。就此詳細(xì)討論了在Ultra2 SCSI單端" title="單端">單端和差分兩種模式兼容下,其PCB的輸出阻抗與連接電纜的兩種阻抗的匹配問題,并介紹了在這樣的高速邏輯系統(tǒng)中,PCB設(shè)計(jì)通常要考慮的一些其它問題。

關(guān)鍵詞: Ultra2 SCSI Fast-40 印刷電路板 高速邏輯設(shè)計(jì)

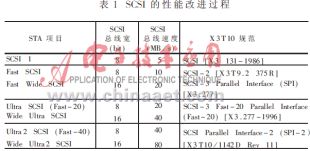

小型計(jì)算機(jī)系統(tǒng)接口(SCSI),是美國ANSI9.2委員會(huì)定義的計(jì)算機(jī)與外設(shè)之間的接口標(biāo)準(zhǔn),可以以更高的數(shù)據(jù)傳輸速率串接7臺或更多不同的外圍設(shè)備。為了滿足外圍設(shè)備不斷增加的速率要求,SCSI得到了長足的發(fā)展。表1顯示了并行SCSI性能的改進(jìn)過程,我們注意到SCSI 的性能幾乎每5年提高一倍。SCSI 的最新版本是Ultra2,它的數(shù)據(jù)傳輸速率是Ultra的兩倍,其中Wide Ultra2 SCSI 速率達(dá)到了80MB/s。

并行SCSI在改進(jìn)性能時(shí)一直保持了向下和向上兼容。這樣,使舊的設(shè)備能夠繼續(xù)使用,而新的設(shè)備也能工作于舊的SCSI版本下。現(xiàn)在并行SCSI的新版本Ultra2采用差分信號IO技術(shù),稱做低電壓差分(LVD),這種技術(shù)可以達(dá)到非常高的傳輸頻率。為了繼續(xù)使用舊的單端(SE)SCSI,一些Ultra2 SCSI設(shè)備能夠兼容單端和低電壓差分模式。這樣,它的印刷電路板(PCB)設(shè)計(jì)就很具有挑戰(zhàn)性,因?yàn)椋琇VD電纜的差分阻抗" title="差分阻抗">差分阻抗是110~135Ω,而單端阻抗通常要低30%~40%,那么PCB對這兩種情況應(yīng)該能夠兼容,也就是用于Ultra2 SCSI的PCB要能具有不同的輸出阻抗來分別匹配連接電纜的差分阻抗和單端阻抗。

1 跡線的特性阻抗

由于SCSI數(shù)據(jù)速率的提高,設(shè)計(jì)PCB就需要克服很多問題。其中隨著傳輸速率的提高,布線的長度及其特性阻抗" title="特性阻抗">特性阻抗就開始變的非常重要。如果跡線的電器長度大于傳輸信號上升沿的一半,這條跡線就應(yīng)被當(dāng)作傳輸線來處理。這一臨界電器長度可以用公式(1)來表示,式中Tr表示輸出電壓的上升時(shí)間,L表示跡線的電感,C表示跡線的總電容。采用Ultra2接口,對于1ns 的上升時(shí)間,臨界電器長度通常近似為3.1 英寸,當(dāng)跡線長度超過了3.1英寸時(shí),跡線就應(yīng)被當(dāng)作傳輸線來對待,那么,其特性阻抗就應(yīng)該與連接電纜的特性阻抗相匹配。否則,就會(huì)因?yàn)镻CB和連接電纜的不匹配而出現(xiàn)振鈴現(xiàn)象使信號質(zhì)量受到極大影響。這樣一來,在PCB的設(shè)計(jì)中,跡線的特性阻抗就成了一個(gè)重要問題,這也是我們下面需要詳細(xì)討論的問題。

對于信號來說PCB可以看作微波傳輸帶或帶狀線或者兼而有之。它們的電特性是由它們的幾何結(jié)構(gòu)和材料特性決定的。圖1顯示了微波傳輸線的結(jié)構(gòu),它的特性阻抗可以用公式(2)來表示,式中Er是基片" title="基片">基片的相對介電常數(shù)。

圖2顯示帶狀線的結(jié)構(gòu),它的特性阻抗可以用公式(3)來表示。

當(dāng)決定是使用微波傳輸帶還是帶狀線時(shí),要考慮PCB的層數(shù)和走線的復(fù)雜程度。在大多數(shù)情況下,微波傳輸帶和帶狀線要混合使用。一旦單端阻抗確定后,差分阻抗就取決于PCB上兩條跡線的間距。差分對" title="差分對">差分對的兩條跡線具有相同的物理交叉和斷面尺寸也是非常重要的。圖3顯示了一差分對跡線的結(jié)構(gòu),公式(4)顯示了微波傳輸帶的差分阻抗,其中Z為單端阻抗。公式(5)顯示了微波帶狀線的差分阻抗。

從前面的公式可以看出單端特性阻抗主要取決于跡線的寬度和厚度、基片的介電常數(shù)和厚度等因素。而差分阻抗則由單端阻抗、差分對的兩條跡線之間的間距和差分對之間的對間距決定,而且布線應(yīng)力求平行、對等,不要歪斜和出現(xiàn)直角轉(zhuǎn)彎,以免改變阻抗。

滿足多模式的關(guān)鍵是有正確的差分阻抗值,同時(shí)有正確的差分對單端的阻抗比。在滿足公式(5)的情況下,差分對跡線的間距近似為基片厚度的5%時(shí),差分對單端的阻抗比是1.35,符合我們的差分對單端阻抗比要求。這里5%并不小,因?yàn)闉榱藵M足單端阻抗要求,往往要選用較厚的基片,另外,差分對的對間距離也至少應(yīng)為差分對的兩條跡線間距的兩倍以上,以減小差分對間的電容耦合和互感。單端和差分阻抗的實(shí)用范圍為20~150Ω,典型值為50~110Ω,而可控阻抗電路板,其所有布線都可匹配在幾個(gè)歐姆左右,通常單端阻抗能保持在50~80Ω。

2 信號的終止

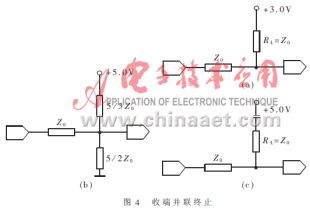

對于沒有從PCB輸出的傳輸線,在末端加入和傳輸線阻抗Z0相等的電阻ZL,能有效地排除傳輸線上的振鈴。最普遍的方法是在接受端采用并聯(lián)終止法,如圖4(a)所示。這樣,收端的反射系數(shù)PL=(RL-Z0)/(RL+Z0)就等于零,這意味著此時(shí)信號線上沒有反射或失真,除了時(shí)延以外,這條線可看作一條直流電路。應(yīng)當(dāng)強(qiáng)調(diào)的是,不管器件位于傳輸線的任何位置,終止電阻都應(yīng)放在線的末尾。在任何情況下也不能把信號線分成一個(gè)T型網(wǎng),分送到幾個(gè)器件中,而是應(yīng)當(dāng)把信號線彎曲地按順序送給不同的器件。

圖4(a)的一個(gè)主要缺點(diǎn)是使用+3V電源。可以用戴維寧等效電路來表示RL和電源,如圖4(b)所示,使系統(tǒng)運(yùn)行在+5V直流下,這樣也能起到很好的作用,但會(huì)消耗額外的電能。

和以上兩種方法相比,在圖4(c)中采用一個(gè)電容串接在RL與+5V之間來隔斷直流消耗的方法可以減少電源的的消耗,也不必使用+3V電源。電容為0.1μF的多層陶瓷電容,市場上已經(jīng)出現(xiàn)了包含電容—電阻的組合件,通常為DIP封裝。和在收段用并聯(lián)終止技術(shù)相對的另一種方法是在發(fā)端采用串聯(lián)終止,這里不再詳細(xì)討論。

無論何時(shí),當(dāng)傳輸線的延遲達(dá)到2TD=TR時(shí),必須考慮傳輸線的影響,即信號的變化時(shí)間TR小于等于信號到達(dá)收端、再反射、返回到發(fā)端的時(shí)間2TD。

3 電容加載

在高速邏輯設(shè)計(jì)中,直流負(fù)載幾乎不會(huì)出現(xiàn)問題,而交流負(fù)載則顯得更加重要。高頻段跡線的特性阻抗和傳輸時(shí)延取決于跡線的電容和電感。公式(6)顯示了跡線的特性阻抗,公式(7)顯示了跡線的傳輸時(shí)延。而在具體計(jì)算PCB的特性阻抗和傳輸時(shí)延時(shí)還需要考慮電容加載問題,電容加載會(huì)使阻抗減小,使傳輸時(shí)延加大。公式(8)顯示了跡線的加載特性阻抗,變量Cd為附加電容,公式(9)顯示了跡線的加載傳輸時(shí)延。在計(jì)算電路的電容時(shí),必須意識到插槽和過孔的附加電容。通常,一個(gè)插槽的附加電容為2pF,而過孔為0.3~0.8pF。連接器的阻抗和長度也必須考慮。

為了確保器件規(guī)定的性能,器件所有負(fù)載的電容,包括信號線的分布電容,不應(yīng)超過器件規(guī)定的電容負(fù)載。作為一條經(jīng)驗(yàn)原則,為了達(dá)到最好的速度/負(fù)載性能,任何一個(gè)器件的最大負(fù)載不應(yīng)超過4~6個(gè)器件。但是,市場上也有一些高反轉(zhuǎn)速率的器件,具有較高的輸出驅(qū)動(dòng)能力。

設(shè)計(jì)高速印刷電路板還應(yīng)該正確選擇介電材料,介電材料的兩個(gè)主要參數(shù)是介電常數(shù)和損耗正切。介電常數(shù)反映介質(zhì)容納電荷的能力,而損耗正切則意味著介質(zhì)將耗散多少能量。常用的G-10和FR-4材料,相對介電常數(shù)為4~5,非常好的材料可以達(dá)到2~3。事實(shí)上,這意味著G-10介電材料必須使用較厚的基片以減少電容。G-10材料足以支持到100MHz的信號,對于更高的頻率,應(yīng)考慮選用Teflon一類的材料,當(dāng)然,這類材料比較昂貴。

可以說,設(shè)計(jì)出具有與SCSI接口電纜阻抗相當(dāng)。并與其差分對單端阻抗比相同的印刷電路板是可行的。它能夠在充分利用Ultra SCSI2的多模式技術(shù)的同時(shí),使信號只有很小的畸變。

此外,對于類似Ultra2 SCSI這樣的高速邏輯電路的系統(tǒng)設(shè)計(jì),信號的反轉(zhuǎn)速率已達(dá)到2~5V/ns,上升時(shí)間低于2ns(多數(shù)在1ns以下)。信號線長度稍長一些就會(huì)出現(xiàn)傳輸線現(xiàn)象,例如振鈴。通常,為了避免發(fā)生這種現(xiàn)象,必須采取下列相應(yīng)步驟:

·線路板中分別使用地層和電源層;

·控制導(dǎo)線之間的距離以減少串?dāng)_;

·多使用去耦電容;

·注意交流負(fù)載;

·終止信號線以減少反射。

同時(shí),還要遵守以下通用規(guī)則:

·跡線沿負(fù)載均勻分布,減小因不連續(xù)而產(chǎn)生的反射;

·關(guān)鍵信號走線避免直角轉(zhuǎn)彎和T型分支;

·考慮插槽和過孔的附加電容;

·盡可能縮短連線;

·使用介電常數(shù)盡可能低的基片;

·使用多層PCB,有可能的話,使用阻抗受控的PCB;

·平衡走線長度,避免歪斜;

·縮短通過連接器的長度;

·器件要有去耦電容;

·在PCB板中,把高速器件和其它部分隔離,這樣能簡化板子的布局和減小高速的區(qū)域。

參考文獻(xiàn)

1 SCSI Parallel Interface-2 (SPI-2).Working DraftAmerican National Standard、1998;Project 1142D

2 Jock Tomlinson.Avoid The Pitfalls of High-Speed Logic Design. Electronics Today、1996;31(3)