隨著上層應(yīng)用軟件的日趨多樣化,現(xiàn)在的便攜式電子產(chǎn)品對嵌入式芯片的功能需求越來越高,單一或僅可以局部定制的傳統(tǒng)芯片已經(jīng)不能滿足需要。因此數(shù)字系統(tǒng)和模擬系統(tǒng)都可以根據(jù)需要靈活定制成為芯片設(shè)計、開發(fā)的發(fā)展方向。Cypress為滿足業(yè)界需要繼PSoC1之后開發(fā)了PSoC3和PSoC5全新可編程模擬和數(shù)字嵌入式芯片。其中PSoC3使用基于單循環(huán)流水線的高性能8051內(nèi)核(67MHz/33MIPS),PSoC5則是基于32位ARM Cortex-M3的內(nèi)核(80MHz/100MIPS);兩者都內(nèi)置閃存、SRAM,支持片外存儲器訪問,在8、16和32bit應(yīng)用中同時實現(xiàn)了高集成度和高靈活性。本文重點講述了PSoC3在多通訊接口設(shè)計中的應(yīng)用,以及如何使用多DMA技術(shù)提高通訊的速度和效率。

一、 Cypress PSoC3芯片介紹

Cypress PSoC3使用基于單循環(huán)流水線的高性能8051內(nèi)核 (67MHz/33MIPS),提供業(yè)界廣泛采用的5.5V至0.5V電壓范圍和低至200nA的休眠電流,可以滿足極低功耗的應(yīng)用場合。PSoC3的高性能模擬子系統(tǒng)和數(shù)字系統(tǒng)都擁有可編程通路,允許將任何模擬或數(shù)字信號(包括可編程時鐘)分配到任何通用I/O引腳,這為使用者提供了真正的“系統(tǒng)級”可編程能力。

Cypress PSoC3的芯片編號是CY8C38xx,該系列芯片依據(jù)功能模塊的不同包含多種芯片。表1是CY8C38xx系列的選型指南,除了表中列出的特性外,每個CY8C38xx芯片還包含:1.024V±0.1%的精密片上電壓參考源,帶PLL的1~66MHz±1%的精密可編程時鐘源,有ECC(錯誤校正碼)功能的Flash,DMA(直接存儲器訪問),4KB可調(diào)試跟蹤的RAM,JTAG/SWD編程/調(diào)試接口,支持片外存儲器訪問等。

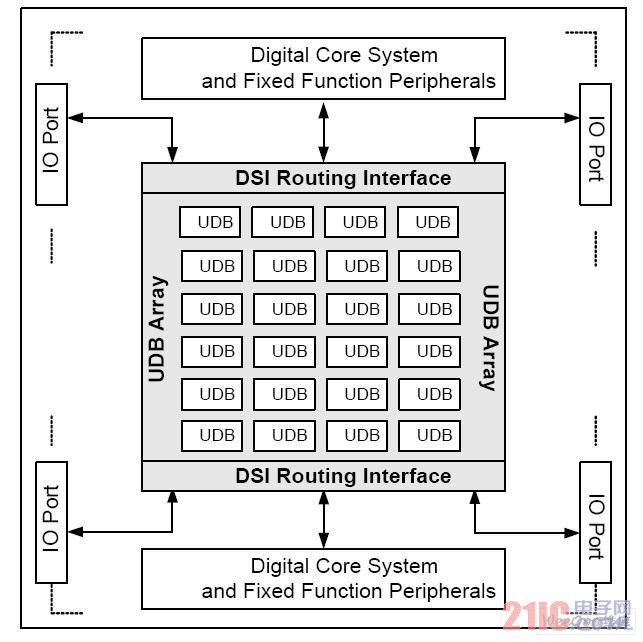

Cypress PSoC3 內(nèi)部采用CPLD的結(jié)構(gòu)實現(xiàn)了完全的數(shù)字可編程電路。圖1顯示了CY8C38xx系列內(nèi)部的可編程邏輯圖。從圖1中可以看出,外設(shè)和邏輯部分可以彼此互聯(lián),也可以連接到任何引腳。數(shù)字可編程邏輯包括了以下部分。

UDB(Universal Digital Blocks)形成了可編程數(shù)字系統(tǒng)的核心功能,由PLD和Data path組成,可以創(chuàng)建各種通用外設(shè)和定制化功能。

UDB Array由多個UDB通過矩陣和可編程互聯(lián)組成,支持UDB和DSI(Digital System Interconnect)之間很靈活的擴展。

DSI是數(shù)字信號的集中互聯(lián),包括UDB,固定功能外設(shè),I/O,中斷,DMA和其它部分的數(shù)字信號。

強大的模擬資源以及靈活的模擬布線資源也是PSoC3的一大亮點之一。圖2是CY8C38系列芯片的片內(nèi)模擬資源圖,通過這些可編程的模擬電路,可以構(gòu)成標準的模擬信號處理模塊。并且這些模擬資源可以通過內(nèi)部的模擬互連子系統(tǒng)進行連接,提供高度的模擬設(shè)計自由度以及IP資源的保護。模擬子系統(tǒng)有以下系統(tǒng)構(gòu)成。

·有模擬全局和局部總線,模擬開關(guān)構(gòu)成的高度可配置的結(jié)構(gòu)。

·高精度的Delta-Sigma ADC.

·支持8位的電壓或者電流DAC.

·四路比較器并且可以有選擇性的互聯(lián)到LUT中.

·多達四個的SC/CT模塊可以構(gòu)成OPAMP等模擬電路

·多達四個內(nèi)部的OPAMP,可以連接到GPIO作為大電流輸出的緩沖器。

·CapSense子系統(tǒng)支持電容觸摸的檢測。

·內(nèi)部高精度參考電壓源。

圖1 CY8C38系列芯片的片內(nèi)可編程數(shù)字系統(tǒng)圖

表1 PSoC3 選型指南

圖2 PSoC3 內(nèi)部模擬資源圖

除了模擬和數(shù)字可編程邏輯外,CY8C38 系列芯片都包含了一個專用于數(shù)字濾波的硬件加速器DFB(Digital Filter Block),它內(nèi)部的專用乘法器和加速器可以在一個系統(tǒng)時鐘內(nèi)計算一個24 位數(shù)與24 位數(shù)的乘法。使用DFB 可以方便的實現(xiàn)FIR 和IIR 數(shù)字濾波器,而且?guī)缀醪徽加肕CU 的資源。在實現(xiàn)濾波器之外,DFB 還可以作為PSoC3 的算法加速器,可以很方便快捷的實現(xiàn)各種數(shù)字算法,而且不需要占用PSoC3 的CPU 資源。

圖3 是DFB 的模塊框圖,典型應(yīng)用是將某個片內(nèi)數(shù)據(jù)源(例如ADC 或某個DMA)的數(shù)據(jù)連接到DFB,經(jīng)DFB 處理后將結(jié)果輸出到另一個片內(nèi)數(shù)據(jù)源(例如DAC 或另一個DMA)。數(shù)據(jù)的移入和移出可以設(shè)定由特定的DMA 控制,也可以由MCU 直接移動。

圖3 DFB 結(jié)構(gòu)圖

除了可編程的資源之外,PSoC3內(nèi)部還提供了特定功能的模塊。這些模塊可以不占用模擬,數(shù)字可編程以及MCU資源,完成相應(yīng)的功能。這些模塊包括:

·支持高達1MBPS的Can總線控制器,兼容ISO-11898-1標準。

·全速USB2.0控制器,支持8個端點和DMA數(shù)據(jù)傳輸控制。

·支持50k/100k/400k/1M BPS的I2C主/從總線控制器,兼容Philips ‘The I2C Specification’ Version 2.1。

·16 Bit專用的定時,計數(shù)和PWM等常用的嵌入式系統(tǒng)模塊。

二、 Cypress PSoC®Creator™ 集成開發(fā)環(huán)境

Cypress PSoC Creator 開發(fā)環(huán)境是Cypress 為PSoC3 / PSoC5可編程片上系統(tǒng)提供的高效,易用的繼承開發(fā)環(huán)境。

該獨特的新型設(shè)計軟件使得工程師能夠按照自己的思維方式進行設(shè)計。使用基于電路圖的方式完成對可編程模擬,數(shù)字以及布線資源的設(shè)計。該軟件還提供了特有的嵌入式系統(tǒng)的組件庫來應(yīng)用其內(nèi)部的資源,通過在組件庫中選擇組件并使用基于電路圖的方式可以使得整個開發(fā)過程就像搭積木一樣,簡單高效的實現(xiàn)工程師的設(shè)計。該軟件工具通過電路綜合可以自動的把用戶的設(shè)計轉(zhuǎn)化成對可編程電路的配置,使得用戶即使不了解芯片的細節(jié)也可以完成復(fù)雜的電路設(shè)計。使用PSoC Creator進行設(shè)計的時候,客戶是根據(jù)應(yīng)用需求急性設(shè)計,而不是目標器件的限制。重新構(gòu)建設(shè)計就像修改程序一樣,不需要復(fù)雜的電路板級修改。

PSoC Creator將一個最新的軟件開發(fā)IDE與一個*性的圖形設(shè)計編輯器結(jié)合在一起,構(gòu)成一個獨特的強有力的軟硬件同步設(shè)計環(huán)境。它提供內(nèi)容豐富的、存有幾十個預(yù)先配置過的模擬和數(shù)字外設(shè)庫,可以方便地拖放進電路圖設(shè)計界面并組成強大的系統(tǒng)。該工具還可以自動為所有片上信號分配管腳,如有需要,甚至還能將I/O分配到最佳管腳。每個外設(shè)元件的參數(shù)均經(jīng)過仔細的配置,以保證應(yīng)用效果能最好地滿足設(shè)計者的要求,且沒有資源浪費。構(gòu)建過程會為每一個元件產(chǎn)生一個一致的、容易記住的API系列,這樣,軟件開發(fā)者即可控制硬件,而無需為基本執(zhí)行指令操心。 定制的設(shè)計及其相關(guān)的API還可以方便地存儲在庫中,用于將來的項目或在組織內(nèi)部分享。

PSoC Creator內(nèi)部包含了全功能免費的編譯器,其獨特的綜合布線工具能夠自動綜合客戶的設(shè)計輸入,并生成相應(yīng)的API。PSoC3的工程采用了工業(yè)界常用的Keil CA51編譯器,而GNU GCC-ARM編譯器也包含其中,能夠針對PSoC5的設(shè)計進行編譯。在綜合,編譯等完成之后,生成兼容Intel Hex格式的配置文件對芯片進行配置。

PSoC Creator目前的版本是: PSoC Creator 1.0 Production. 該軟件運行界面如下圖4。

圖4 PSoC Creator 運行界面

PSoC Creator提供給用戶的設(shè)計入口如下:

● 原理圖編輯器:該編輯器是創(chuàng)建設(shè)計的主要工具。支持對設(shè)計進行原理圖編輯。

● 文本編輯器:該工具允許用戶編輯C,匯編,Verilog, C#等語言代碼。

● 設(shè)計資源編輯器:該工具用于配置整個設(shè)計的參數(shù),包括電源,編譯開關(guān),調(diào)試開關(guān),F(xiàn)LASH保護信息,以及管腳分配等。

● 圖標編輯器:允許用戶創(chuàng)建自己的模塊圖標

● 其他工具:

- 原理圖宏編輯器:允許用戶對原理圖設(shè)置不同的宏以完成不同的功能。

- 原理圖模板編輯器:允許用戶對原理圖的模板進行編輯

- 圖標形狀編輯器:允許用戶在創(chuàng)建模塊以及原理圖中使用自定義的形狀。

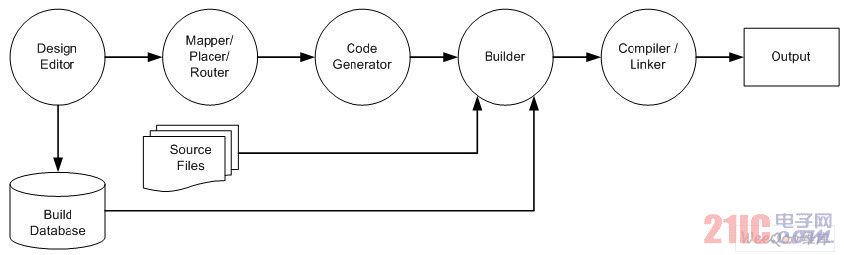

PSoC Creator在用戶通過設(shè)計入口完成設(shè)計之后,對設(shè)計進行一系列的處理并完成最終的結(jié)果輸出。該工具的對工程的構(gòu)建過程如圖5所示。

圖5 PSoC Creator工程構(gòu)建過程

從圖5中可以看出,工程構(gòu)建過程包括以下步驟:

·通過設(shè)計輸入接口完成設(shè)計

·綜合器完成對電路圖的綜合,并進行布局,布線,映射等工作

·代碼生成器生成對應(yīng)電路的API控制接口

·構(gòu)建器準備設(shè)計源文件,讀取構(gòu)建數(shù)據(jù)庫,獲得構(gòu)建配置,庫文件等信息

·編譯器完成編譯,鏈接器對生成的文件進行鏈接

·輸出配置Hex文件。

三、 Cypress PSoC3應(yīng)用于多通訊接口的DMA設(shè)計

DMA是PSoC3中用于處理快速數(shù)據(jù)搬運的模塊。DMA的控制器可以在不需要CPU干預(yù)的情況下處理數(shù)據(jù)的傳輸。通過DMA處理數(shù)據(jù)傳輸可以有效地降低CPU的負擔,同時也能夠提高數(shù)據(jù)傳輸?shù)臅r間。PSoC3內(nèi)置的DMA可以完成四種基本的數(shù)據(jù)傳輸:

·內(nèi)存到內(nèi)存

·內(nèi)存到外設(shè)

·外設(shè)到內(nèi)存

·外設(shè)到外設(shè)

PSoC3中,采用PHUB來連接各個內(nèi)部設(shè)備。DMA和CPU都需要使用PHUB來完成數(shù)據(jù)傳輸。PHUB上的兩個主設(shè)備分別是DMA和CPU,而從設(shè)備是內(nèi)存,外設(shè)以及控制和配置寄存器。PSoC3支持多個DMA的通道,DMA主控制器對通道的請求按照優(yōu)先級進行仲裁。單個DMA的通道可以傳輸高達64KB的數(shù)據(jù)。

PSoC3的DMA控制器支持如下特性:

·支持24個DMA通道

·8優(yōu)先級判決

·128個事務(wù)描述符

8/16/32 位的數(shù)據(jù)傳輸

·完全可配置的源和目標地址

·兼容不同數(shù)端

·在完成數(shù)據(jù)傳輸之后能夠生成中斷

·DMA 向?qū)軌蚣铀倩贒MA 的開發(fā)

·DMA 事務(wù)可以有可編程數(shù)字邏輯或者CPU 觸發(fā)

·支持多個DMA 通道和描述符的級聯(lián)以完成復(fù)雜的功能。

3.1 在PSoC Creator 中使用DMA

PSoC Creator 做為PSoC3 和PSoC5 開發(fā)的設(shè)計工具,其內(nèi)部集成了DMA 模塊來配置DMA 和生成相關(guān)的控制代碼,同時提供的DMA 向?qū)崿F(xiàn)了圖形化操作界面。

DMA 模塊位于組件窗口的System 目錄下,如圖所示。

圖6 DMA 模塊位置

通過拖曳到原理圖編輯器可以放置DMA 模塊,每次拖曳的DMA 會使用一個通道。DMA 模塊的輸入輸出地址等需要在代碼中進行配置,而通過原理圖配置的都是控制管腳和控制信息。在原理圖上DMA 模塊的表現(xiàn)如下圖7 所示。

圖7 DMA 模塊

它的輸入輸出的管腳共有三個。

nrq - 輸出管腳。該管教用于表征DMA的傳輸完成,用來通知中斷控制器產(chǎn)生中斷或者用來觸發(fā)其他邏輯。當完成傳輸之后DMA會生成一個2個總線周期的脈沖。

drq - 輸入管腳(可選)。該管腳是可選管腳,只有在觸發(fā)條件選擇為硬件的時候才可見。該管腳可以連接到產(chǎn)生DMA事務(wù)請求的模塊,觸發(fā)條件可以配置成電平觸發(fā)或邊沿觸發(fā)。

trq - 輸入管腳(可選)。該管腳是可選管腳,只有在結(jié)束條件選為硬件時才可見。該管腳觸發(fā)之后,DMA會停止數(shù)據(jù)傳輸。

在配置完成硬件連接以后,使用配置向?qū)硗瓿蓪MA的如下參數(shù)的配置:

·Byte Per Burst - 每次執(zhí)行Burst傳輸傳送的字節(jié)數(shù)

·Transaction Descriptor 的數(shù)量

·Endian (Big / Little)的配置

·傳輸?shù)淖止?jié)數(shù)

·目標地址

·源地址

·地址遞增模式

·TD連接模式

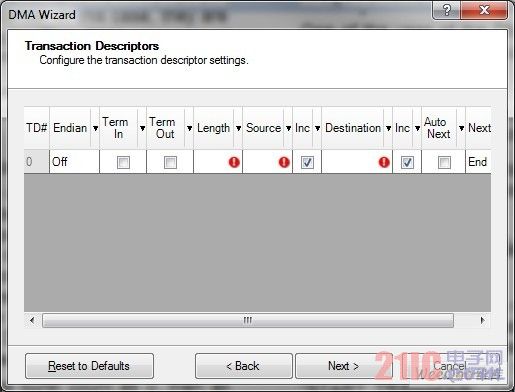

在PSoC Creator中打開DMA向?qū)Вx擇要配置的DMA,進入第一個頁面如圖8所示。

圖8 DMA 向?qū)?-配置

該界面主要配置目標和源地址的范圍。支持地址段在SRAM,FLASH,EEPROM中。其次是配置Burst的字節(jié)數(shù)以及該DMA中的事務(wù)描述符的數(shù)量和連接關(guān)系。在完成該步驟之后,會進入下個配置界面,主要配置其他的詳細參數(shù)。如圖9 所示。

圖9 DMA詳細配置

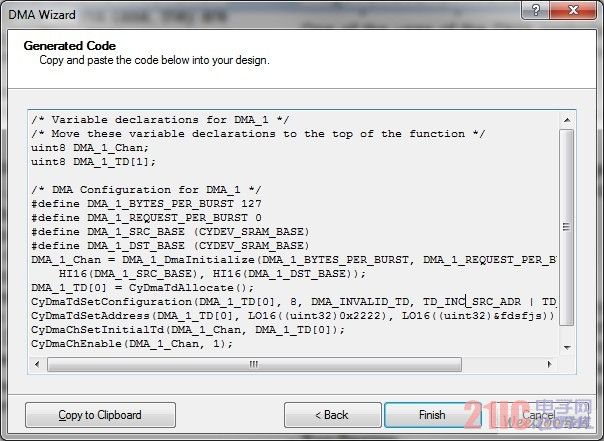

在圖9中輸入事務(wù)描述符號的參數(shù)。其中最為常用而且重要的參數(shù)包括:源地址,目標地址,地址遞增模式,以及事務(wù)描述符的連接模式。在完成該步驟之后,點擊下一步,就會生成相應(yīng)的配置代碼,如圖10所示。

圖10 DMA 生成代碼

復(fù)制上述代碼到程序的初始化模塊中,并對需要的地方進行細微的修改,就可以完成DMA的初始化。在程序運行時,DMA會根據(jù)請求自動把數(shù)據(jù)從源地址搬運到目標地址。

3.2 DMA應(yīng)用于多通訊端口實例

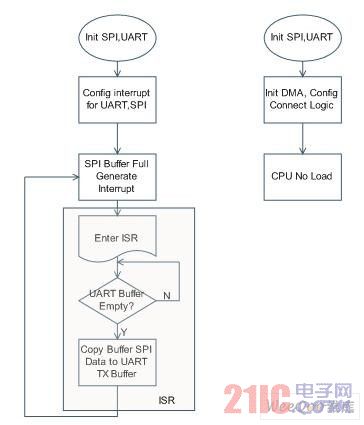

DMA的數(shù)據(jù)傳輸可以極大提高基于PSoC3系統(tǒng)的吞吐率。以一個系統(tǒng)為例,該系統(tǒng)通過SPI接收別的系統(tǒng)的輸入,并通過UART傳送到主機系統(tǒng)中。圖11給出了基于傳統(tǒng)MCU和基于PSoC3 DMA的兩種程序流程圖進行比較(不考慮兩種傳送速率不匹配的情況)。

圖11 (a) 傳統(tǒng)MCU設(shè)計 (b) PSoC3 DMA的設(shè)計

傳統(tǒng)的MCU需要初始化SPI和UART通訊模塊,并配置兩者的中斷。當SPI的Buffer滿了之后,就產(chǎn)生中斷,中斷程序首先中止新的SPI傳輸,然后檢測UART的Buffer,如果不為空就等待舊的數(shù)據(jù)傳送完。為空之后就把SPI的數(shù)據(jù)復(fù)制到TX Buffer 并打開SPI接收后續(xù)數(shù)據(jù)。

基于PSoC3 DMA的設(shè)計中,可以基于原理圖實現(xiàn)上述的邏輯。如圖12所示。

圖12 系統(tǒng)邏輯圖

當SPI的Full信號和UART的Empty信號同時有效的時候,觸發(fā)DMA傳輸,把SPI Buffer中的數(shù)據(jù)傳送到UART的Buffer中。不需要CPU的干預(yù)就能夠完成多通訊口之間的數(shù)據(jù)共享。

該通訊實例只是為了表明DMA在多通訊端口數(shù)據(jù)傳輸中的作用。在實際的實現(xiàn)中,DMA可以操作的通訊端口包括:

·USB的端點

·UART的Buffer

·SPI的Buffer

·I2S的Buffer

·其他各種自定義的通訊協(xié)議

通過DMA可以高效的實現(xiàn)通訊接口之間的如下操作:

·各通訊端口之間的數(shù)據(jù)搬移

·通訊端口Buffer到PSoC3數(shù)字和模擬模塊之間的傳輸

·通訊端口Buffer自動存放到內(nèi)存之中

·內(nèi)存到通訊口的數(shù)據(jù)搬移

·數(shù)字、模擬模塊到通訊口的數(shù)據(jù)搬移

四、 總結(jié)

Cypress PSoC3處理器集成了多種可編程的數(shù)字模擬資源以及布線資源,以及一些專用的通訊和控制設(shè)備,可以極大地方便各種嵌入式系統(tǒng)的應(yīng)用。PSoC Creator作為PSoC3的開發(fā)工具,能夠提供基于原理圖,功能組件的設(shè)計模式。使得用戶能夠用簡單有效的方式來完成復(fù)雜的可編程系統(tǒng)設(shè)計。

通訊作為嵌入式系統(tǒng)的重要部分,在傳統(tǒng)設(shè)計中需要占用一定的CPU時間來處理。本文介紹的基于PSoC3的新設(shè)計方式,采用DMA高效的處理嵌入式系統(tǒng)通訊而不占用CPU處理時間,同時還可以基于PSoC3的靈活配置實現(xiàn)多路DMA并行操作以降低系統(tǒng)硬件成本。這種新方式能夠極大地提高基于PSoC3系統(tǒng)的吞吐能力和系統(tǒng)運行效率。