摘要:為了在虛擬儀器設計中使用以太網(wǎng)總線來將數(shù)據(jù)采集系統(tǒng)納入局域網(wǎng)甚至Internet,從而實現(xiàn)虛擬儀器的網(wǎng)絡化,文中給出了一款基于TCP/IP協(xié)議專用芯片的以太網(wǎng)接口的設計方法。此接口選用Altera公司的FPGA芯片EPM570GT100C4,并配合專用協(xié)議集成芯片W3150A+和物理層芯片RTL8201,可成功實現(xiàn)以太網(wǎng)的數(shù)據(jù)傳輸。

關鍵詞:虛擬儀器;以太網(wǎng);W3150A+

0 引言

虛擬儀器以其性價比高、開放性強等優(yōu)勢迅速占領了市場,并成為測控儀器新的經(jīng)濟增長點。步入信息化時代最顯著的標志就是信息網(wǎng)絡在各行業(yè)中的滲透和普及,其中以太網(wǎng)最為典型。以太網(wǎng)作為一種成本低廉、吞吐能力強、適應性好、網(wǎng)絡管理能力日益提高的網(wǎng)絡,它可以方便地將數(shù)據(jù)采集系統(tǒng)納入局域網(wǎng)甚至Internet。而以太網(wǎng)總線則有可能代替現(xiàn)行的其他總線方式而成為虛擬儀器數(shù)據(jù)采集系統(tǒng)的首選接口。

1 以太網(wǎng)接口的總體設計

1.1 以太網(wǎng)接口設計方案選擇

以太網(wǎng)接口的設計通常有三種方案:其一是采用FPGA實現(xiàn)物理層、網(wǎng)絡層、接入層和傳輸層等各層的描述,該方案要自行實現(xiàn)復雜的TCP /IP協(xié)議,難度較大;二是基于物理層網(wǎng)絡控制器和微處理器來實現(xiàn)網(wǎng)絡傳輸,該方案的優(yōu)點是靈活性強,可以針對不同的系統(tǒng)采用不同的協(xié)議,可實現(xiàn)協(xié)議的精簡:三是采用專用的協(xié)議處理芯片實現(xiàn)以太網(wǎng)數(shù)據(jù)傳輸,該方案的硬件電路相對簡單,開發(fā)周期短,并有越來越多的芯片可供選擇,且集成了多種協(xié)議,使用十分方便。

本設計采用第三種接口方案,即采用專用的TCP/IP協(xié)議集成芯片,并由FPGA實現(xiàn)對協(xié)議處理芯片的控制,從而實現(xiàn)以太網(wǎng)數(shù)據(jù)傳輸。協(xié)議處理芯片選用內(nèi)部固化了TCP/IP協(xié)議的W3150A+并配合物理層芯片RTL8201,該方法硬件電路相對簡單,并可利用邏輯硬件實現(xiàn),從而使系統(tǒng)設計更加簡單、緊湊。

1.2 以太網(wǎng)控制芯片W3150A+簡介

W3150A+是WIZnet公司專門為以太網(wǎng)互聯(lián)和嵌入式系統(tǒng)推出的TCP/IP協(xié)議棧芯片。W3150A+能夠?qū)崿F(xiàn)TCP、UDP、IP Ver.4、DHCP、ARP和ICMP等協(xié)議,同時,網(wǎng)絡接口層(包括MAC子層和DLC子層)也可在該芯片中實現(xiàn)。同時還能提供四路網(wǎng)絡連接,其內(nèi)部有16KB的雙口RAM可

作為數(shù)據(jù)緩沖區(qū),并可支持全雙工模式,同時帶有標準的MD接口,可方便連接物理層接口芯片。此外,WIZnet公司還提供了Socket API程序包,可以加速應用程序的開發(fā)。

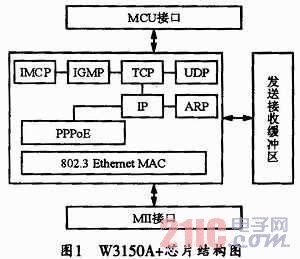

圖1所示是W3150A+芯片的結構框圖。由圖1可見,W3150A+主要由4部分組成。其中第一部分是MCU接口。W3150A+提供有直接總線接口、

間接總線接口和SPI總線接口。既適合與類似8051單片機的總線連接,也非常適合與只有IO口而沒有總線接口的控制器連接;第二部分是TCP /IP協(xié)議棧。W3150A+已經(jīng)完全固化了從MAC層、網(wǎng)絡層到傳輸層所需要的協(xié)議,因此,用戶無需了解這些協(xié)議的具體實現(xiàn)方法和實現(xiàn)代碼;第三部分是接收和發(fā)送緩沖區(qū),通過以太網(wǎng)進行通信的數(shù)據(jù)就是通過這些緩沖區(qū)來交換的;第四部分是以太網(wǎng)物理層接口(MII接口)。W3150A +可以與物理層芯片RTL8201無縫連接,從而實現(xiàn)10/100BaseT以太網(wǎng)物理接口。

W3150A+內(nèi)部的寄存器分為兩個存儲器和兩類寄存器。兩個存儲器分別用于數(shù)據(jù)傳輸?shù)妮斎牒洼敵觯瑑深惣拇嫫鞣謩e是通用寄存器和端口寄存器,每類寄存器都含有大量的狀態(tài)字控制寄存器。下面簡要介紹比較重要的狀態(tài)字控制寄存器。

Sn_MR:端口n模式寄存器,該寄存器用于設置端口的選項或協(xié)議類型;

Sn_CR:端口n命令寄存器,該寄存器用來設置端口的初始化、關閉、建立連接、斷開連接、數(shù)據(jù)傳輸以及命令接受等;

Sn_IR:端口n中斷寄存器,該寄存器用于顯示建立和中止連接、接收數(shù)據(jù)、發(fā)送完成以及時間溢出等信息;

Sn_PORT:端口n的端口號寄存器,該寄存器可在TCP或UDP模式下設定對應的端口號;

S_TX_FSR:端口n發(fā)送存儲器剩余空間寄存器,該寄存器用于指示用戶可以使用的發(fā)送數(shù)據(jù)空間的大小,在發(fā)送數(shù)據(jù)前,用戶必須先檢查剩余空間的大小,然后控制發(fā)送數(shù)據(jù)的字節(jié)數(shù);

Sn_TX_RR:端口n發(fā)送存儲器讀指針寄存器,該寄存器用于指示端口在發(fā)送過程完成后發(fā)送存儲器的當前位置。當端口n的命令寄存器收

到SEND命令后,可隨即從當前Sn_TX_RR到Sn_TX_WR的數(shù)據(jù)中發(fā)送出去,發(fā)送完成后,Sn_TX_RR的值自動改變;

Sn_TX_WR:端口n傳輸寫指針寄存器,該寄存器可指示向TX存儲器寫入數(shù)據(jù)時的地址;

Sn_RX_RSR:端口n接收數(shù)據(jù)字節(jié)數(shù)寄存器,該寄存器只是端口接收數(shù)據(jù)緩沖區(qū)接收數(shù)據(jù)的字節(jié)數(shù),通常可由Sn_TX_RR到Sn_TX_WR的值計

算得出,向端口n命令寄存器寫入RECV命令后,寄存器的值將自動改變,并可以接收遠程對端的數(shù)據(jù);

Sn_RX_RD:端口n接收緩沖區(qū)讀指針寄存器,該寄存器只是端口接收過程完成后的讀地址信息。

W3150A+內(nèi)部有4個獨立的端口(Socket),它們的狀態(tài)、控制分別映射在第二到第五寄存器區(qū)。主要用于實現(xiàn)端口工作模式的控制(TCP服

務器、TCP客戶端、UDP或PPPOE等)、設置該端口的端口號,設置該端口目的主機IP地址和端口號,以及端口接收和發(fā)送數(shù)據(jù)控制等。

2 以太網(wǎng)接口的硬件設計

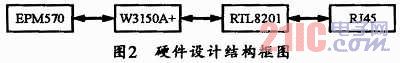

本接口的硬件設計主要包括FPGA與W3150A+的接口設計,物理層芯片RTL8201與W3150A+的接口設計以及時鐘模塊和電源模塊的設計。其硬件設計框圖如圖2所示。

2.1 W3150A+與FPGA的接口設計

隨著半導體技術的飛速發(fā)展,F(xiàn)PGA(Field Programmable Gate Array)的計算能力、容量以及可靠性有了很大的提高。它正以高度靈活的用戶現(xiàn)場編程功能、反復可改寫功能、高可靠性等優(yōu)點,成為數(shù)字電路、數(shù)字信號處理等領域的新寵。

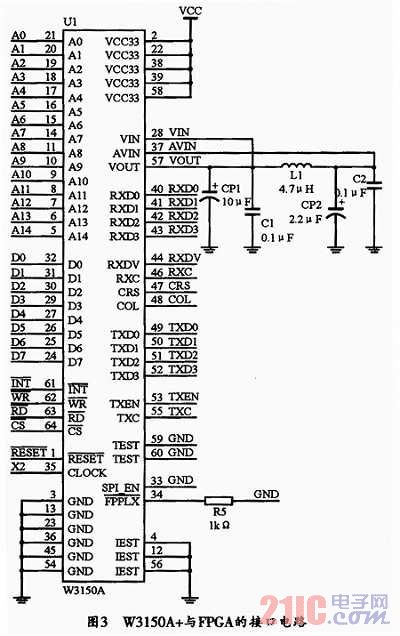

考慮到成本、實用性以及功耗,本設計選用的FPGA芯片是Altera公司MAXII系列的EPM570GT100C4。MAXII系列器件是一種非易失性CPLD,采用0.18μm的制造工藝,并包含有240到2210個邏輯單元和8Kbits非易失性存儲器,它相對于其他的CPLD可以提供快速、穩(wěn)定、數(shù)量更多的I/O管腳。

W3150A+與微處理器芯片的接口方式有三種:直接總線接口模式、間接總線接口模式和SPI模式。其中直接總線接口模式適用于大數(shù)據(jù)量傳輸?shù)那闆r;SPI模式的接口連線較少,適用于數(shù)據(jù)量不大,傳輸速率相對較低的情況;間接總線接口模式下的數(shù)據(jù)傳輸性能則介于它們兩者

之間。本系統(tǒng)采用直接總線接口模式,以便最大限度地提高數(shù)據(jù)的傳輸速率。其具體的接口電路如圖3所示。

2.2 物理層芯片與W3150A+的接口設計

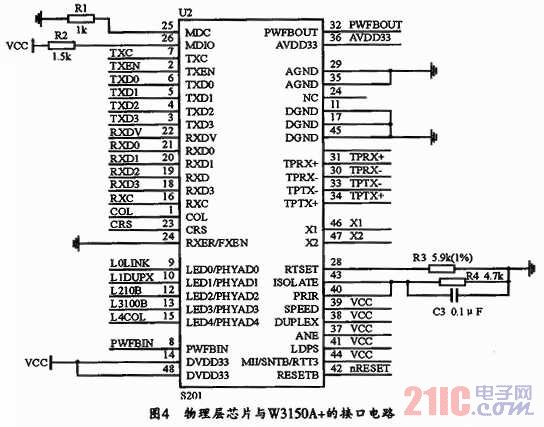

RTL8201BL是一個單端口的物理層收發(fā)器,它只有一個MII/SNI(媒體獨立接口/串行網(wǎng)絡接口)接口。可用于實現(xiàn)全部的10/100M以太網(wǎng)物理層功能,包括物理層編碼子層(PCS)、物理層介質(zhì)連接設備(PMA)、雙絞線物理媒介相關子層(TP~PMD)、10Base-Tx編解碼和雙絞線媒介訪問單元(TPMAU)。PECL接口可支持連接一個外部的100Base-FX光纖收發(fā)器。這款芯片使用先進的CMOS工藝制作,可以滿足低壓低功耗的需求。

RTL8201BL與W3150A+可通過標準MII接口相連,其中引腳RX_CLK、RXDV、RXD[0:3]以及COL用于數(shù)據(jù)的接收,而TX_CLK、TXE、TXD[0:3]用于數(shù)據(jù)的發(fā)送。其具體的電路圖如圖4所示。

3 數(shù)據(jù)傳輸?shù)膶崿F(xiàn)過程

通過控制器對寄存器進行讀寫訪問操作,W3150A+就可以進行網(wǎng)絡連接。下面介紹具體的操作過程。

首先應進行初始化。初始化設置包括基本設置、網(wǎng)絡信息設置,端口存儲器信息設置等,設置完后就可進行數(shù)據(jù)傳輸。數(shù)據(jù)傳輸可以

采用TCP、UDP、IP_RAW和MAC_RAW模式進行,并可在端口n模式寄存器(Sn_MR)的協(xié)議類型中選擇通信模式。其中,基本設置包括模式寄存器(MR)、中斷屏蔽寄存器(SIMR)、重發(fā)時間寄存器(RTR)、重發(fā)計數(shù)寄存器(RGR)等;設置網(wǎng)絡信息包括設定網(wǎng)關(GAR)、設定源硬件地址(SHAR)、設定子網(wǎng)掩碼(SUBR)、設定源IP地址(SIPR)等;而設置端口存儲器信息則主要是設定發(fā)送緩沖區(qū)和接收緩沖區(qū)的大小分配,具體可通過設置RMSR、TMSR寄存器實現(xiàn)。

本系統(tǒng)在FPGA芯片EPM570GT100C4的基礎上可利用軟件Quartus II來開發(fā)邏輯控制功能,從而實現(xiàn)對W3150A+的控制。其主要端口如下:

nrst:復位輸入鍵,低電平有效;

clk:時鐘輸入;

nwrst:復位輸出,可復位W3150A+和RTL8201;

nwr:對W3150A+寫使能信號,低電平有效;

nrd:對W3150A+讀使能信號,低電平有效;

ncs:W3150A+片選信號,低電平有效;

address:15位地址信號;

data:8位數(shù)據(jù)信號;

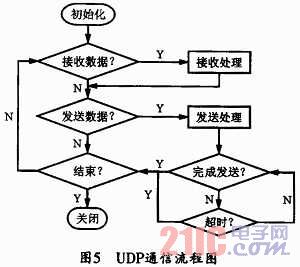

本接口通信設計采用的是UDP通信方式,其通信流程圖如圖5所示。

端口初始化主要是對端口進行初始化,包括設置UDP模式、設置端口號,設置OPEN命令;通過Sn_RX_RSR寄存器的值可檢測是否收到數(shù)

據(jù),若非零,即進入數(shù)據(jù)接收處理;接收處理時,首先讀取Sn_RX_RSR寄存器的值,即接收數(shù)據(jù)字節(jié)數(shù),然后計算偏址和實際物理地址,再根

據(jù)物理地址讀取數(shù)據(jù)。在讀取數(shù)據(jù)過程中,如果物理地址到達該端口設定的高限地址,則先讀高限地址的數(shù)據(jù),然后將物理地址改為基地址,然后再從基地址繼續(xù)讀取剩余的數(shù)據(jù)。讀完所有的數(shù)據(jù)后,可將Sn_RX_RR的值加上讀取的數(shù)據(jù)長度,然后寫入sn_RX_BASE,最后再向端口n的指令寄存器寫入RECV命令。

發(fā)送數(shù)據(jù)?/發(fā)送處理的實現(xiàn)過程是首先讀取S_TX_FSR寄存器的值以便能使用發(fā)送數(shù)據(jù)空間的大小來計算偏址和實際物理地址,然后再從

物理地址寫入要發(fā)送的數(shù)據(jù)。在發(fā)送數(shù)據(jù)過程中,如果物理地址已到達該端口設定的高限地址,則先將數(shù)據(jù)寫入高限地址,然后再將物理地

址改為基地址,接著從基地址繼續(xù)寫入數(shù)據(jù)。寫完所有的數(shù)據(jù)后,再將Sn_TX_WR的值加上發(fā)送的數(shù)據(jù)長度,然后寫入Sn_TX_BASE,最后向端

口n的指令寄存器寫入SEND命令。

發(fā)送完成的確定可在發(fā)送(SEND)命令后,通過檢測Sn_CR的值來判斷數(shù)據(jù)是否全部發(fā)送完成。

當遠程對端不存在或數(shù)據(jù)傳輸不正常時,將產(chǎn)生超時錯誤。此次可以通過對Sn_IR(TIMEOUT bit)檢測來判斷是否超時。

當操作全部完成時,應關閉窗口,即將Sn_CR寄存器置為CLOSE。

4 結束語

本文介紹了以太網(wǎng)接口的設計及其數(shù)據(jù)傳輸?shù)膶崿F(xiàn)過程。利用本文的方法可以使以太網(wǎng)接口正常運行,故可為后續(xù)的虛擬儀器開發(fā)奠定基礎。事實上,本方法已經(jīng)過多次試驗證明:完全滿足工程需要。