全球衛(wèi)星導航具有政治、經(jīng)濟、軍事等多方面的重要意義,世界各大國和國家集團都在競相發(fā)展全球定位衛(wèi)星系統(tǒng)。目前4大衛(wèi)星導航系統(tǒng)(GPS,Galileo,GLONASS以及中國的BD-2)并存的格局日漸端倪,多個導航衛(wèi)星星座的建立使多星座兼容操作成為可能。對多星座兼容接收機而言,同一時刻可視衛(wèi)星的數(shù)量增加,一方面使系統(tǒng)的可用性得到了提高,另一方面使衛(wèi)星的選擇范圍擴大,有利于我們采用選星策略去選擇位置更好的衛(wèi)星,提高定位精度等。GPS是目前世界上最成熟的衛(wèi)星導航系統(tǒng),BD-2是我國自主研發(fā)的新一代衛(wèi)星導航系統(tǒng)。目前,對G-PS/BD-2兼容接收機的研究還處于起步階段。針對GPS和BD-2開展研究,對于我國國家經(jīng)濟安全和國防安全意義重大。

隨著GPS抗干擾技術(shù)的發(fā)展,為了實現(xiàn)數(shù)字波束形成,在此基礎(chǔ)上,加上某種自適應抗干擾算法,現(xiàn)代的GPS接收機一般都采用陣列天線,要求有多個天線接收通道。因此多通道多載波的DDC設(shè)計是實現(xiàn)GPS/SD-2接收機的重要基礎(chǔ),也是設(shè)計實現(xiàn)中的難點,隨著DDC通道數(shù)增加硬件資源開銷增大,增加了硬件設(shè)計的困難。這里采用專用數(shù)字下變頻器件ISL5416,結(jié)合實際工程需求完成了16陣元GPS/BD-2接收機的DDC設(shè)計。

1 系統(tǒng)整體結(jié)構(gòu)設(shè)計

1.1 整體結(jié)構(gòu)

該系統(tǒng)設(shè)計有16個天線陣元。接收的信號有GPS的L1波段,信號頻帶為(1575.42±1.023)MHz,BD-2的B1波段,信號頻帶為(1561.098± 2.046)MHz。

接收機總體框圖如圖1所示。16個天線分別對應16個射頻通道,射頻通道只是信號通路,信號經(jīng)過射頻通道沒有發(fā)生性質(zhì)變化,只是信號頻譜從射頻搬移到中頻。接收機對北斗和GPS信號的接收共用一個射頻通道,并且這一射頻通道在結(jié)構(gòu)上也更加簡化。ADC輸出的數(shù)字信號仍然屬于多載波的中頻信號,需通過2個DDC通道作下變頻處理從而分別得到GPS和BD-2信號的數(shù)字基帶信號。因此,最終實現(xiàn)16個陣元的信號接收需要32個DDC通道,ISL5416是4通道DDC,8片ISL5416組合的結(jié)構(gòu)能夠?qū)崿F(xiàn)系統(tǒng)要求。

1.2 工作原理

軟件無線電中,信號的解調(diào)是在基帶上完成的,因此基于低通或帶通采樣得到的數(shù)字中頻信號都需要通過數(shù)字正交變頻技術(shù)轉(zhuǎn)換為數(shù)字基帶信號。數(shù)字下變頻器是將實數(shù)的數(shù)字中頻信號轉(zhuǎn)換為復數(shù)的數(shù)字基帶信號,其正交性由數(shù)控振蕩器(NCO)輸出的正交本振來保證。經(jīng)下變頻的數(shù)字基帶信號一般都有比較嚴重的過采樣狀態(tài),因此在下變頻中要進行抽取處理,降低數(shù)據(jù)率,減輕后續(xù)處理的負擔。數(shù)字下變頻框圖如圖2所示。

2 設(shè)計實現(xiàn)

2.1 器件選型

目前數(shù)字下變頻器主流實現(xiàn)方案有2種:FPGA方案和ASIC芯片方案。

1)FPGA擅長并行運算和流水線處理,能夠滿足DDC對高速處理需求,另外,由于FPGA設(shè)計的靈活性,使DDC模塊能根據(jù)具體系統(tǒng)的需求量身定制,實現(xiàn)資源和性能的優(yōu)化,特別適合一些需要高帶寬或特殊采樣率的場合。其缺點是參數(shù)調(diào)整的靈活性差難以實現(xiàn)可變帶寬,程序的效率和可靠性難以保證,開發(fā)調(diào)試難度大,另外占用FPGA資源較多。

2)由于DDC在無線電系統(tǒng)中應用廣泛,DDC專用芯片(ASIC)的性能經(jīng)過嚴格驗證,其可靠性和穩(wěn)定性相對FPGA程序要高很多,用戶可靈活配置其內(nèi)部參數(shù)以實現(xiàn)不同指標。但ASIC的結(jié)構(gòu)固定,處理性能有一定局限。目前常見的DDC專用芯片有Intersil公司的單通道DDC HSP5001 6,HSP50214.4通道的DDC HSP50216,ISL5416;ADI公司的集成ADC和4/6個DDC通道的AD6654。

綜合考慮該系統(tǒng)設(shè)計要求DDC通道數(shù)較多,并要求將寬帶數(shù)字中頻信號中不同載頻和帶寬的信號分離到中頻,因此這里采用ISL5416型DDC。ISL5416是4通道大動態(tài)范圍寬帶可編程DDC,每個通道有獨立的NCO、混頻器、數(shù)字濾波器、AGC和重采樣濾波器,每個通道都可以獨立編程并且實時更新,能夠通過將各個通道級聯(lián)或者多相濾波以增加處理帶寬,其功能框圖如圖3所示。

2.2 DDC電路及參數(shù)設(shè)計

本設(shè)計系統(tǒng),信號經(jīng)射頻通道下變頻到中頻后,信號頻帶分別為GPS:(67.42±1.023)MHz,BD-2:(53.098±2.046)MHz。ADC采樣率為80 MHz,對信號進行帶通采樣,根據(jù)帶通采樣原理可設(shè)DDC的NCO頻率分別為12.58和26902 MHz。最大信號帶寬為4 MHz,所以可將下變頻信號進行16倍抽取,最后得到I、Q基帶信號以5 MHz的數(shù)據(jù)率輸出,DDC芯片ISL5416系統(tǒng)時鐘也設(shè)計為80 MHz,ISL5416有4個獨立的下變頻通道,分別取2個作為GPS和BD-2下變頻通道。ISL5416有4組信號輸入接口,但內(nèi)部交叉開關(guān)可以靈活配置輸入連接,所以為了方便硬件電路設(shè)計,只選用兩組接口分別接到2個ADC芯片的輸出,再通過芯片交叉開關(guān)配置將信號連接分配到4個DDC通道輸入信號接口。同時,ISL5416輸入接口為17位,為了連接14位ADC芯片AD6645的輸出,在硬件設(shè)計上,將ISL5416輸入口的低3位接地,高14位接ADC輸入。ISL5416關(guān)鍵部分電路原理圖如圖4所示。

參考ISL5416設(shè)計手冊根據(jù)系統(tǒng)指標,并結(jié)合系統(tǒng)設(shè)計要求,完成ISL5416各模塊的配置和設(shè)計如下:

2.2.1 輸入和輸出接口

ISL5416輸入時鐘:80MHz,時鐘輸入引腳CLKC;輸入數(shù)據(jù)格式為16位二進制補碼,定點;輸入模式為門控(GATED);NCO中心頻率為GP-S:12.58 MHz,BD-2:26.902 MHz;ISL5416的輸出接口為4組16位并行輸出接口,4個下變頻通道要同時輸出4組I、Q數(shù)據(jù)則需要8個16位輸出接口。因此采用分時復用輸出的方式,即在第1個時鐘輸出GPS基帶數(shù)據(jù),在第2個時鐘輸出BD-2基帶數(shù)據(jù)。接口數(shù)據(jù)率為10 MHz。

2.2.2 CIC濾波

CIC濾波器通帶寬度很窄,而且級數(shù)越高相對帶寬越窄。在相同相對帶寬下,級數(shù)越高混疊衰減越大。綜合考慮,在混疊衰減-100 dB的條件下,CIC配置如下:

1)GPS CIC級數(shù)為5,抽取因子4,輸入數(shù)據(jù)率80 MHz。通帶1.023 MHz,計算CIC濾波器的帶寬比例因子b為:

![]()

參見ISL5416數(shù)據(jù)手冊表可知CIC濾波器通帶衰減-0.257 dB,混疊衰減-119.749 dB。

2)BD一2,CIC級數(shù)為5,抽取因子4,輸入數(shù)據(jù)率80MHz,通帶2.046 MHz,參照式(1)計算CIC濾波器帶寬比例因子b為0.102 3,參見ISL5416數(shù)據(jù)手冊上的表可得帶寬比例因子為0.10時,通帶衰減-0.717 dB,混疊衰減-96.135 dB。

2.2.3 FIR1濾波器

FIR1有32抽頭,有20位可編程系數(shù),20位輸入數(shù)據(jù),24位輸出,每個時鐘計算4抽頭,如需使用全部32抽頭則每次計算共需8個時鐘。 FIR1的抽取數(shù)可以編程為1~8。

由于前級CIC濾波器抽取因子為4,F(xiàn)IR1每次計算只有4個時鐘周期,因此可以選擇將FIR1配置為16抽頭的FIR濾波器,抽取因子為2,輸出數(shù)據(jù)率為10 MHz。GPS和BD-2濾波器設(shè)計分別如下:

1)GPs輸入數(shù)據(jù)率20 MHz,通帶1.023MHz,截止頻率為6MHz,阻帶衰減80 dB,通帶波紋0.1dB,抽取因子為2,輸出數(shù)據(jù)率降為10MHz。

2)BD-2輸入數(shù)據(jù)率20 MHz,通帶2.046MHz,截止頻率為7MHz,阻帶衰減80dB,通帶波紋O.1dB,抽取因子為2,輸出數(shù)據(jù)率降為10MHz。

2.2.4 FIR2濾波器

FIR2有64抽頭,有20位可編程系數(shù),20位輸入數(shù)據(jù),24位輸出,每個時鐘計算8抽頭,如需使用全部64抽頭則每次計算共需8個時鐘。F-IR2的抽取數(shù)可以編程為1~8。由于CIC與FIR1總的抽取因子為8,因此可以使用全部64抽頭。GPS和BD-2濾波器設(shè)計分別如下:

1)GPS輸入數(shù)據(jù)率10MHz,通帶1.023MHz,截止頻率為1.6MHz,阻帶衰減80dB,通帶波紋0.1dB,抽取因子為2,輸出數(shù)據(jù)率降為5MHz。

2)BD-2輸入數(shù)據(jù)率10MHz,通帶2.046MHz,截止頻率為2.5MHz,阻帶衰減80dB,通帶波紋0.1dB,抽取因子為2,輸出數(shù)據(jù)率降為5MHz。

DDC下變頻通道,經(jīng)CIC、FIR1和FIR2級聯(lián)抽取濾波,3個濾波器級聯(lián)的總體頻率響應如圖5和6所示,從圖中可以看出帶外抑制在90 dBFS以下能夠滿足實際要求。

3 性能測試

本系統(tǒng)采用AD6645高速ADC采集數(shù)據(jù),并將數(shù)據(jù)輸入ISL5416。通過XILINX公司的XC5VLX110,百萬門級的FPGA接收DDC下變頻后數(shù)據(jù)。調(diào)試時,通過FPGA調(diào)試工具軟件ChipScope抓取FPGA內(nèi)ADC數(shù)據(jù)及ISL5416輸出的I、Q兩路數(shù)據(jù)。FPGA內(nèi)的DDC輸出I、Q數(shù)據(jù)如圖7所示。由圖可見,ISL5416正確地輸出了正交的I、Q兩路信號。

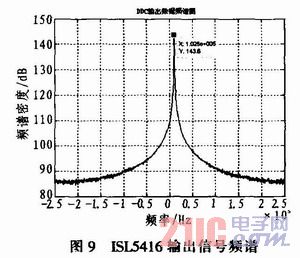

采用安捷倫信號發(fā)生器33250A產(chǎn)生67.52 MHz單頻正弦信號,在ADC采樣率為80 MHz時,采樣得到信號頻譜如圖8所示。信號經(jīng)ISL5416下變頻之后得到I、Q兩路數(shù)據(jù),I、Q兩路數(shù)據(jù)合成的復信號頻譜如圖9所示。

從以上兩圖可以看出,67.52 MHz單頻正弦經(jīng)80 MHz采樣,ISL5416按上文所述的配置工作,頻譜搬移67.42 MHz,輸出正交的I、Q兩路信號,I、Q兩路信號的頻率為100 kHz,實現(xiàn)了頻譜的搬移,阻帶抑制符合要求,ISL5416正常工作,實現(xiàn)數(shù)字下變頻。

4 結(jié) 論

本文根據(jù)工程項目需求,結(jié)合4通道專用DDC芯片可靈活配置的特性,合理設(shè)計,將接收機中ADC采樣后的多載波中頻信號,通過DDC通道下變頻得到GPS和BD-2的I、Q數(shù)字基帶數(shù)據(jù),以便后續(xù)的陣列信號處理及抗干擾算法研究。最終,使用8片DDC芯片ISL5416,實現(xiàn)了16陣元GP-S/BD-2接收機的DDC設(shè)計。由于此類接收機陣元數(shù)多,各通道結(jié)構(gòu)一致,采用專用DDC芯片節(jié)約成本,也避免了采用FPGA設(shè)計DDC時的重復設(shè)計。為軟件無線電在16陣元GPS/BD-2接收機的實現(xiàn)提供了解決方案,并具有較強的商用價值。