軟件無線電是近年來提出的一種新的無線通信體系結構。它最初起源于軍事通信,是以開放的、可擴展的、結構最簡的硬件為通用平臺,把盡可能多的功能用可升級、可替換的軟件來實現(xiàn)。軟件無線電的出現(xiàn)大大減小了硬件對通信系統(tǒng)的束縛,通過加載軟件就可以實現(xiàn)各種無線通信功能。

如何產(chǎn)生多種調制信號,一直是大家討論和關注的熱點。本文提出的方案就是基于超高速、先進DDS" title="DDS">DDS技術的數(shù)字中頻處理技術的方法,利用美AD公司推出的AD9954" title="AD9954">AD9954構建一個硬件平臺,結合相應的數(shù)字處理軟件和控制軟件,獲得多種調制信號。一方面由于體積變小,使用起來很方便,另一方面也大大降低了成本。

1 DDS的原理介紹

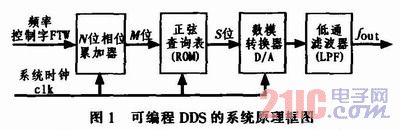

直接數(shù)字頻率合成器DDS是近年來發(fā)展起來的一種新的基于查找表的頻率合成技術。典型的DDS由相位累加器、ROM波形存儲表、D/A轉換器(Digital-to-AnalogConverter,DAC)和低通濾波器(LoW Passed Filter,LPF)組成,如圖1所示。

相位累加器由N位加法器與N位累加寄存器級聯(lián)構成。每來一個時鐘脈沖fs,加法器將頻率控制字FTW與累加寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的結果送至累加寄存器的數(shù)據(jù)輸入端。累加寄存器將加法器在上一個時鐘脈沖作用后所產(chǎn)生的新相位數(shù)據(jù)反饋到加法器的輸入端,使加法器在下一個時鐘脈沖的作用下繼續(xù)與頻率控制字相加。這樣,相位累加器在時鐘作用下,不斷對頻率控制字進行線性相位累加。由此可以看出,相位累加器在每一個時鐘脈沖輸入時,把頻率控制字累加1次,相位累加器輸出的數(shù)據(jù)就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號頻率。

用相位累加器輸出的數(shù)據(jù)作為波形存儲(ROM)的相位取樣地址,這樣就可把存儲在波形存儲器內的波形抽樣值(二進制編碼)經(jīng)查找表查出,完成相位到幅值轉換。波形存儲器的輸出送到D/A轉換器,D/A轉換器將數(shù)字量形式的波形幅值轉換成所要求合成頻率的模擬量形式信號。低通濾波器用于濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號。

若相位累加器的位數(shù)為N.改變頻率控制字FTW或參考時鐘fs,就可以改變輸出頻率fo:

![]()

DDS在相對帶寬、頻率轉換時間、高分辨率、相位連續(xù)性、正交輸出以及集成化等一系列性能指標方面遠遠超過了傳統(tǒng)頻率合成技術所能達到的水平,為系統(tǒng)提供了優(yōu)于模擬信號源的性能。

2 AD9954芯片的介紹

2.1 AD9954的主要性能特性

1)DDS采樣率可達400 MSPS;2)內置14位DAC;3)32位相位累加器;4)波特率達25 M的SPI接口;5)內置1 024x32位RAM,可實現(xiàn)內部調制;6)內部采用1.8 V供電,超低功耗;7)可自動線性和非線性掃頻。

2.2 AD9954的原理及工作過程

AD9954是采用先進的DDS技術開發(fā)的高集成度DDS器件。該芯片的速度是業(yè)界第一個時鐘達到400 MHz,合成技術高達160 MHz,功耗200 mW。以前產(chǎn)品的合成頻率只有120 MHz且功耗卻有2 W。它能使設計者采用DDS在功率敏感的應用中在更高頻率輸出進行快速跳頻。

AD9954作為新型DDS系列的旗艦產(chǎn)品,內置高速、高性能14位DAC,它內含1 024x32靜態(tài)RAM,可實現(xiàn)高速調制,并支持幾種快速掃頻模式和精細的調諧分辨率(32位頻率調諧字)。可提供自定義的線性掃頻操作模式,采用自動線性和非線性掃描功能來控制頻率調諧和相位,其中頻率調諧和控制字通過串行I/O口加載到AD9954,可實現(xiàn)多片同步。

3 系統(tǒng)設計原理框圖

多種調制信號平臺由TI的430單片機、Altera公司的FPGA、AD公司的AD9954、外圍的濾波和整形電路搭建而成。其中以AD9954為核心元器件來產(chǎn)生原始的所需波形,如圖2所示。

通過MCU控制FPGA的調制類型狀態(tài)和DDS調制芯片的寄存器數(shù)值,完成利用人機界面對整體電路的控制和配置過程。FPGA將A/D轉換過后的基帶信號通過確定的調制方式再經(jīng)相應的轉換送入DDS調制IC中。DDS的輸出信號經(jīng)功率放大后再進行輸出。

AD9954的串口與FPGA相連,F(xiàn)PGA通過AD9954的CS、SCLK、SDIO和SDO管腳向AD9954寫入數(shù)據(jù)和控制字。首先設置特定的寄存器控制字,允許RAM工作,接著將RAM輸出作為相位累加器的輸入給芯片提供頻率轉換字,然后寫好RAM段控制寄存器的值,定義起始地址、終止地址并選擇工作模式。例如,在RAM地址256~511中寫入計算好的頻率值,主要操作過程如下:

1)允許RAM操作,清除CFR<30>;2)選擇模式5即連續(xù)循環(huán)模式;3)選擇RAM段1,PS0=1,PS1=0;4)指令字節(jié)為00001001;5)定義通信階段的通信周期數(shù)為256,把數(shù)據(jù)寫入RAM存儲器地址256~511中:6)改變I/O UPDATE啟動模式工作。本系統(tǒng)可由地址的變化速率來計算調制速度,地址變化速率RAM段控制寄存器中的地址變化率控制字決定,其值的范圍是1~65 535,定義的時間是SYNC_CLK的周期數(shù)。由于SYNC_CLK最大為100 MHz,從而決定了地址變化率控制字為1時能定義的最快速度為100 MHz,假設一個波形要采集256個點,那么調制速度為100 MHz/256=400 kHz;如果采樣點為100個,則調制速度可達100 MHz/100=1 MHz。由于AD9954產(chǎn)生的調制波形采樣點多,采樣時間精確,因此波形性能較好。

4 輸出信號介紹及設置AD9954中的寄存器

4.1 正弦信號

正弦波信號廣泛地應用于通信系統(tǒng)中,它可以作為載波信號來進行數(shù)字系統(tǒng)的調制,這不僅僅是因為它容易產(chǎn)生,最主要的是它便于接收并且形式簡單。其數(shù)學表達式為:

![]()

平臺上的實現(xiàn):AD9954首先通過關閉RAM模式和線性掃頻模式來實現(xiàn)單頻模式,然后設置頻率字設置寄存器1來實現(xiàn)要獲得的頻率。它的頻率計算公式如下:

![]()

4.2 線性調頻信號

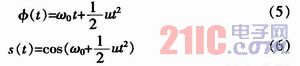

線性調頻信號是一種發(fā)射脈沖信號在信息脈沖持續(xù)時間T內作線性變化,其瞬時頻率隨時間線性變化。這種信號的產(chǎn)生可以由一個鋸齒波控制壓控振蕩器實現(xiàn),振蕩頻率隨鋸齒波而變化,因此脈沖信號的載頻從原來單一頻率展寬為一個頻帶。可以用以下表達式來說明這個過程:

![]()

式中ω0為載波頻率的初始值,u為一個常數(shù),因此線性調頻信號的瞬時相位聲φ(t)和線性調頻信號在信息脈沖持續(xù)時間T內的表達式s(t)分別為:

平臺上的實現(xiàn):在AD9954中通過設置控制寄存器CFR1的21位為1來實現(xiàn)這一功能,分別向兩個頻率字設置寄存器FTW1和FTW2寫入掃頻的起始頻率和結束頻率,指定頻差。對線性掃頻每次的步長通過線性掃頻控制字來設定,同時值得指出的是,可以選擇從低頻率到高頻率的掃頻,也可以選擇從高頻率到低頻率的掃頻。

4.3 FSK調制信號

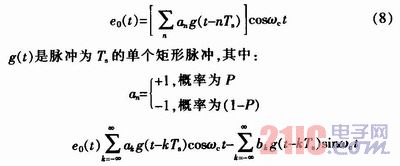

FSK信號也可以分為2FSK信號和多進制數(shù)字頻率調制。2FSK信號是由信息源符號1和0對應于不同的兩個載頻來實現(xiàn)調制的一種方式。其數(shù)學表達式為:

其中,g(t)為單個矩形脈沖,脈寬為Ts,

由于AD9954具有4個不同的RAM區(qū),因此也可以實現(xiàn)四進制的頻率調制,其實現(xiàn)方式與相位調制類似。

4.4 BPSK,QPSK調制信號

BPSK,QPSK信號是載波相位按照基帶脈沖而改變的一種數(shù)字調制方式。BPSK和QPSK信號的表達式分別為:

g(t)是脈沖為L的單個矩形脈沖,其中:ak=cosψk,bk=sinψk(ψk為受調相位)

在這里實現(xiàn)的只是絕對移相方式,對于BPSK而言,是按照1對應相位π,0對應相位0的方式來實現(xiàn)的;對于QPSK信號,則是由2 bit脈沖信號的4種不同狀態(tài)來選擇4種不同的相位,4種相位有2組形式,可選擇0,π/2,3π/2,7π/2和π/4,3π/4,5π/4,7π/4中的任意一組作為參考相位。

要實現(xiàn)上述調制信號,必須使AD9954工作在RAM模式下,通過設置控制寄存器CFR1的21位為0,同時配合外部片選信號PS0,PS1來實現(xiàn)4個RAM區(qū)的轉換。每個RAM區(qū)的首地址中存儲的是相位信息。在這種模式下,RAM中存儲的數(shù)據(jù)就會作為相位累加器的相位輸入。選擇不同的RAM區(qū),就會選擇不同的初始參考相位,從而達到相位調制的目的。

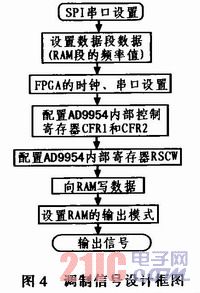

5 軟件系統(tǒng)設計

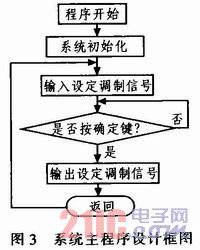

5.1 單片機編程

采用中斷的方式對AD9954寫入控制字,在每寫完一個控制字命令周期后,主機向AD9954發(fā)送一個更新信號,進入下一個控制命令字周期的寫入。在每寫完8 bit數(shù)據(jù)后就進行一次中斷,每中斷一次后設置標志位,等待下一次中斷。主程序根據(jù)鍵盤選擇調制方式,按確定后選擇需要的調制信號,流程圖如圖3所示。

5.2 FPGA的編程設計

首先利用FPGA制作1個ROM表,該表中存入的是一組相位信息或者頻率信息,然后通過時鐘的分頻及譯碼電路獲得信息表的地址,將對應地址的內容作為輸出,最后通過1個判決電路(二選一電路)來控制輸出模式。ROM表中的地址內容可以控制AD9954對實際相位值或實際頻率值的選擇。

由于FPGA的內部時鐘存在一定的不穩(wěn)定性,因此在這里選用外部穩(wěn)定的晶振作為輸入,一方面提供了穩(wěn)定的時鐘輸入,另一方面又可以減小FPGA內部寶貴資源的使用。

6 實驗輸出波形的時域和頻域分析圖

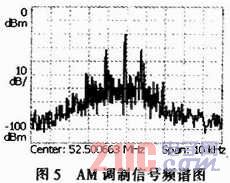

6.1 AM信號測試分析

AM系統(tǒng)頻域頻譜結構和時域解調波形測試結果分別如圖5、圖6所示。

AM載波頻率設置為52.5 MHz,實際測得的中心頻率為52.500 663 MHz,頻率誤差為0.000 663/52.5=1.263x10-5,誤差在系統(tǒng)規(guī)定的范圍內。

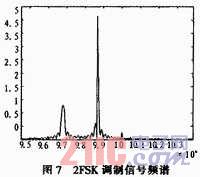

6.2 2FSK和4PSK信號測試分析

在該平臺下生成的FSK和QPSK頻譜如圖7、圖8所示。

2FSK信號是設置AD9954在Direct Switch模式下進行測試的,AD9954的系統(tǒng)時鐘為200 MHz,RAM0和RAM1設置的頻率值分別為9.7 MHz和9.9 MHz。設PS0=0,根據(jù)基帶信號0或1改變PS1的值為0或1即可產(chǎn)生2FSK信號。將2FSK信號波形數(shù)據(jù)采集并存儲后對其做FFT變換,畫出其頻譜圖如圖6所示,可見在9.69 MHz和9.88MHz有兩根譜線,證明采集到的為2FSK信號。

4PSK信號是設置AD9954在Direct Switch模式下進行測試的,AD9954的系統(tǒng)時鐘為200 MHz,RAM0、RAM1、RAM2和RAM3設置的頻率值分別為9.7 MHz、10.3 MHz、10MHz和10.9 MHz。根據(jù)基帶信號的0或1或2或3改變PS1和PS0的值即可產(chǎn)生4FSK信號。

7 結束語

本文介紹了采用先進DDS技術的AD9954性能特點和工作原理及過程,利用其可編程幅度、頻率、相位給出了AD9954在高速調制信號系統(tǒng)中的應用方案,從而較方便地實現(xiàn)基于軟件無線電技術的各種調制信號。采用超高速、先進DDS技術的數(shù)字中頻處理技術的方法,構建AD9954硬件實現(xiàn)平臺,結合相應的數(shù)字處理軟件和控制軟件,可獲得調幅、噪聲調頻、FSK、PSK等多種調制信號。本文提出的硬件實現(xiàn)方案,為產(chǎn)生多模式信號提供了硬件平臺,具有較好的應用價值。