第三代通用序列傳輸口(USB 3.0)承襲USB的便利性及多樣性,一舉將傳輸速度提升十倍,且保有對(duì)于現(xiàn)存USB裝置的向下兼容性,預(yù)期將迅速普及于個(gè)人電腦,消費(fèi)電子,通訊等各式應(yīng)用。現(xiàn)有的USB 2.0纜線及連接器提供了四條信號(hào)線,包含VBus 5V 500mA直流供電,一對(duì)DP/DM半雙工雙向差分信號(hào)線,以及GND接地,以此四條接線提供了USB 2.0的480Mbps的資料傳輸,及直流供電。USB 3.0為了提供高達(dá)5Gbps的資料傳輸率,額外增加五條訊號(hào)線,包括兩對(duì)單向傳輸?shù)某咚伲⊿uperSpeed)差分訊號(hào):SSTX+, SSTX-, SSRX+, SSRX-,及多一組的接地接點(diǎn),并將直流供電能力提升至5V 900mA。其中的兩對(duì)差分訊號(hào)分別負(fù)責(zé)傳輸及接收,提供雙向全雙工的5Gbps的傳輸能力。

圖1:USB 3.0連接器,后排的USB 3.0 SuperSpeed信號(hào)接點(diǎn)。

圖2:USB 3.0纜線示意圖,藍(lán)色部分為SuperSpeed 5Gbps信號(hào)。

SuperSpeed 5Gbps信號(hào)品質(zhì)的系統(tǒng)設(shè)計(jì)及量測(cè)挑戰(zhàn)

USB 3.0 SuperSpeed位傳輸率高達(dá)5Gbps,且采用開放式接口,信號(hào)品質(zhì)將直接影響裝置兼容性及傳輸效率,與使用者體驗(yàn)息息相關(guān)。主控芯片、印刷電路板、連接器、纜線甚至裝置端芯片組,都是影響信號(hào)品質(zhì)的關(guān)鍵。對(duì)于芯片廠商的類比傳輸設(shè)計(jì)能力,半導(dǎo)體制程變異,系統(tǒng)廠商的印刷電路設(shè)計(jì)布局都是全新的考驗(yàn)。不同于USB 2.0的經(jīng)驗(yàn),信號(hào)品質(zhì)的參考指標(biāo)將不再只是傳輸端的眼圖(Eye diagram)。USB 3.0獨(dú)立的傳輸及接收通道,系統(tǒng)接收能力也成為信號(hào)品質(zhì)及系統(tǒng)設(shè)計(jì)的重要量測(cè)指標(biāo)。接收端量測(cè)主要考驗(yàn)待測(cè)物對(duì)不同頻率的時(shí)基誤差容忍能力。容忍能力越強(qiáng)的芯片,代表其系統(tǒng)設(shè)計(jì)可較寬松,可使用較長(zhǎng)的信號(hào)走線,也有較佳的裝置兼容性。

圖3: USB 3.0 SuperSpeed傳輸端信號(hào)量測(cè)眼圖(Eye diagram)

圖4: USB 3.0接收量測(cè)結(jié)果。橫軸為時(shí)基誤差的頻率,縱軸為時(shí)基誤差的振幅。綠點(diǎn)表示位錯(cuò)誤率低于10-12的測(cè)試基準(zhǔn)點(diǎn)。黑線為測(cè)試基準(zhǔn)規(guī)范。

第三代通用序列傳輸口(USB 3.0)承襲USB的便利性及多樣性,一舉將傳輸速度提升十倍,且保有對(duì)于現(xiàn)存USB裝置的向下兼容性,預(yù)期將迅速普及于個(gè)人電腦,消費(fèi)電子,通訊等各式應(yīng)用。現(xiàn)有的USB 2.0纜線及連接器提供了四條信號(hào)線,包含VBus 5V 500mA直流供電,一對(duì)DP/DM半雙工雙向差分信號(hào)線,以及GND接地,以此四條接線提供了USB 2.0的480Mbps的資料傳輸,及直流供電。USB 3.0為了提供高達(dá)5Gbps的資料傳輸率,額外增加五條訊號(hào)線,包括兩對(duì)單向傳輸?shù)某咚伲⊿uperSpeed)差分訊號(hào):SSTX+, SSTX-, SSRX+, SSRX-,及多一組的接地接點(diǎn),并將直流供電能力提升至5V 900mA。其中的兩對(duì)差分訊號(hào)分別負(fù)責(zé)傳輸及接收,提供雙向全雙工的5Gbps的傳輸能力。

圖1:USB 3.0連接器,后排的USB 3.0 SuperSpeed信號(hào)接點(diǎn)。

圖2:USB 3.0纜線示意圖,藍(lán)色部分為SuperSpeed 5Gbps信號(hào)。

SuperSpeed 5Gbps信號(hào)品質(zhì)的系統(tǒng)設(shè)計(jì)及量測(cè)挑戰(zhàn)

USB 3.0 SuperSpeed位傳輸率高達(dá)5Gbps,且采用開放式接口,信號(hào)品質(zhì)將直接影響裝置兼容性及傳輸效率,與使用者體驗(yàn)息息相關(guān)。主控芯片、印刷電路板、連接器、纜線甚至裝置端芯片組,都是影響信號(hào)品質(zhì)的關(guān)鍵。對(duì)于芯片廠商的類比傳輸設(shè)計(jì)能力,半導(dǎo)體制程變異,系統(tǒng)廠商的印刷電路設(shè)計(jì)布局都是全新的考驗(yàn)。不同于USB 2.0的經(jīng)驗(yàn),信號(hào)品質(zhì)的參考指標(biāo)將不再只是傳輸端的眼圖(Eye diagram)。USB 3.0獨(dú)立的傳輸及接收通道,系統(tǒng)接收能力也成為信號(hào)品質(zhì)及系統(tǒng)設(shè)計(jì)的重要量測(cè)指標(biāo)。接收端量測(cè)主要考驗(yàn)待測(cè)物對(duì)不同頻率的時(shí)基誤差容忍能力。容忍能力越強(qiáng)的芯片,代表其系統(tǒng)設(shè)計(jì)可較寬松,可使用較長(zhǎng)的信號(hào)走線,也有較佳的裝置兼容性。

圖3: USB 3.0 SuperSpeed傳輸端信號(hào)量測(cè)眼圖(Eye diagram)

圖4: USB 3.0接收量測(cè)結(jié)果。橫軸為時(shí)基誤差的頻率,縱軸為時(shí)基誤差的振幅。綠點(diǎn)表示位錯(cuò)誤率低于10-12的測(cè)試基準(zhǔn)點(diǎn)。黑線為測(cè)試基準(zhǔn)規(guī)范。

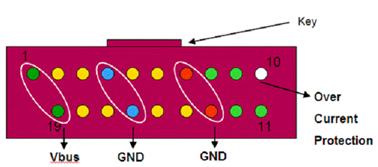

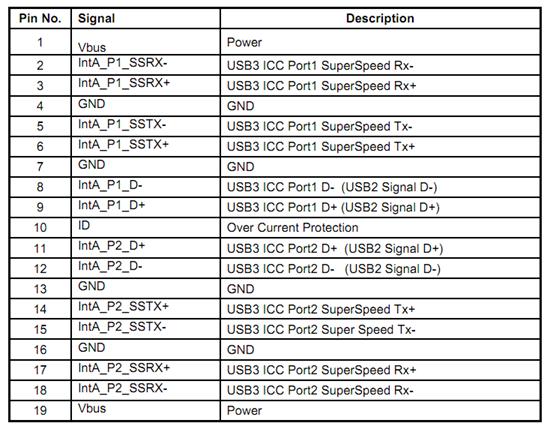

主機(jī)板及筆電的延伸設(shè)計(jì)

在USB 2.0相當(dāng)普遍的前端連接口,以內(nèi)連接的方式連接主機(jī)板及主機(jī)外箱,提供使用者方便順手的熱插拔應(yīng)用。USB 3.0連接口勢(shì)必也將導(dǎo)入前板連接口的設(shè)計(jì),額外的連接器及內(nèi)部連接線,對(duì)于信號(hào)品質(zhì)又是外加的考驗(yàn)。

圖5: USB 3.0內(nèi)部連接口針腳定義。

此外在筆電設(shè)計(jì)中,普遍使用軟排線連接不同的子板,以配合輕薄的外型及機(jī)構(gòu)設(shè)計(jì)。軟排線的阻抗控制,軟排線連接器的信號(hào)連續(xù)性,都不如印刷電路板及標(biāo)準(zhǔn)連接頭容易控制。這些都將是未來筆記型電腦中USB 3.0連接口的設(shè)計(jì)挑戰(zhàn)。如何在不使用信號(hào)調(diào)整器(re-driver)的額外成本下,導(dǎo)入前板及軟排線等系統(tǒng)設(shè)計(jì),又維持良好的5Gbps信號(hào)品質(zhì),成為重要的組件選擇關(guān)鍵。

圖6: USB 3.0內(nèi)部連接口及連接線

美商睿思科技的USB3.0主端控制芯片F(xiàn)L1009,因應(yīng)前述不同系統(tǒng)設(shè)計(jì)挑戰(zhàn),整合高效能類比實(shí)體設(shè)計(jì),完整驗(yàn)證不同系統(tǒng)設(shè)計(jì)需求。包含可容許長(zhǎng)達(dá)23公分(9英吋)的線路布局長(zhǎng)度,釋放系統(tǒng)設(shè)計(jì)在線路布局(layout)上的局限性,并允許長(zhǎng)至45公分的前板USB3.0額外接線,且不需額外re-driver的成本,使系統(tǒng)商與板卡商得以創(chuàng)造最高性能的產(chǎn)品,并有效減少設(shè)計(jì)時(shí)間與成本。除此之外,F(xiàn)L1009也是全球第一顆支持xHCI 1.0的SuperSpeed USB主控端芯片,提供超高效能及絕佳兼容性。