一、 引言

隨著計(jì)算機(jī)的廣泛使用,對(duì)輸出的VGA信號(hào)進(jìn)行實(shí)時(shí)監(jiān)控、存儲(chǔ)及傳輸?shù)膽?yīng)用需求越來越迫切。本文基于Ti公司的TMS320DM355處理器(簡(jiǎn)稱DM355)、AD公司的AD9883芯片,結(jié)合FPGA技術(shù),提出了一種支持分辨率較高、性能優(yōu)良的視頻信號(hào)采集和接口電路方案。

該系統(tǒng)對(duì)計(jì)算機(jī)輸出的XGA(1024x768)信號(hào)進(jìn)行實(shí)時(shí)采集、編碼、傳輸,同時(shí)利用ADV7123芯片將VGA信號(hào)還原,在本地的顯示器進(jìn)行輸出,主要應(yīng)用于視頻會(huì)議,視頻教學(xué)系統(tǒng)中。由于VGA信號(hào)的采集涉及到AD9883[1] [2]芯片和FPGA中信號(hào)時(shí)序的轉(zhuǎn)換,及DM355的視頻處理前端(VPFE:Video Processing Front End)驅(qū)動(dòng)的修改,比較復(fù)雜,本文將對(duì)此作重點(diǎn)闡述。

二、 系統(tǒng)整體設(shè)計(jì)

1. 方案選擇

本文采用TI公司的達(dá)芬奇系列芯片TMS320DM355來實(shí)現(xiàn),這一方案的優(yōu)點(diǎn)在于:

1)DM355內(nèi)部集成了ARM926EJ-S內(nèi)核、協(xié)處理器(MJCP)、視頻處理子系統(tǒng)及多種外設(shè)。ARM中移植嵌入式linux后可構(gòu)成一個(gè)良好的基于網(wǎng)絡(luò)的嵌入式產(chǎn)品開發(fā)平臺(tái),能方便的實(shí)現(xiàn)Web服務(wù)器的構(gòu)建和功能的擴(kuò)展。協(xié)處理器(MJCP)可實(shí)現(xiàn)對(duì)多媒體數(shù)據(jù)的編解碼。

2)DM355是一款低功耗的芯片,待機(jī)功耗僅為1mW,其電池的使用壽命是當(dāng)今業(yè)界相當(dāng)?shù)谋銛y式產(chǎn)品的2倍。

3)DM355是TI公司的一款中低檔芯片,在滿足性能要求的同時(shí),其價(jià)格與同類芯片相比也很有優(yōu)勢(shì)。因此,廣泛應(yīng)用于數(shù)碼相機(jī),IP攝像機(jī),數(shù)碼相片,醫(yī)學(xué)成像及視頻監(jiān)控系統(tǒng)中。

DM355的視頻處理子系統(tǒng)包括視頻處理前端(VPFE)和視頻處理后端(VPBE:Video Processing Back End),視頻處理前端[3]用于接收外部傳感器或視頻譯碼器等輸入的圖像信息,由CCD控制器、硬件圖像信號(hào)處理器、自動(dòng)曝光/聚焦模塊H3A和寄存器組成,支持的視頻輸入格式有如下三種:

1) RAW格式。

2) BT.656格式。

3) YUV格式。

其中,RAW格式對(duì)于每個(gè)像素點(diǎn)只存儲(chǔ)RGB三原色中某一種顏色的值,在進(jìn)行色彩還原時(shí)因插值運(yùn)算會(huì)導(dǎo)致莫爾紋效應(yīng);BT.656格式支持的視頻分辨率太低,因此,本系統(tǒng)的DM355處理器的視頻處理前端采用YUV格式進(jìn)行視頻采集,須將VGA信號(hào)通過硬件電路轉(zhuǎn)換為YUV信號(hào)格式。

2. 系統(tǒng)總體設(shè)計(jì)

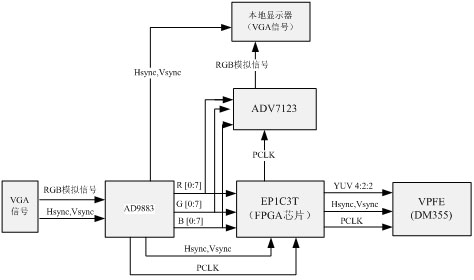

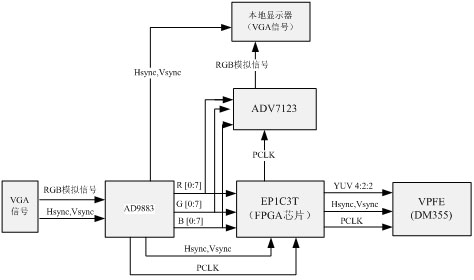

圖1所示為VGA視頻采集系統(tǒng)框圖。

圖1 VGA視頻采集系統(tǒng)框圖

1)VGA輸入模塊。將RGB模擬信號(hào)及行同步信號(hào)(Hsync)、場(chǎng)同步信號(hào)(Vsync)輸入給A/D轉(zhuǎn)換模塊。由于該模塊由模擬電路組成,易產(chǎn)生噪聲,因此布線時(shí)接口器件應(yīng)盡量靠近A/D轉(zhuǎn)換芯片。

2)A/D轉(zhuǎn)換模塊。首先根據(jù)行、場(chǎng)同步信號(hào)確定采樣的行頻和場(chǎng)頻,接著由行頻和內(nèi)部寄存器確定像素同步時(shí)鐘,然后通過配置AD9883芯片內(nèi)部的鎖相環(huán)(PLL)產(chǎn)生同步時(shí)鐘。該模塊可將輸入的VGA模擬信號(hào)轉(zhuǎn)換為8bit×3路的數(shù)字視頻信號(hào),并通過一系列寄存器調(diào)整圖像的采樣效果。

3) FPGA轉(zhuǎn)換控制模塊。一方面FPGA通過I2C總線向AD9883的寄存器寫入控制信息;另一方面將輸入的RGB信號(hào)轉(zhuǎn)換為DM355支持的YUV信號(hào)格式,將視頻信號(hào)送給DM355的視頻采集前端。

4)D/A輸出顯示模塊。該模塊采用ADV7123芯片將8bit×3路RGB數(shù)字信號(hào)還原為模擬信號(hào),并結(jié)合行、場(chǎng)同步信號(hào)構(gòu)成VGA信號(hào),供本地計(jì)算機(jī)顯示輸出。

三、 系統(tǒng)硬件設(shè)計(jì)

1.VGA接口

VGA是一種D型接口,可傳輸VGA,SVGA,XGA,SXGA等圖像格式。VGA接口共有15條線,分為3組:一是RGB三色模擬信號(hào)輸入線;二是RGB三色地線,接地處理;三是時(shí)序信號(hào)線,分別是行同步信號(hào)線(Horizon Synchronizing,HS)和場(chǎng)同步信號(hào)線(Vertical Synchronizing,VS),這兩條線控制了VGA的顯示時(shí)序。

顯示器采用逐行掃描的方式進(jìn)行掃描,陰極射線槍發(fā)出的電子束打在涂有熒光粉的屏幕上,產(chǎn)生RGB三基色,由此合成一個(gè)彩色圖像。VGA顯示可分為行掃描和場(chǎng)掃描,從屏幕左上方開始掃描,從左到右,由上至下。每行掃描結(jié)束時(shí),用行同步信號(hào)進(jìn)行行同步;當(dāng)整個(gè)屏幕的所有行掃描結(jié)束后,用場(chǎng)同步信號(hào)進(jìn)行場(chǎng)同步,如圖2所示。在掃描過程中,CRT對(duì)電子束進(jìn)行消隱控制,在消隱過程中不發(fā)送電子束。在每行結(jié)束后,電子槍回掃的過程進(jìn)行行消隱;在每場(chǎng)結(jié)束后,電子槍回掃的過程進(jìn)行場(chǎng)消隱,整個(gè)屏幕變黑,光柵在這段內(nèi)重新回到屏幕的左上角,開始下一幀圖像的掃描。

圖2 VGA掃描時(shí)序

2. A/D轉(zhuǎn)換模塊

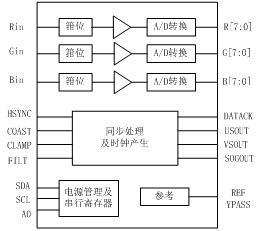

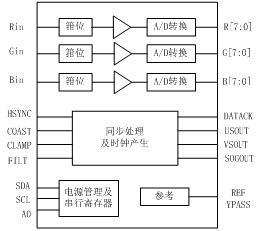

本系統(tǒng)的A/D轉(zhuǎn)換器采用AD9883,該芯片專門用于采集模擬R,G,B信號(hào),將其數(shù)字化顯示或作為中間轉(zhuǎn)換器件使用。該芯片具有采樣精度為8bit×3路通道,最高采樣率為140MSPS/s,300MB的模擬帶寬,支持最高分辨率為SXGA(1280x1024),刷新率為75Hz的視頻信號(hào)。基于AD9883的電路可為高清電視提供良好的接口,或作為高性能視頻設(shè)備的前端掃描轉(zhuǎn)換器,它的內(nèi)部結(jié)構(gòu)如圖3所示,主要包括A/D轉(zhuǎn)換電路、時(shí)鐘產(chǎn)生電路、同步信號(hào)產(chǎn)生電路、I2C總線接口四個(gè)部分。

圖3 AD9883的內(nèi)部結(jié)構(gòu)圖

AD9883內(nèi)部的寄存器通過I2C總線完全可編程,芯片按照寄存器設(shè)定的模式進(jìn)行工作。如AD9883支持多種VGA格式,但不能自動(dòng)檢測(cè)實(shí)現(xiàn)自適應(yīng),需要通過I2C接口進(jìn)行寄存器配置,指定芯片采集的視頻格式。

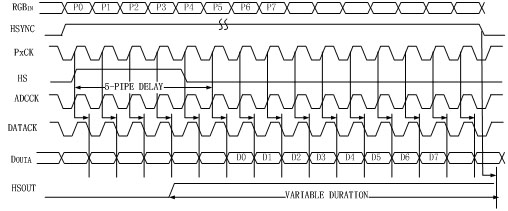

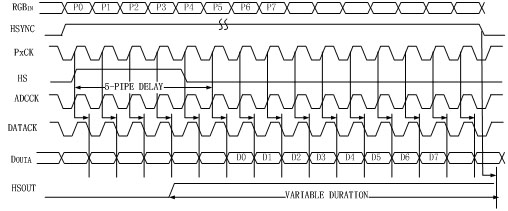

經(jīng)AD9883轉(zhuǎn)換后,數(shù)字視頻信號(hào)輸出的時(shí)序如圖4所示。在數(shù)據(jù)輸出時(shí)鐘DATACK的下降沿對(duì)應(yīng)信號(hào)的采樣及量化,量化的數(shù)據(jù)在時(shí)鐘上升沿穩(wěn)定的輸出;接口電路可在DATACK的上升沿準(zhǔn)確地鎖存圖像數(shù)據(jù),從而實(shí)現(xiàn)數(shù)字化圖像的采集。值得注意的是,AD9883有一個(gè)數(shù)據(jù)輸出通道,在輸出數(shù)據(jù)有效之前必須清空通道,從而導(dǎo)致每行輸出有效數(shù)據(jù)之前將輸出4組無效的數(shù)據(jù),可通過行同步信號(hào)HSOUT避免輸出這些無效數(shù)據(jù)。

圖4 AD9883數(shù)據(jù)輸出時(shí)序圖

一、 引言

隨著計(jì)算機(jī)的廣泛使用,對(duì)輸出的VGA信號(hào)進(jìn)行實(shí)時(shí)監(jiān)控、存儲(chǔ)及傳輸?shù)膽?yīng)用需求越來越迫切。本文基于Ti公司的TMS320DM355處理器(簡(jiǎn)稱DM355)、AD公司的AD9883芯片,結(jié)合FPGA技術(shù),提出了一種支持分辨率較高、性能優(yōu)良的視頻信號(hào)采集和接口電路方案。

該系統(tǒng)對(duì)計(jì)算機(jī)輸出的XGA(1024x768)信號(hào)進(jìn)行實(shí)時(shí)采集、編碼、傳輸,同時(shí)利用ADV7123芯片將VGA信號(hào)還原,在本地的顯示器進(jìn)行輸出,主要應(yīng)用于視頻會(huì)議,視頻教學(xué)系統(tǒng)中。由于VGA信號(hào)的采集涉及到AD9883[1] [2]芯片和FPGA中信號(hào)時(shí)序的轉(zhuǎn)換,及DM355的視頻處理前端(VPFE:Video Processing Front End)驅(qū)動(dòng)的修改,比較復(fù)雜,本文將對(duì)此作重點(diǎn)闡述。

二、 系統(tǒng)整體設(shè)計(jì)

1. 方案選擇

本文采用TI公司的達(dá)芬奇系列芯片TMS320DM355來實(shí)現(xiàn),這一方案的優(yōu)點(diǎn)在于:

1)DM355內(nèi)部集成了ARM926EJ-S內(nèi)核、協(xié)處理器(MJCP)、視頻處理子系統(tǒng)及多種外設(shè)。ARM中移植嵌入式linux后可構(gòu)成一個(gè)良好的基于網(wǎng)絡(luò)的嵌入式產(chǎn)品開發(fā)平臺(tái),能方便的實(shí)現(xiàn)Web服務(wù)器的構(gòu)建和功能的擴(kuò)展。協(xié)處理器(MJCP)可實(shí)現(xiàn)對(duì)多媒體數(shù)據(jù)的編解碼。

2)DM355是一款低功耗的芯片,待機(jī)功耗僅為1mW,其電池的使用壽命是當(dāng)今業(yè)界相當(dāng)?shù)谋銛y式產(chǎn)品的2倍。

3)DM355是TI公司的一款中低檔芯片,在滿足性能要求的同時(shí),其價(jià)格與同類芯片相比也很有優(yōu)勢(shì)。因此,廣泛應(yīng)用于數(shù)碼相機(jī),IP攝像機(jī),數(shù)碼相片,醫(yī)學(xué)成像及視頻監(jiān)控系統(tǒng)中。

DM355的視頻處理子系統(tǒng)包括視頻處理前端(VPFE)和視頻處理后端(VPBE:Video Processing Back End),視頻處理前端[3]用于接收外部傳感器或視頻譯碼器等輸入的圖像信息,由CCD控制器、硬件圖像信號(hào)處理器、自動(dòng)曝光/聚焦模塊H3A和寄存器組成,支持的視頻輸入格式有如下三種:

1) RAW格式。

2) BT.656格式。

3) YUV格式。

其中,RAW格式對(duì)于每個(gè)像素點(diǎn)只存儲(chǔ)RGB三原色中某一種顏色的值,在進(jìn)行色彩還原時(shí)因插值運(yùn)算會(huì)導(dǎo)致莫爾紋效應(yīng);BT.656格式支持的視頻分辨率太低,因此,本系統(tǒng)的DM355處理器的視頻處理前端采用YUV格式進(jìn)行視頻采集,須將VGA信號(hào)通過硬件電路轉(zhuǎn)換為YUV信號(hào)格式。

2. 系統(tǒng)總體設(shè)計(jì)

圖1所示為VGA視頻采集系統(tǒng)框圖。

圖1 VGA視頻采集系統(tǒng)框圖

1)VGA輸入模塊。將RGB模擬信號(hào)及行同步信號(hào)(Hsync)、場(chǎng)同步信號(hào)(Vsync)輸入給A/D轉(zhuǎn)換模塊。由于該模塊由模擬電路組成,易產(chǎn)生噪聲,因此布線時(shí)接口器件應(yīng)盡量靠近A/D轉(zhuǎn)換芯片。

2)A/D轉(zhuǎn)換模塊。首先根據(jù)行、場(chǎng)同步信號(hào)確定采樣的行頻和場(chǎng)頻,接著由行頻和內(nèi)部寄存器確定像素同步時(shí)鐘,然后通過配置AD9883芯片內(nèi)部的鎖相環(huán)(PLL)產(chǎn)生同步時(shí)鐘。該模塊可將輸入的VGA模擬信號(hào)轉(zhuǎn)換為8bit×3路的數(shù)字視頻信號(hào),并通過一系列寄存器調(diào)整圖像的采樣效果。

3) FPGA轉(zhuǎn)換控制模塊。一方面FPGA通過I2C總線向AD9883的寄存器寫入控制信息;另一方面將輸入的RGB信號(hào)轉(zhuǎn)換為DM355支持的YUV信號(hào)格式,將視頻信號(hào)送給DM355的視頻采集前端。

4)D/A輸出顯示模塊。該模塊采用ADV7123芯片將8bit×3路RGB數(shù)字信號(hào)還原為模擬信號(hào),并結(jié)合行、場(chǎng)同步信號(hào)構(gòu)成VGA信號(hào),供本地計(jì)算機(jī)顯示輸出。

三、 系統(tǒng)硬件設(shè)計(jì)

1.VGA接口

VGA是一種D型接口,可傳輸VGA,SVGA,XGA,SXGA等圖像格式。VGA接口共有15條線,分為3組:一是RGB三色模擬信號(hào)輸入線;二是RGB三色地線,接地處理;三是時(shí)序信號(hào)線,分別是行同步信號(hào)線(Horizon Synchronizing,HS)和場(chǎng)同步信號(hào)線(Vertical Synchronizing,VS),這兩條線控制了VGA的顯示時(shí)序。

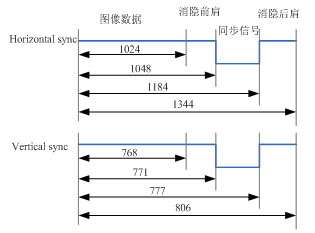

顯示器采用逐行掃描的方式進(jìn)行掃描,陰極射線槍發(fā)出的電子束打在涂有熒光粉的屏幕上,產(chǎn)生RGB三基色,由此合成一個(gè)彩色圖像。VGA顯示可分為行掃描和場(chǎng)掃描,從屏幕左上方開始掃描,從左到右,由上至下。每行掃描結(jié)束時(shí),用行同步信號(hào)進(jìn)行行同步;當(dāng)整個(gè)屏幕的所有行掃描結(jié)束后,用場(chǎng)同步信號(hào)進(jìn)行場(chǎng)同步,如圖2所示。在掃描過程中,CRT對(duì)電子束進(jìn)行消隱控制,在消隱過程中不發(fā)送電子束。在每行結(jié)束后,電子槍回掃的過程進(jìn)行行消隱;在每場(chǎng)結(jié)束后,電子槍回掃的過程進(jìn)行場(chǎng)消隱,整個(gè)屏幕變黑,光柵在這段內(nèi)重新回到屏幕的左上角,開始下一幀圖像的掃描。

圖2 VGA掃描時(shí)序

2. A/D轉(zhuǎn)換模塊

本系統(tǒng)的A/D轉(zhuǎn)換器采用AD9883,該芯片專門用于采集模擬R,G,B信號(hào),將其數(shù)字化顯示或作為中間轉(zhuǎn)換器件使用。該芯片具有采樣精度為8bit×3路通道,最高采樣率為140MSPS/s,300MB的模擬帶寬,支持最高分辨率為SXGA(1280x1024),刷新率為75Hz的視頻信號(hào)。基于AD9883的電路可為高清電視提供良好的接口,或作為高性能視頻設(shè)備的前端掃描轉(zhuǎn)換器,它的內(nèi)部結(jié)構(gòu)如圖3所示,主要包括A/D轉(zhuǎn)換電路、時(shí)鐘產(chǎn)生電路、同步信號(hào)產(chǎn)生電路、I2C總線接口四個(gè)部分。

圖3 AD9883的內(nèi)部結(jié)構(gòu)圖

AD9883內(nèi)部的寄存器通過I2C總線完全可編程,芯片按照寄存器設(shè)定的模式進(jìn)行工作。如AD9883支持多種VGA格式,但不能自動(dòng)檢測(cè)實(shí)現(xiàn)自適應(yīng),需要通過I2C接口進(jìn)行寄存器配置,指定芯片采集的視頻格式。

經(jīng)AD9883轉(zhuǎn)換后,數(shù)字視頻信號(hào)輸出的時(shí)序如圖4所示。在數(shù)據(jù)輸出時(shí)鐘DATACK的下降沿對(duì)應(yīng)信號(hào)的采樣及量化,量化的數(shù)據(jù)在時(shí)鐘上升沿穩(wěn)定的輸出;接口電路可在DATACK的上升沿準(zhǔn)確地鎖存圖像數(shù)據(jù),從而實(shí)現(xiàn)數(shù)字化圖像的采集。值得注意的是,AD9883有一個(gè)數(shù)據(jù)輸出通道,在輸出數(shù)據(jù)有效之前必須清空通道,從而導(dǎo)致每行輸出有效數(shù)據(jù)之前將輸出4組無效的數(shù)據(jù),可通過行同步信號(hào)HSOUT避免輸出這些無效數(shù)據(jù)。

圖4 AD9883數(shù)據(jù)輸出時(shí)序圖

3.FPGA設(shè)計(jì)

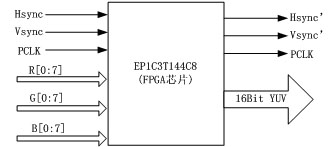

本系統(tǒng)采用EP1C3T144C8將輸入的數(shù)字化的RGB信號(hào)轉(zhuǎn)換為YUV信號(hào),送給DM355的視頻采集前端。FPGA以AD9883輸出的像素時(shí)鐘PCLK作為全局同步時(shí)鐘。

RGB和YUV是兩種常用的色彩空間。RGB色彩空間是采用R,G,B三個(gè)色彩分量來表示一個(gè)像素,常見的RGB格式有RGB565、RGB555、RGB24,本文中AD9883轉(zhuǎn)換輸出的數(shù)據(jù)格式為RGB24,即每個(gè)像素用24位表示,RGB分量各使用8位。

YUV色彩空間是視頻傳輸中常采用的一種方法,其特點(diǎn)為亮度信號(hào)與色差信號(hào)分離。Y表示亮度信息,U表示藍(lán)色色差(即藍(lán)色信號(hào)與亮度信號(hào)的差值),V表示紅色色差(即紅色信號(hào)與亮度信號(hào)的差值)。常見的YUV格式有YUV 4:4:4,YUV4:2:2,YUV4:2:0,本系統(tǒng)中DM355的視頻處理前端接收的采集信號(hào)格式為YUV4:2:2。該格式為每個(gè)像素保留Y分量,而UV分量在水平方向上每?jī)蓚€(gè)像素采樣一次,在圖像數(shù)據(jù)流中,YUV分量排列如下:Y0 U0 Y1 V0 Y2 U1 Y3 V1 Y4 U2 Y5 V2 … …

圖5所示為FPGA進(jìn)行色彩轉(zhuǎn)換的工作框圖,該模塊將輸入的8bit×3路RGB信號(hào)轉(zhuǎn)換為16bit的YUV信號(hào)。在YUV 16Bit的工作模式下,在一個(gè)時(shí)鐘周期內(nèi),高八位用于間隔傳遞U分量或V分量,低8位用于傳輸Y分量。

圖5 FPGA芯片色彩轉(zhuǎn)換框圖

除色彩空間的轉(zhuǎn)換外,F(xiàn)PGA模塊將像素同步時(shí)鐘及行、場(chǎng)同步信號(hào)送給A /D轉(zhuǎn)換模塊及DM355處理器,方便其他模塊進(jìn)行信號(hào)同步操作。

4.D/A輸出顯示設(shè)計(jì)

本設(shè)計(jì)采用ADV7123作為視頻轉(zhuǎn)換芯片,將數(shù)字視頻信號(hào)轉(zhuǎn)換為VGA模擬信號(hào),供本地計(jì)算機(jī)顯示輸出。ADV7123具有三路高速、10位輸入的視頻DA轉(zhuǎn)換器,具有330Mhz的最大采樣速度,與多種高精度的顯示系統(tǒng)兼容,可充分滿足本系統(tǒng)的轉(zhuǎn)換需求。當(dāng)RGB三通道的輸入比特?cái)?shù)少于10位時(shí),可將高位用于數(shù)據(jù)比特傳輸,低位接地處理。ADV7123芯片產(chǎn)生三路模擬輸出后,結(jié)合FPGA傳來的行、場(chǎng)同步信號(hào)完成視頻的顯示。

四、 系統(tǒng)軟件設(shè)計(jì)

1. FPGA軟件設(shè)計(jì)

FPGA[4]模塊的軟件設(shè)計(jì)主要實(shí)現(xiàn)以下3方面的功能:

1)I2C接口配置

在上一小節(jié)中提到,AD9883芯片內(nèi)部的寄存器通過I2C總線完全可編程,本小節(jié)將講述FPGA通過I2C接口對(duì)這些寄存器的具體配置。通過這些具體參數(shù)的配置,可實(shí)現(xiàn)對(duì)AD9883視頻采集格式、視頻轉(zhuǎn)換效果等的控制。

AD9883內(nèi)部共25個(gè)寄存器,其中00H和14H為只讀寄存器,15~18H為測(cè)試用寄存器,01H~13H為功能寄存器。FPGA芯片對(duì)主要功能寄存器的配置如表1所示:

表1 AD9883寄存器配置

|

功能 |

寄存器 |

配置值 |

|

鎖相環(huán)分頻控制 |

01H |

F0H |

|

時(shí)鐘產(chǎn)生器控制 |

03H |

70H |

|

04H |

80H |

|

|

箝位控制 |

05H |

09H |

|

增益和偏置控制 |

08H |

90H |

|

09H |

90H |

|

|

0aH |

90H |

|

|

0bH |

80H |

|

|

0cH |

80H |

|

|

0dH |

80H |

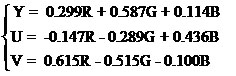

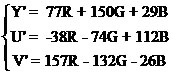

2)RGB與YUV的轉(zhuǎn)換

本系統(tǒng)中的FPGA模塊的另一功能是將RGB信號(hào)轉(zhuǎn)換為YUV信號(hào),二者轉(zhuǎn)換的公式為(RGB取值范圍均為0-255):

(式 1)

(式 1)

由于FPGA芯片進(jìn)行浮點(diǎn)運(yùn)算時(shí),運(yùn)算步驟繁瑣并且硬件資源消耗較大,故將式1中的參數(shù)均乘以256后取整,轉(zhuǎn)換如下:

(式2)

(式2)

經(jīng)過運(yùn)算后,得到式2中的Y’,U’,V’分量后,分別取數(shù)據(jù)的高八位即為Y,U,V分量的實(shí)際值。

3)VPFE接口時(shí)序的實(shí)現(xiàn)

由于AD9883芯片輸出的同步信號(hào)與DM355要求的輸入同步信號(hào)格式不匹配,因此需要將同步信號(hào)進(jìn)行轉(zhuǎn)換。AD9883芯片輸出的同步信號(hào)周期包括行消隱前肩、行消隱后肩、同步信號(hào)和圖像數(shù)據(jù)四個(gè)部分,而實(shí)際傳輸給DM355的視頻處理前端的信號(hào)僅包括同步信號(hào)和圖像數(shù)據(jù)兩個(gè)部分,因此需要對(duì)信號(hào)周期進(jìn)行轉(zhuǎn)換,如圖6所示。

圖6 VGA行、場(chǎng)同步時(shí)序示意圖

2.DM355軟件設(shè)計(jì)

1)視頻處理前端驅(qū)動(dòng)的修改

為了采集轉(zhuǎn)換后的YUV信號(hào),本文對(duì)DM355的視頻處理前端的驅(qū)動(dòng)進(jìn)行了修改,配置視頻采集設(shè)備的工作模式為YUV輸入模式。主要修改的驅(qū)動(dòng)文件為dm355_vpfe.c,部分代碼解析如下:

static vpfe_obj vpfe_device_ycbcr = {

……

.vwin = {0,0,1024,768},//VPFE_WIN_VGA,

.bounds = {0,0,1024,768},//VPFE_WIN_VGA,

//設(shè)置采集的YUV信號(hào)的分辨率

.pixelaspect = VPFE_PIXELASPECT_NTSC,

.pixelfmt = V4L2_PIX_FMT_UYVY,

.field = V4L2_FIELD_NONE,

//設(shè)置V4L2的工作模式為逐行掃描格式

……

.capture_device = TVP5146,

.ccdc_params_ycbcr = {

.pix_fmt = CCDC_PIXFMT_YCBCR_16BIT,

//采用16位數(shù)據(jù)總線傳輸YUV信號(hào)

……

.bt656_enable = FALSE,

//不采用BT.656采集模式

.pix_order = CCDC_PIXORDER_CBYCRY,

.buf_type = CCDC_BUFTYPE_FLD_SEPARATED

//該設(shè)置相對(duì)于CCDC_BUFTYPE_FLD_INTERLEAVED而言,設(shè)置buffer為獨(dú)立的

},

.tvp5146_params = {

.mode = TVP5146_MODE_AUTO,

.amuxmode = TVP5146_AMUX_COMPOSITE,

.enablebt656sync = FALSE,

//不采用BT.656同步模式

.data_width = TVP5146_WIDTH_16BIT

//數(shù)據(jù)總線寬度為16bit

},

.irqlock = SPIN_LOCK_UNLOCKED

};

2)視頻信號(hào)采集程序設(shè)計(jì)

在DM355的應(yīng)用程序設(shè)計(jì)中,視音頻數(shù)據(jù)的采集、編碼、輸出分別通過Capture Thread,Video Thread, Writer Thread獨(dú)立線程來實(shí)現(xiàn)。其中,視頻采集線程的主要作用是對(duì)采集設(shè)備進(jìn)行初始化,開辟緩沖區(qū),以幀為單位往其中寫入數(shù)據(jù),為Video Thread做準(zhǔn)備。

視頻采集程序通過調(diào)用V4L2[5](Video For Linux 2)來實(shí)現(xiàn),V4L2是Linux中提供的關(guān)于視頻設(shè)備的內(nèi)核驅(qū)動(dòng),它為針對(duì)視頻設(shè)備的應(yīng)用程序變成提供一系列的接口函數(shù),如VIDIOC_REQBUFS,分配內(nèi)存;VIDIOC_QUERYBUF,將VIDIOC_REQBUFS中分配的數(shù)據(jù)緩存轉(zhuǎn)換成物理地址;VIDIOC_QUERYCAP,查詢采集設(shè)備功能;VIDIOC_S_FMT,設(shè)置當(dāng)前驅(qū)動(dòng)的視頻捕獲格式;VIDIOC_STREAMON,開始視頻采集等。

圖7采集設(shè)備初始化流程圖

圖7為視頻采集線程對(duì)采集設(shè)備進(jìn)行初始化的流程圖。在Linux中,視頻采集設(shè)備的設(shè)備文件名為/dev/video0,可通過函數(shù)open(“/dev/video0”, O_RDWR | O_NONBLOCK, 0)來打開視頻設(shè)備。打開設(shè)備文件后,利用ioctl函數(shù),設(shè)置不同的V4L2參數(shù),來調(diào)用底層的V4L2驅(qū)動(dòng)程序,獲取視頻采集設(shè)備的參數(shù),根據(jù)實(shí)際應(yīng)用需求設(shè)置視頻格式,同時(shí)為采集設(shè)備分配幀緩沖區(qū), 并將該緩沖區(qū)映射到用戶空間。這樣,當(dāng)緩沖區(qū)中存儲(chǔ)了一幀視頻數(shù)據(jù)后,VIDIOC_DQBUF就把數(shù)據(jù)從緩沖區(qū)中讀取出來,VIDIOC_DQBUF把數(shù)據(jù)放入視頻數(shù)據(jù)緩存隊(duì)列繼續(xù)下一幀的采集。當(dāng)接收到結(jié)束采集命令時(shí),通過ioctl函數(shù)發(fā)送VIDIOC_STREAMOFF命令,停止視頻采集。

五、系統(tǒng)測(cè)試和結(jié)束語

本系統(tǒng)對(duì)VGA信號(hào)采集成功后,利用MPEG4算法進(jìn)行編碼,并利用開源的JRTP庫實(shí)現(xiàn)網(wǎng)絡(luò)傳輸功能,客戶端可實(shí)時(shí)觀看和存儲(chǔ)接收到的碼流。在進(jìn)行VGA信號(hào)采集編碼的同時(shí),可利用ADV7123芯片將VGA信號(hào)還原,在本地的顯示器進(jìn)行輸出。經(jīng)過實(shí)驗(yàn)測(cè)試,本系統(tǒng)具有較好的實(shí)時(shí)性,解碼后的圖像主觀質(zhì)量也很好。

本文提出的基于TMS320DM355處理器,采用AD9883和ADV7123轉(zhuǎn)換芯片,結(jié)合FPGA技術(shù)的VGA信號(hào)采集方案,能夠?qū)GA信號(hào)進(jìn)行實(shí)時(shí)采集。該系統(tǒng)可廣泛應(yīng)用于雷達(dá)、天氣預(yù)報(bào)、航空航天、通信等領(lǐng)域的圖像數(shù)據(jù)實(shí)時(shí)記錄。

【參考文獻(xiàn)】

[1] Analog Devices.AD9883A/AD9883A Data sheet[EB/OL].2007. http://www.analog.com/static /imported- files/data_sheets/ AD9883A.pdf.

[2] 胡建民,郭太良,林志賢。 AD9883 在平板顯示視頻接口中的應(yīng)用[J]。現(xiàn)代電子技術(shù), 2007(2):25-27.

[3] Texas Instruments Incorporated. TMS320DM35x digital media system-on-chip video processing front end (VPFE) RG spruf71a[EB/OL]。[2009-08-10]。 http://focus.ti.com/lit/ug /spruf71a/spruf71a.pdf 。

[4] 朱文偉,許忠仁,基于FPGA 的V GA 圖像控制器的設(shè)計(jì)與實(shí)現(xiàn)[J ] 。 貴州大學(xué)學(xué)報(bào):自然科學(xué)版,2009 ,30 (2) :109- 111.

[5] SCHIMEK Michael H,DIRKS Bill,VERKUIL Hans,et al. Video for Linux Two API specification [EB/OL]。 [2009-10-20].http://www.soezblog.com/plate/web/bookmarkmsg.jsp?UI =cherng64&CI =368&p =1&BI=199102.