經(jīng)過近幾年的快速發(fā)展,嵌入式系統(tǒng)(Embedded system)已經(jīng)成為電子信息產(chǎn)業(yè)中最具增長力的一個分支。隨著手機、PDA、GPS、機頂盒等新興產(chǎn)品的大量應(yīng)用,嵌入式系統(tǒng)的市場正在以每年30%的速度遞增(IDC預(yù)測),嵌入式系統(tǒng)的設(shè)計也成為軟硬件工程師越來越關(guān)心的話題。

在嵌入式系統(tǒng)的設(shè)計中,低功耗設(shè)計(Low-Power Design)是許多設(shè)計人員必須面對的問題,其原因在于嵌入式系統(tǒng)被廣泛應(yīng)用于便攜式和移動性較強的產(chǎn)品中去,而這些產(chǎn)品不是一直都有充足的電源供應(yīng),往往是靠電池來供電,所以設(shè)計人員從每一個細節(jié)來考慮降低功率消耗,從而盡可能地延長電池使用時間。事實上,從全局來考慮低功耗設(shè)計已經(jīng)成為了一個越來越迫切的問題。

那么,我們應(yīng)該從哪些方面來考慮低功耗設(shè)計呢?筆者認為應(yīng)從以下幾方面綜合考慮:

處理器的選擇

接口驅(qū)動電路設(shè)計

動態(tài)電源管理

電源供給電路的選擇

下面我們分別進行討論:

一、處理器的選擇

我們對一個嵌入式系統(tǒng)的選型往往是從其CPU和操作系統(tǒng)(OS)開始的,一旦這兩者選定,整個大的系統(tǒng)框架便選定了。我們在選擇一個CPU的時候,一般更注意其性能的優(yōu)劣(比如時鐘頻率等)及所提供的接口和功能的多少,往往忽視其功耗特性。但是因為CPU是嵌入式系統(tǒng)功率消耗的主要來源---對于手持設(shè)備來講,它幾乎占據(jù)了除顯示屏以外的整個系統(tǒng)功

耗的一半以上(視系統(tǒng)具體情況而定),所以選擇合適的CPU對于最后的系統(tǒng)功耗大小有舉足輕重的影響。

一般的情況下,我們是在CPU的性能(Performance)和功耗(Power Consumption)方面進行比較和選擇。通常可以采用每執(zhí)行1M次指令所消耗的能量來進行衡量,即Watt/MIPS。但是,這僅僅是一個參考指標(biāo),實際上各個CPU的體系結(jié)構(gòu)相差很大,衡量性能的方式也不盡相同,所以,我們還應(yīng)該進一步分析一些細節(jié)。

我們把CPU的功率消耗分為兩大部分:內(nèi)核消耗功率PCORE和外部接口控制器消耗功率PI/O,總的功率等于兩者之和,即P=PCORE+PI/O。對于PCORE,關(guān)鍵在于其供電電壓和時鐘頻率的高低;對于PI/O來講,除了留意各個專門I/O控制器的功耗外,還必須關(guān)注地址和數(shù)據(jù)總線寬度。下面對兩者分別進行討論:

1、CPU供電電壓和時鐘頻率

我們知道,在數(shù)字集成電路設(shè)計中,CMOS電路的靜態(tài)功耗很低,與其動態(tài)功耗相比基本可以忽略不計,故暫不考慮。其動態(tài)功耗計算公式為:

Pd=CTV2f

式中,Pd---CMOS芯片的動態(tài)功耗

CT----CMOS芯片的負載電容

V----CMOS芯片的工作電壓

f-----CMOS芯片的工作頻率

由上式可知,CMOS電路中的功率消耗是與電路的開關(guān)頻率呈線性關(guān)系,與供電電壓呈二次平方關(guān)系。對于一顆CPU來講,Vcore電壓越高,時鐘頻率越快,則功率消耗越大。所以,在能夠滿足功能正常的前提下,盡可能選擇低電壓工作的CPU能夠在總體功耗方面得到較好的效果。對于已經(jīng)選定的CPU來講,降低供電電壓和工作頻率,也是一條節(jié)省功率的可行之路。

2、總線寬度

我們還經(jīng)常陷入一個誤區(qū),即:CPU外部總線寬度越寬越好。如果我們僅僅從數(shù)據(jù)傳輸速度上來講,也許這個觀點是對的,但如果在一個對功耗相當(dāng)敏感的設(shè)計來說,這個觀點就不一定正確了。

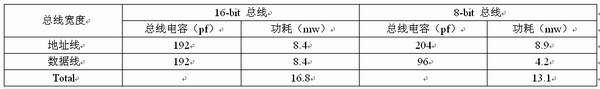

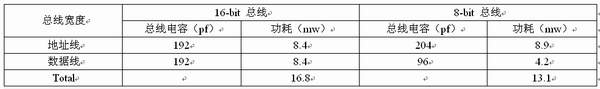

同樣引用公式Pd=CTV2f ,對于每一條線(地址等數(shù)據(jù)線)而言,都會面臨這樣的功率消耗,顯而易見,當(dāng)總線寬度越寬的時候,功耗自然越大。每條線路的容性負載都不太一樣,但一般都在4~12PF之間。我們來看下面一個例子:一片1Mbit Flash通過8bit和16bit的

總線與CPU相連,總線頻率為4MHZ ,總線電壓為3.3V。我們可以得到以下結(jié)果:

由上可見,采用16-bit總線和采用8-bit總線會有3.7mw的功耗差異。

當(dāng)然,如果需要大量頻繁地存取數(shù)據(jù)的場合下,用8-bit總線不見得會經(jīng)濟,因為增加了讀寫周期。

另外,從上面的例子我們也可以看到:如果CPU采用內(nèi)置Flash的方式,也可大大地降低系統(tǒng)功率消耗。

二、接口驅(qū)動電路的低功耗設(shè)計

接口電路的低功耗設(shè)計,往往是容易被大家所忽略的一個環(huán)節(jié),在這個環(huán)節(jié)里,我們除了考慮選用靜態(tài)電流較低的外圍芯片外,還應(yīng)該考慮以下幾個因素:

上拉電阻/下拉電阻的選取

對懸空腳的處理

Buffer的必要性

通常我們習(xí)慣隨意地確定一個上拉電阻值,而沒有經(jīng)過仔細地計算。現(xiàn)在我們來簡單計算一下,如果在一個3.3V的系統(tǒng)里用4.7KΩ為上拉電阻,當(dāng)輸出為低的時候,每只腳上的電流消耗就為0.7mA,如果有10個這樣的信號腳時,就會有7mA電流消耗在這上面。所以我們應(yīng)該在考慮在能夠正常驅(qū)動后級的情況下(即考慮IC的VIH或VIL),盡可能選取更大的阻值。現(xiàn)在很多應(yīng)用設(shè)計中的上拉電阻值甚至高達幾百KΩ。另外,當(dāng)一個信號在多數(shù)情況下時為低的時候,我們也可以考慮用下拉電阻以節(jié)省功率。

CMOS器件的懸空腳也應(yīng)該引起我們的重視。因為CMOS懸空的輸入端的輸入阻抗極高,很可能感應(yīng)一些電荷導(dǎo)致器件被高壓擊穿,而且還會導(dǎo)致輸入端信號電平隨機變化,導(dǎo)致CPU在休眠時不斷地被喚醒,從而無法進入休眠狀態(tài)或其他莫名其妙的故障,所以正確的方法是將未使用到的輸入端接到VCC或地。

Buffer有很多功能,如電平轉(zhuǎn)換,增加驅(qū)動能力,數(shù)據(jù)傳輸?shù)姆较蚩刂频鹊龋绻麅H僅基于驅(qū)動能力的考慮增加Buffer的話,我們就應(yīng)該慎重考慮了,因為過驅(qū)動會導(dǎo)致更多的能量被白白浪費掉。所以我們應(yīng)該仔細檢查芯片的最大輸出電流IOH和IOL是否足以驅(qū)動下級IC,如果可以通過選取合適的前后級芯片來避免Buffer的使用,對于能量來講是一個很大的節(jié)約。

三、動態(tài)電源管理(DPM)

所謂動態(tài)的電源管理就是在系統(tǒng)運行期間通過對系統(tǒng)的時鐘或電壓的動態(tài)控制來達到節(jié)省功率的目的,這種動態(tài)控制是與系統(tǒng)的運行狀態(tài)密切相關(guān)的,這個工作往往通過軟件來實現(xiàn)。

1、選取不同工作模式

如前所述,系統(tǒng)時鐘對于功耗大小有非常明顯的影響。所以我們除了著重于滿足性能的需求外,還必須考慮如何動態(tài)地設(shè)置時鐘來達到功率的最大程度節(jié)約。CPU內(nèi)部的各種頻率都是通過外部晶振頻率經(jīng)由內(nèi)部鎖相環(huán)(PLL)倍頻式后產(chǎn)生的。于是,是否可以通過內(nèi)部寄存器設(shè)置各種工作頻率的高低成為控制功耗的一個關(guān)鍵因素。現(xiàn)在很多CPU都有多種工作模式,我們可以通過控制CPU進入不同的模式來達到省電的目的。

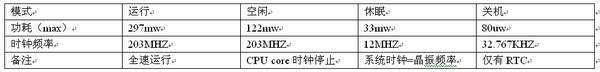

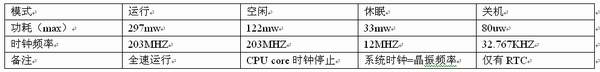

我們以SAMSUNG S3C2410X (32bit ARM 920T內(nèi)核)為例,它提供了四種工作模式:正常模式、空閑模式、休眠模式、關(guān)機模式,各種模式的功耗如下:

由上圖可見,CPU在全速運行的時候比在空閑或者休眠的時候消耗的功率大得多。省電的原則就是讓正常運行模式遠比空閑、休眠模式少占用時間。在類似PDA的設(shè)備中,系統(tǒng)在全速運行的時候遠比空閑的時候少,所以我們可以通過設(shè)置使CPU盡可能工作在空閑狀態(tài),然后通過相應(yīng)的中斷喚醒CPU,恢復(fù)到正常工作模式,處理響應(yīng)的事件,然后再進入空閑模式。

經(jīng)過近幾年的快速發(fā)展,嵌入式系統(tǒng)(Embedded system)已經(jīng)成為電子信息產(chǎn)業(yè)中最具增長力的一個分支。隨著手機、PDA、GPS、機頂盒等新興產(chǎn)品的大量應(yīng)用,嵌入式系統(tǒng)的市場正在以每年30%的速度遞增(IDC預(yù)測),嵌入式系統(tǒng)的設(shè)計也成為軟硬件工程師越來越關(guān)心的話題。

在嵌入式系統(tǒng)的設(shè)計中,低功耗設(shè)計(Low-Power Design)是許多設(shè)計人員必須面對的問題,其原因在于嵌入式系統(tǒng)被廣泛應(yīng)用于便攜式和移動性較強的產(chǎn)品中去,而這些產(chǎn)品不是一直都有充足的電源供應(yīng),往往是靠電池來供電,所以設(shè)計人員從每一個細節(jié)來考慮降低功率消耗,從而盡可能地延長電池使用時間。事實上,從全局來考慮低功耗設(shè)計已經(jīng)成為了一個越來越迫切的問題。

那么,我們應(yīng)該從哪些方面來考慮低功耗設(shè)計呢?筆者認為應(yīng)從以下幾方面綜合考慮:

處理器的選擇

接口驅(qū)動電路設(shè)計

動態(tài)電源管理

電源供給電路的選擇

下面我們分別進行討論:

一、處理器的選擇

我們對一個嵌入式系統(tǒng)的選型往往是從其CPU和操作系統(tǒng)(OS)開始的,一旦這兩者選定,整個大的系統(tǒng)框架便選定了。我們在選擇一個CPU的時候,一般更注意其性能的優(yōu)劣(比如時鐘頻率等)及所提供的接口和功能的多少,往往忽視其功耗特性。但是因為CPU是嵌入式系統(tǒng)功率消耗的主要來源---對于手持設(shè)備來講,它幾乎占據(jù)了除顯示屏以外的整個系統(tǒng)功

耗的一半以上(視系統(tǒng)具體情況而定),所以選擇合適的CPU對于最后的系統(tǒng)功耗大小有舉足輕重的影響。

一般的情況下,我們是在CPU的性能(Performance)和功耗(Power Consumption)方面進行比較和選擇。通常可以采用每執(zhí)行1M次指令所消耗的能量來進行衡量,即Watt/MIPS。但是,這僅僅是一個參考指標(biāo),實際上各個CPU的體系結(jié)構(gòu)相差很大,衡量性能的方式也不盡相同,所以,我們還應(yīng)該進一步分析一些細節(jié)。

我們把CPU的功率消耗分為兩大部分:內(nèi)核消耗功率PCORE和外部接口控制器消耗功率PI/O,總的功率等于兩者之和,即P=PCORE+PI/O。對于PCORE,關(guān)鍵在于其供電電壓和時鐘頻率的高低;對于PI/O來講,除了留意各個專門I/O控制器的功耗外,還必須關(guān)注地址和數(shù)據(jù)總線寬度。下面對兩者分別進行討論:

1、CPU供電電壓和時鐘頻率

我們知道,在數(shù)字集成電路設(shè)計中,CMOS電路的靜態(tài)功耗很低,與其動態(tài)功耗相比基本可以忽略不計,故暫不考慮。其動態(tài)功耗計算公式為:

Pd=CTV2f

式中,Pd---CMOS芯片的動態(tài)功耗

CT----CMOS芯片的負載電容

V----CMOS芯片的工作電壓

f-----CMOS芯片的工作頻率

由上式可知,CMOS電路中的功率消耗是與電路的開關(guān)頻率呈線性關(guān)系,與供電電壓呈二次平方關(guān)系。對于一顆CPU來講,Vcore電壓越高,時鐘頻率越快,則功率消耗越大。所以,在能夠滿足功能正常的前提下,盡可能選擇低電壓工作的CPU能夠在總體功耗方面得到較好的效果。對于已經(jīng)選定的CPU來講,降低供電電壓和工作頻率,也是一條節(jié)省功率的可行之路。

2、總線寬度

我們還經(jīng)常陷入一個誤區(qū),即:CPU外部總線寬度越寬越好。如果我們僅僅從數(shù)據(jù)傳輸速度上來講,也許這個觀點是對的,但如果在一個對功耗相當(dāng)敏感的設(shè)計來說,這個觀點就不一定正確了。

同樣引用公式Pd=CTV2f ,對于每一條線(地址等數(shù)據(jù)線)而言,都會面臨這樣的功率消耗,顯而易見,當(dāng)總線寬度越寬的時候,功耗自然越大。每條線路的容性負載都不太一樣,但一般都在4~12PF之間。我們來看下面一個例子:一片1Mbit Flash通過8bit和16bit的

總線與CPU相連,總線頻率為4MHZ ,總線電壓為3.3V。我們可以得到以下結(jié)果:

由上可見,采用16-bit總線和采用8-bit總線會有3.7mw的功耗差異。

當(dāng)然,如果需要大量頻繁地存取數(shù)據(jù)的場合下,用8-bit總線不見得會經(jīng)濟,因為增加了讀寫周期。

另外,從上面的例子我們也可以看到:如果CPU采用內(nèi)置Flash的方式,也可大大地降低系統(tǒng)功率消耗。

二、接口驅(qū)動電路的低功耗設(shè)計

接口電路的低功耗設(shè)計,往往是容易被大家所忽略的一個環(huán)節(jié),在這個環(huán)節(jié)里,我們除了考慮選用靜態(tài)電流較低的外圍芯片外,還應(yīng)該考慮以下幾個因素:

上拉電阻/下拉電阻的選取

對懸空腳的處理

Buffer的必要性

通常我們習(xí)慣隨意地確定一個上拉電阻值,而沒有經(jīng)過仔細地計算。現(xiàn)在我們來簡單計算一下,如果在一個3.3V的系統(tǒng)里用4.7KΩ為上拉電阻,當(dāng)輸出為低的時候,每只腳上的電流消耗就為0.7mA,如果有10個這樣的信號腳時,就會有7mA電流消耗在這上面。所以我們應(yīng)該在考慮在能夠正常驅(qū)動后級的情況下(即考慮IC的VIH或VIL),盡可能選取更大的阻值。現(xiàn)在很多應(yīng)用設(shè)計中的上拉電阻值甚至高達幾百KΩ。另外,當(dāng)一個信號在多數(shù)情況下時為低的時候,我們也可以考慮用下拉電阻以節(jié)省功率。

CMOS器件的懸空腳也應(yīng)該引起我們的重視。因為CMOS懸空的輸入端的輸入阻抗極高,很可能感應(yīng)一些電荷導(dǎo)致器件被高壓擊穿,而且還會導(dǎo)致輸入端信號電平隨機變化,導(dǎo)致CPU在休眠時不斷地被喚醒,從而無法進入休眠狀態(tài)或其他莫名其妙的故障,所以正確的方法是將未使用到的輸入端接到VCC或地。

Buffer有很多功能,如電平轉(zhuǎn)換,增加驅(qū)動能力,數(shù)據(jù)傳輸?shù)姆较蚩刂频鹊龋绻麅H僅基于驅(qū)動能力的考慮增加Buffer的話,我們就應(yīng)該慎重考慮了,因為過驅(qū)動會導(dǎo)致更多的能量被白白浪費掉。所以我們應(yīng)該仔細檢查芯片的最大輸出電流IOH和IOL是否足以驅(qū)動下級IC,如果可以通過選取合適的前后級芯片來避免Buffer的使用,對于能量來講是一個很大的節(jié)約。

三、動態(tài)電源管理(DPM)

所謂動態(tài)的電源管理就是在系統(tǒng)運行期間通過對系統(tǒng)的時鐘或電壓的動態(tài)控制來達到節(jié)省功率的目的,這種動態(tài)控制是與系統(tǒng)的運行狀態(tài)密切相關(guān)的,這個工作往往通過軟件來實現(xiàn)。

1、選取不同工作模式

如前所述,系統(tǒng)時鐘對于功耗大小有非常明顯的影響。所以我們除了著重于滿足性能的需求外,還必須考慮如何動態(tài)地設(shè)置時鐘來達到功率的最大程度節(jié)約。CPU內(nèi)部的各種頻率都是通過外部晶振頻率經(jīng)由內(nèi)部鎖相環(huán)(PLL)倍頻式后產(chǎn)生的。于是,是否可以通過內(nèi)部寄存器設(shè)置各種工作頻率的高低成為控制功耗的一個關(guān)鍵因素。現(xiàn)在很多CPU都有多種工作模式,我們可以通過控制CPU進入不同的模式來達到省電的目的。

我們以SAMSUNG S3C2410X (32bit ARM 920T內(nèi)核)為例,它提供了四種工作模式:正常模式、空閑模式、休眠模式、關(guān)機模式,各種模式的功耗如下:

由上圖可見,CPU在全速運行的時候比在空閑或者休眠的時候消耗的功率大得多。省電的原則就是讓正常運行模式遠比空閑、休眠模式少占用時間。在類似PDA的設(shè)備中,系統(tǒng)在全速運行的時候遠比空閑的時候少,所以我們可以通過設(shè)置使CPU盡可能工作在空閑狀態(tài),然后通過相應(yīng)的中斷喚醒CPU,恢復(fù)到正常工作模式,處理響應(yīng)的事件,然后再進入空閑模式。