記得大概在6 年前,隨便翻閱一本計(jì)算機(jī)相關(guān)雜志,看到一則硬盤的廣告,什么品牌記不得了,印象最深的就是它所宣傳的新技術(shù)- 串行總線。當(dāng)時我還沒有接觸高速數(shù)字電路方面的知識,腦子里還是傳統(tǒng)的教科書式的關(guān)于數(shù)字電路的概念:串行,或是異步串行總線,無外乎RS232 、RS485 等。居然串行構(gòu)架的傳輸效率高過于并行的系統(tǒng),簡直無法想象。回頭看看這幾年市場熱點(diǎn)和技術(shù)革新,在對照自己第一次接觸“串行”時的愕然,不禁莞爾。

這篇小文章就是自己對關(guān)于高速串行數(shù)字電路設(shè)計(jì)、測試的知識體系的一個梳理。特別是在加入Tektronix 之后,負(fù)責(zé)HSSD (High Speed Serial data )測試產(chǎn)品的支持,從日常接觸的客戶中,了解到很多具體的應(yīng)用和實(shí)例,在一定程度上講,Tektronix 就像小蜜蜂一樣,在不同的客戶中間,傳播著HSSD 設(shè)計(jì)、測試的理念和經(jīng)驗(yàn)。這篇小東西包含了涉及HSSD 各個方面的內(nèi)容,有談到基本的原理、測試的方法、時下比較流行的技術(shù),以及常見的故障信號以及解決方案。希望這篇小東西能在日常繁瑣的工作之余,作為一盤“小甜點(diǎn)”,給大家?guī)韮?nèi)心那一份久違的、輕松愉悅的微笑。

一、高速串行總線基本知識

并行總線之所以在高速傳輸上被串行總線取代的原因就在于:第一,系統(tǒng)時鐘的瓶頸;第二,總線間的串?dāng)_。要達(dá)到上Gbps的傳輸速率,對于并行總線而言,勢必時鐘頻率要達(dá)到GHz,就算是使用DDR方式,其系統(tǒng)時鐘頻率之高,在板級分布之困難,使得我們望而卻步。而動輒幾十條走線等長的排布,可控的串?dāng)_,幾乎也是不可能完成的任務(wù),而不斷增加的時鐘頻率,又對等長走線要求越來越嚴(yán)格,并行總線的瓶頸似乎變得非常的突出。

串行總線沒有時鐘。或是說在串行總線收發(fā)兩端,不需要同步時鐘。這是串行總線最突出的一個特點(diǎn)。這是這個特點(diǎn),一舉將并行構(gòu)架的瓶頸打破,數(shù)據(jù)速率可謂突飛猛進(jìn)!最新在PC行業(yè)的動向是8Gbps的PCIE Gen3。而在通信行業(yè),超過10Gbps的串行總線早已在使用了。

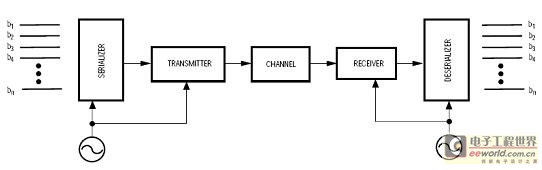

對于高速串行系統(tǒng)的驗(yàn)證與測試和傳統(tǒng)的信號測試有自己特殊的之處,傳統(tǒng)信號測試關(guān)心信號的模擬特征,包括時序和幅度方面特性的考察。對于并行總線而言,時序的方面的測量最主要以建立/保持時間為主,為了滿足接收端能否正確的鎖存數(shù)據(jù),數(shù)據(jù)和時鐘的時序必須滿足建立/保持時間的要求,否則會產(chǎn)生誤碼。對于高速串行系統(tǒng)而言,測試的目的也是為了驗(yàn)證系統(tǒng)是否滿足設(shè)計(jì)要求的誤碼水平。并行和串行的差別就在于發(fā)送端和接收端對數(shù)據(jù)鎖存的處理和時鐘的傳輸上的差異。串行系統(tǒng)在發(fā)送斷通過串行發(fā)送器將數(shù)據(jù)按照Tx clk的節(jié)拍發(fā)送到總線上,在接收端必須能夠從數(shù)據(jù)中恢復(fù)出時鐘,并且用該時鐘鎖存數(shù)據(jù),進(jìn)行解碼。在串行系統(tǒng)中,我們不再關(guān)心時鐘和數(shù)據(jù)信號之間的時序,而是關(guān)心在發(fā)送端是否能否嚴(yán)格按照時鐘節(jié)拍發(fā)送數(shù)據(jù);在接收端能否恢復(fù)出時鐘;在互連層面關(guān)心傳輸線對信號完整性,特別是抖動的影響。

圖表 1典型的串行系統(tǒng)

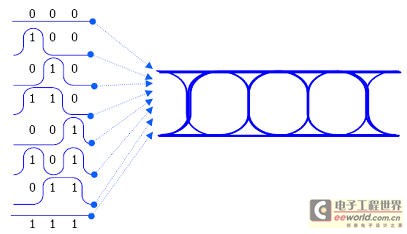

那么如何去定量串行系統(tǒng)的性能呢?在高速串行系統(tǒng)中,主要通過眼圖測試。眼圖是把連續(xù)的比特流按照某一特定的時鐘,分割為單獨(dú)的比特,而后疊加而形成的圖形,類似一個張開的眼睛,故得名眼圖(Eye-diagram)。

圖表 2眼圖的形成

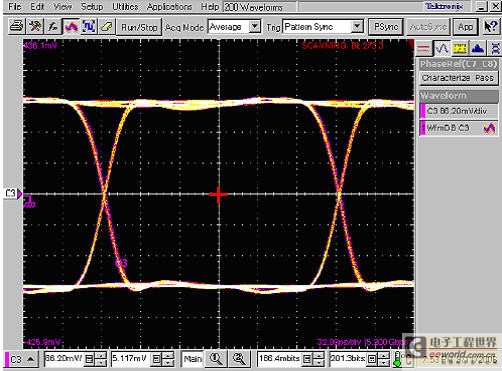

眼圖是高速串行信號的宏觀的信號質(zhì)量的體現(xiàn),在眼圖中能直接反映出信號串行信號的幅度(如眼高、過沖、噪聲等)和時序(如上升/下降時間、UI長度、眼寬、抖動等)特性。在接收端,理想的時鐘判決應(yīng)該發(fā)生在整個眼圖的中間,這樣才能保證系統(tǒng)有最好的誤碼特性。

圖表 3理想的采樣時刻-中間的紅色十字

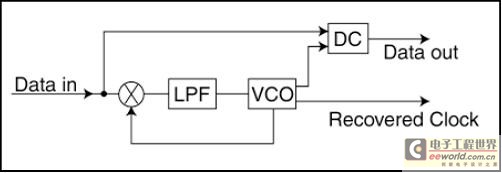

接收端是如何恢復(fù)出嵌入在串行數(shù)據(jù)中的時鐘呢?是通過接收端的時鐘數(shù)據(jù)恢復(fù)(CDR)來完成的。CDR的實(shí)現(xiàn)可以有很多中方式,通常使用鎖相環(huán)(PLL)或者鑒相器(PI)來完成。PLL類型的CDR通過數(shù)據(jù)中0-1的跳變來鎖定時鐘相位和頻率,在一定的范圍內(nèi)能夠跟蹤數(shù)據(jù)信號的抖動,以保持時鐘和數(shù)據(jù)相位的一致,而后通過判決電路(DC)得到數(shù)據(jù)。PLL類型的CDR要求數(shù)據(jù)中有足夠多的0-1跳變,而且數(shù)據(jù)必須是直流平衡的,因此在數(shù)據(jù)進(jìn)入到串行發(fā)送器之前,會通過8B/10B編碼,使得數(shù)據(jù)有足夠多的跳變,并且保證一段數(shù)據(jù)流中0和1的個數(shù)相同。

圖表 4 PLL類型的CDR電路

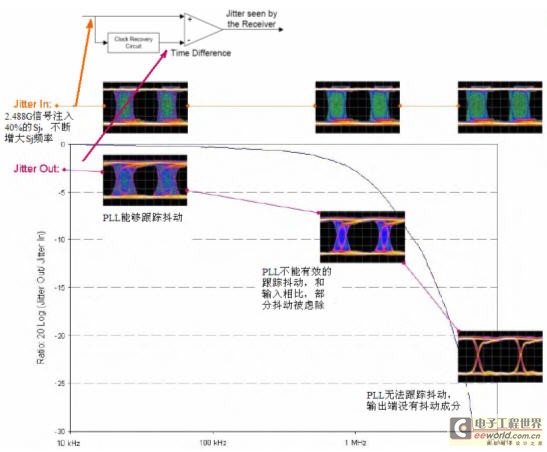

CDR的目的很明確,跟蹤數(shù)據(jù)抖動的變化(產(chǎn)生和數(shù)據(jù)同步的抖動),保證在DC中不會出現(xiàn)誤碼。CDR對數(shù)據(jù)的跟蹤也不是萬能的,如果數(shù)據(jù)中的抖動頻率超過了PLL的環(huán)路帶寬,那么PLL是無法跟蹤的,數(shù)據(jù)抖動就會傳遞到DC中,可能會影響到數(shù)據(jù)的提取而產(chǎn)生誤碼。所以CDR的時鐘恢復(fù)是有范圍的,這個范圍是有PLL的環(huán)路帶寬決定的。在環(huán)路帶寬能的抖動成分能被跟蹤,而超出帶寬的抖動是真正影響到誤碼率性能的抖動,我們所要考察的串行系統(tǒng)的抖動,就是那些不能被PLL跟蹤的抖動!所以,在眼圖測試中,必須要給定CDR的類型,否則盲目的測試眼圖和抖動是沒有任何意義的。

圖表 5抖動測試目的是發(fā)現(xiàn)在接收端無法被跟蹤的抖動

明確的眼圖測試的目的和注意事項(xiàng)后,我們就可以根據(jù)被測系統(tǒng)規(guī)劃合適的測試方案:

- 通過系統(tǒng)的串行速率選擇合適帶寬的示波器

- 根據(jù)串行系統(tǒng)的誤碼標(biāo)準(zhǔn),制定眼圖模板

- 設(shè)計(jì)測試使用的CDR模型,正確模擬接收端的抖動情況

- 選擇合適的測試項(xiàng)目,明確測試目的是以驗(yàn)證為主還是調(diào)試為主

在測試工具的選擇上,工程師并不是只有實(shí)時示波器一種選擇。能夠進(jìn)行高速串行系統(tǒng)功能驗(yàn)證和調(diào)試的工具大致有:實(shí)時示波器(Real Time Oscilloscope)、采樣示波器(Sampling Oscilloscope)、時間間隔分析儀(Time Interval Analyzer)、誤碼儀(Bit Error Rate Tester)。按照測試精度、調(diào)試能力、效率以及成本作為考察項(xiàng)目,將上述幾種測試設(shè)備做簡單的對比:

| 測試精度 | 調(diào)試能力 | 效率 | 成本 | |

|---|---|---|---|---|

| 實(shí)時示波器 | 中 | 強(qiáng) | 高 | 低 |

| 采樣示波器 | 高 | 中 | 高 | 低 |

| 時間間隔分析儀 | 高 | 無 | 中 | 高 |

| 誤碼儀 | 高 | 無 | 低 | 高 |

圖表 6各種測試儀器對比

在測試精度方面,采樣示波器較實(shí)時示波器占有一定優(yōu)勢,時基精度可達(dá)200fs,垂直14bitADC,動態(tài)范圍大,自身噪底低(具體指標(biāo)請參見文檔2)。因此采樣示波器除了分析抖動外,同時還可以分析噪聲對串行系統(tǒng)誤碼的影響。但是采樣示波器采必須需要外觸發(fā),只能觀察周期性、重復(fù)的波形,不具備實(shí)時示波器靈活的觸發(fā)功能,因此在調(diào)試能力方面,實(shí)時示波器是其中最強(qiáng)大的。例如Tektronix DSA系列示波器中的串行觸發(fā),可以觸發(fā)到數(shù)據(jù)流中特定的比特碼型;碼型鎖定功能可以很容易的瀏覽碼型中所有比特;硬件CDR能夠快速的同步數(shù)據(jù),進(jìn)行眼圖、抖動分析。而誤碼儀是專用的誤碼測試設(shè)備,其測試精度是最高的。誤碼儀是一個閉環(huán)的系統(tǒng),通過對比發(fā)送和接收到的數(shù)據(jù)來計(jì)算誤碼。但是誤碼儀測試的效率很低,如果要測試置信概率為95%的誤碼率小于1E-12的話,要至少保證在連續(xù)的3E+12個比特中沒有誤碼。如果該串行速據(jù)的速度為1Gbps,那么3E+12個比特意味著要測試3000秒才能得到結(jié)果,而且這是最樂觀的估算。時間間隔分析儀是專用的測試時間間隔的儀器,時間測試精度高,但是設(shè)備本身帶寬有效,100MHz帶寬的時間價格分析儀非常的昂貴。因此,綜合比較下來,實(shí)時示波器的綜合能力在所有抖動分析測試工具里面是最強(qiáng)的。